FPGA时序约束:如何查看具体错误的时序路径

可编程逻辑

描述

1、时序错误的影响

一个设计的时序报告中,design run 时序有红色,裕量(slack)为负数时,表示时序约束出现违例,虽然个别违例不代表你的工程就有致命的问题,但是这是一个风险(时序报告是按照工艺、电压以及温度的上下限给出的结果)。当违例数较多,也就意味着设计在实际环境中出现问题的概率也会越大。 时间裕量包括建立时间裕量和保持时间裕量(setup slack和hold slack)。从字面上理解,所谓“裕量”即富余的、多出的。什么意思呢?即保持最低要求的建立时间或保持时间所多出的时间,那么“裕量”越多,意味着时序约束越宽松。

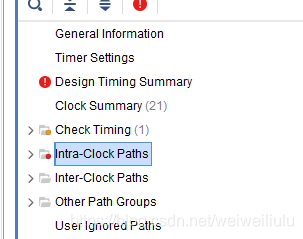

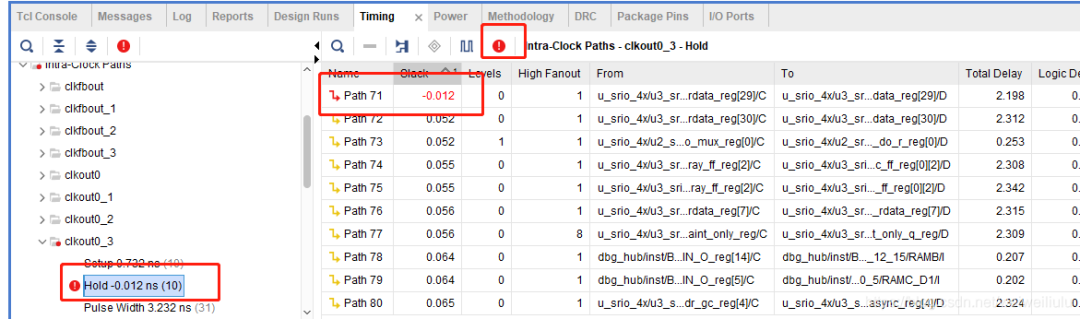

2、如何查看具体错误的时序路径

上述错误的时序,双击可以看到详细的时钟路径和数据路径,右键可以看到具体代码中的原理图。个人比较喜欢先查看原理图可以很直观的看到到底是哪一块的代码错了。 在调试的过程中发现,基本上时序错误都是代码的错误,比如没有跨时钟操作(跨时钟需要打两拍,跨时钟一些信号前后初始化不一致);数据路径过长(主要是针对位宽较大的数据,路径又长。解决办法是在该路径上添加寄存器)。出现时序错误,先从代码逻辑上找问题,代码逻辑排查完了,在考虑时序怎么约束。

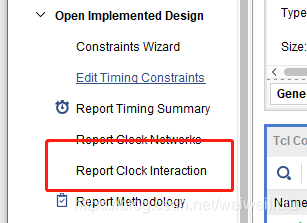

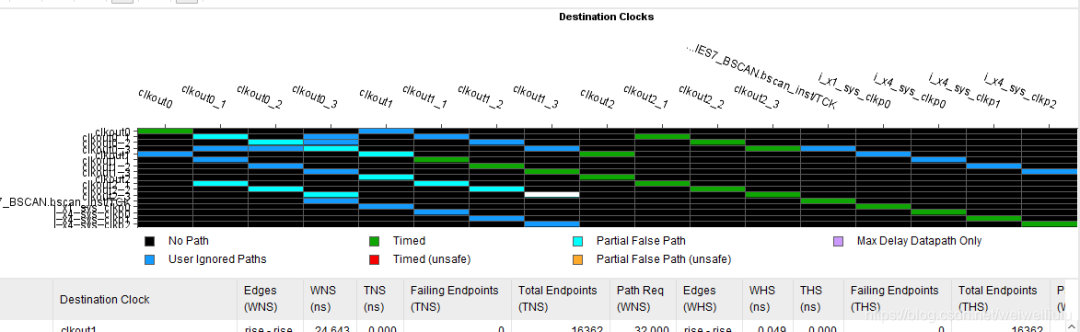

3、clock interaction 时序错误还可以通过下图查看,以前特别爱用里面的指令 set false path 和 set clock groups。自从意识到大部分的时序错误都是逻辑错误导致以后,基本没用到这两句话。有一次盲目的使用set false path 指令,没有对 set false path 的用法有深刻理解, 导致代码逻辑不正常后,就更不会轻易用这些优化指令了。 扩展: 1)set_false_path 设置伪路径后,不再对特殊路径进行时序分析。特殊路径如测试逻辑、添加同步电路后的跨时钟域路径等。在两个时钟域之间应该相互设置为set_false:(注意:只是不对特殊路径进行时序分析,而不是只要出现错误就能用这句话) set_false_path -from [get_clocks clk_a] -to [get_clocks clk_b] set_false_path -from [get_clocks clk_b] -to [get_clocks clk_a] 2)set_clock_groups :添加完以后事这样的 set_clock_groups -asynchronous -group clk_a -group clk_b clk_a和clk_b是异步时钟 设置异步时钟

编辑:黄飞

-

FPGA时序约束之设置时钟组2025-04-23 1620

-

FPGA时序约束之时序路径和时序模型2023-08-14 1697

-

详解时序路径的相关概念2023-06-26 2169

-

FPGA时序约束之衍生时钟约束和时钟分组约束2023-06-12 4491

-

FPGA时序约束:如何查看具体错误的时序路径2023-03-17 2278

-

FPGA的IO口时序约束分析2022-09-27 2530

-

FPGA时序约束一如何查看具体错误的时序路径2022-08-04 1159

-

FPGA的时序input delay约束2022-07-25 3978

-

FPGA设计之时序约束2022-03-18 2350

-

FPGA案例之时序路径与时序模型解析2020-11-17 3950

-

深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果2017-11-24 6114

-

FPGA中的时序约束设计2017-11-17 3091

-

FPGA时序约束方法2015-12-14 1005

全部0条评论

快来发表一下你的评论吧 !