使用STM32缓存来优化性能与功率效率

描述

来源:STM32单片机

本应用笔记描述了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)。

在 Arm Cortex-M33 处理器的 AHB 总线中引入的 ICACHE 和 DCACHE 嵌入到下表中列出的 STM32 微控制器(MCU)中。

这些缓存使用户从内部和外部存储器提取指令和数据时或在用于外部存储器的数据流量时提高应用性能并降低功耗。本文档提供了典型示例,以强调 ICACHE 和 DCACHE 功能,并便于配置。

1. ICACHE 和 DCACHE 概述

本节概述了嵌入在基于 STM32 Arm Cortex内核的微控制器中的 ICACHE 和 DCACHE 接口。详细介绍了 ICACHE 和 DCACHE 框图架构以及在系统架构中的集成。

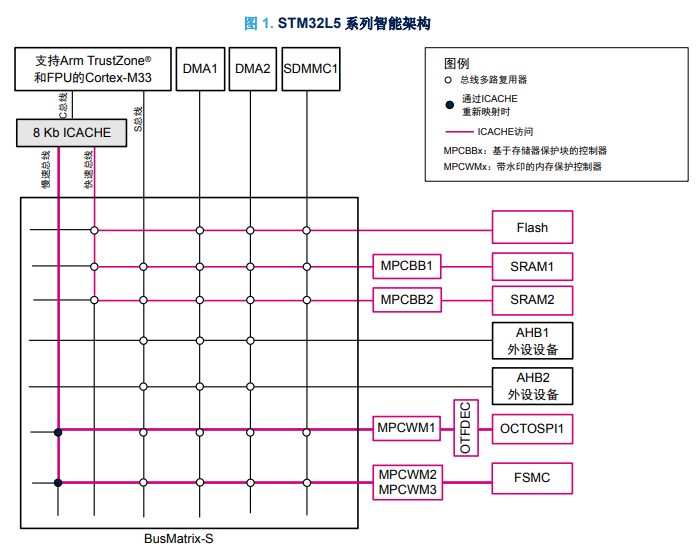

1.1 STM32L5 系列智能架构

此架构基于总线矩阵,允许多个主设备(Cortex-M33、DMA1/2 和 SDMMC1)访问多个从设备(如Flash 存储器、SRAM1/2、OCTOSPI1 或 FSMC)。

下图描述了 STM32L5 系列智能架构。

由于将 8-Kb 的 ICACHE 接口引入其 C-AHB 总线,通过快速总线从内部存储器(Flash 存储器、SRAM1 或SRAM2)或通过慢速总线从外部存储器(OCTOSPI1 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。

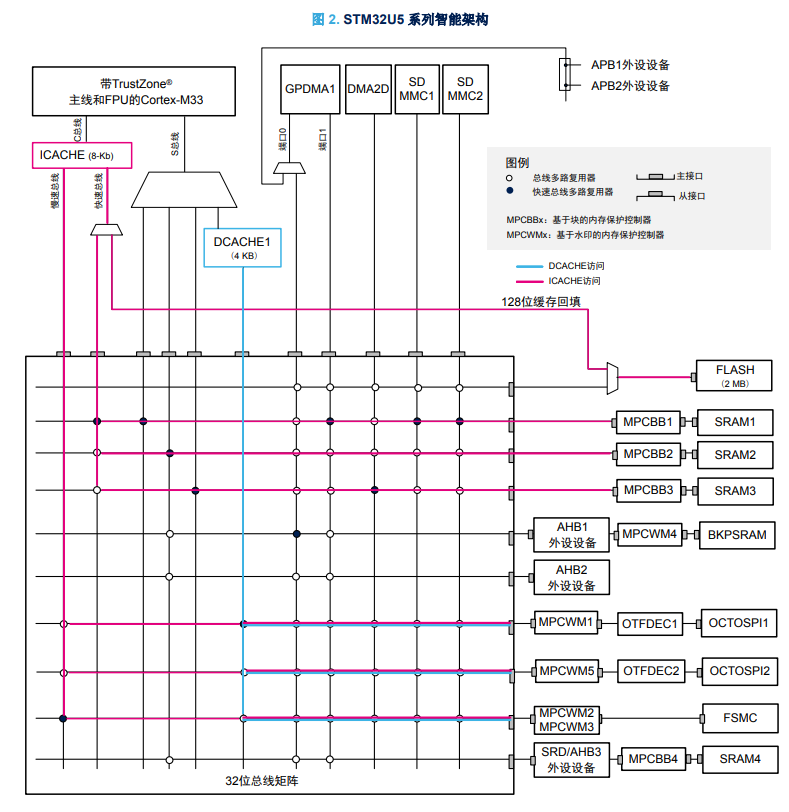

1.2 STM32U5 系列智能架构

此架构基于总线矩阵,允许多个主设备(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)访问多个从设备(如 Flash 存储器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。

下图描述了 STM32U5 系列智能架构。

其 C-AHB 总线引入了 8-Kb 的 ICACHE 接口,通过快速总线从内部存储器(Flash 存储器、SRAM1、SRAM2 或SRAM3)或通过慢速总线从外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。其 S-AHB 总线引入了 4-Kb 的 DCACHE 接口,提高了外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)的数据流量。

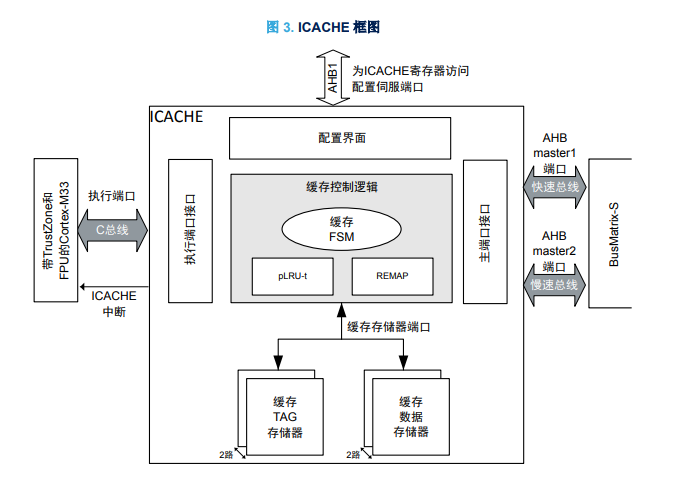

1.2 ICACHE 框图

ICACHE 框图如下图所示:

ICACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位

• 数据存储器,包含缓存的数据

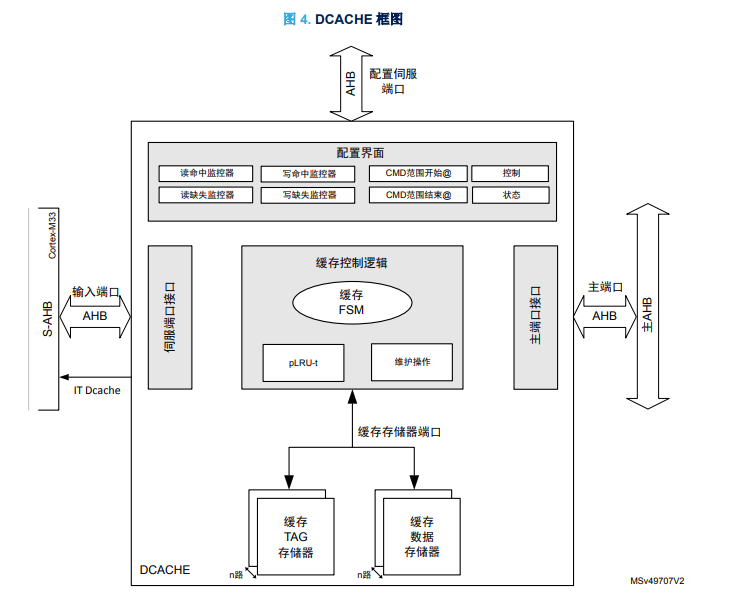

1.4 DCACHE 框图

DCACHE 框图如下图所示。

DCACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位 特权位

– dirty 位

• 数据存储器,包含缓存的数据

本文档详细介绍了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)的基本特性,并在文中提供示例介绍其性能,为大家带来关于这款指令的全面解读。由于文章篇幅有限仅展示部分,完整内容请点击“阅读原文”下载原文档。

审核编辑:汤梓红

-

通过优化代码来提高MCU运行效率2025-11-12 218

-

伺服电机编码器安装与维护最佳实践:优化性能与延长系统寿命2025-08-29 1080

-

高性能缓存设计:如何解决缓存伪共享问题2025-07-01 946

-

STM32GUI_使用 STLINK+stm32gui-pydfb 工具来实时查看图形缓存的图片2023-10-27 1858

-

使用STM32缓存来优化性能与功率效率2023-09-07 635

-

云优化性能:使用基于闪存的存储的I/O密集型工作负载2023-08-28 494

-

使用STM32缓存来优化性能与功率效率应用笔记2023-08-01 522

-

应用笔记|使用 STM32 缓存来优化性能与功率效率2023-02-05 3459

-

AN5212_利用STM32L5系列缓存优化性能和电源效率2022-11-21 572

-

UWB带通滤波器优化性能资料下载2021-04-23 1080

-

Linux和Android系统故障和优化性能的方法和流程探讨2019-07-22 1253

-

智能电机控制优化实时性能与效率设计介绍2019-07-08 2086

-

IR推出高效率氮化镓功率器件2010-05-10 1443

全部0条评论

快来发表一下你的评论吧 !