Debug Core UUID mismatch案例总结

描述

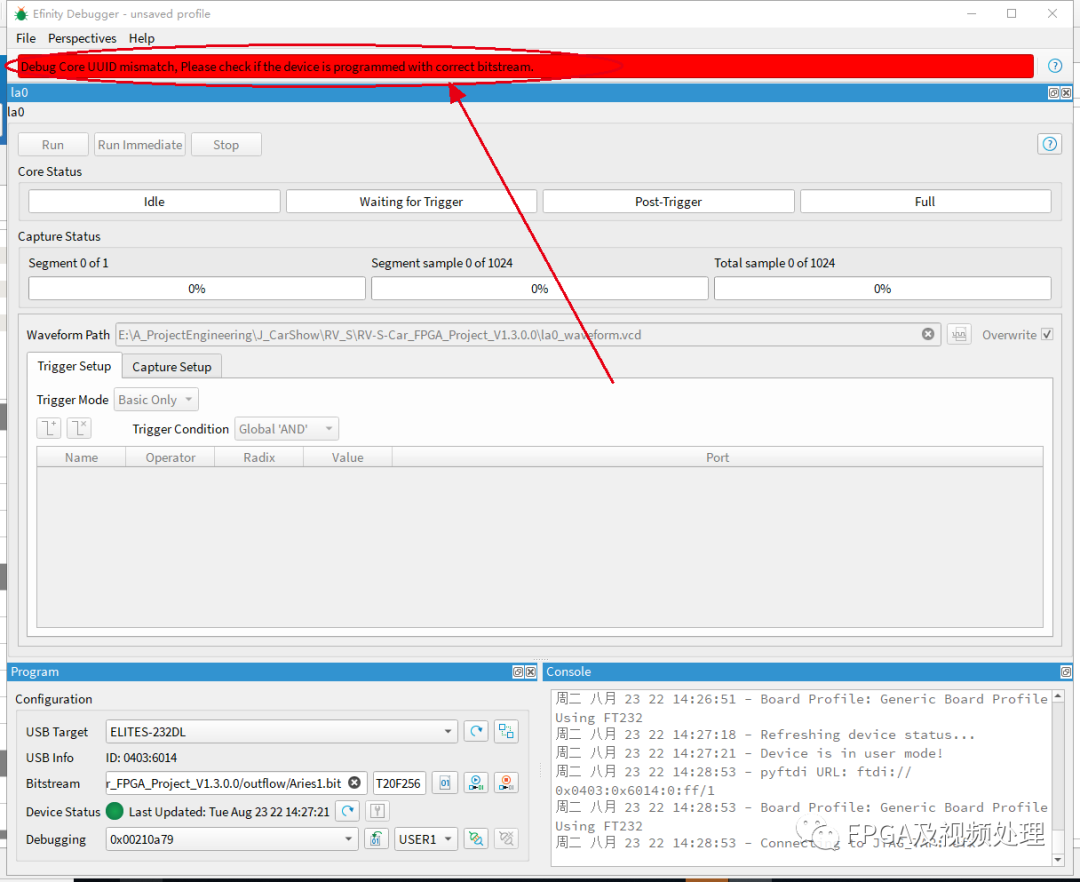

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。

一般有以下几种原因

(1)程序没运行起来。这种情况CDONE信号没有拉高,说明程序没有加载到FPGA,也可以说程序没有运行起来。

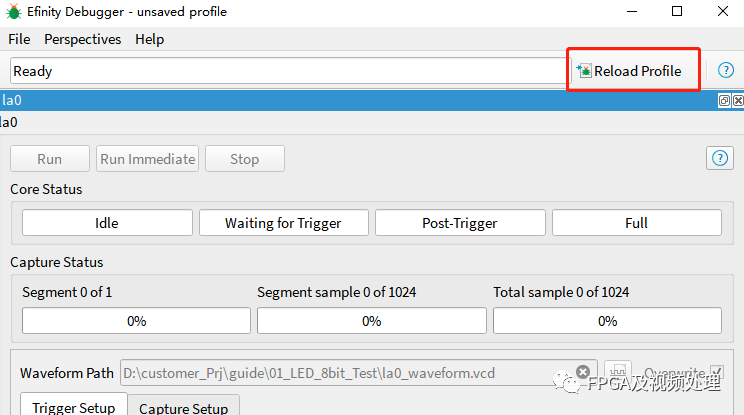

(2)配置文件与debugger文件——即json文件不对应。需要手动从Perspectives -> Profile Editor中重新import Profile,即找到json文件,目前已经添加了upload功能功能解决该问题,在界面的右上角,会提示upload。

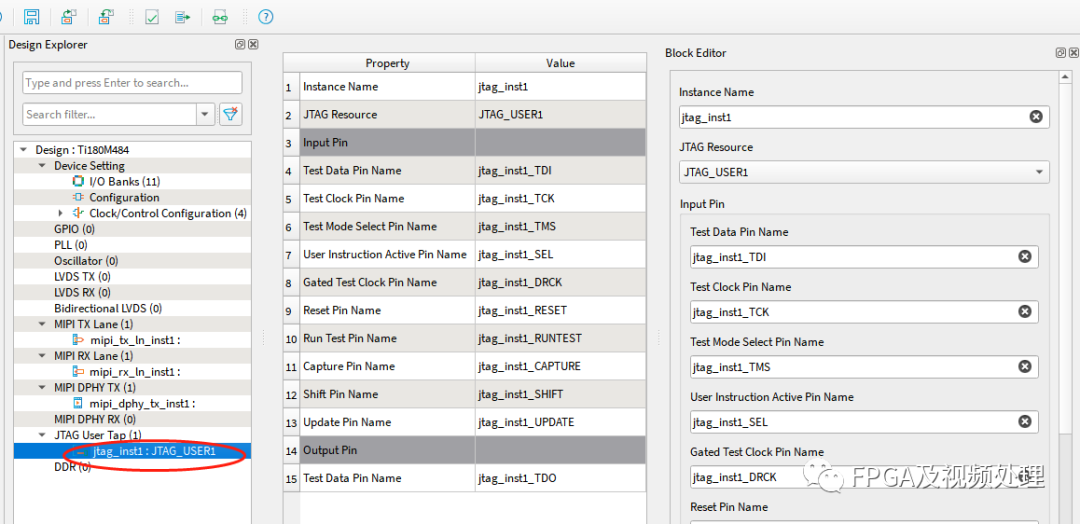

(3)通过Open Debugger添加vio或者la,但是实际上没有在Interface Designer中添加JTAG_USER_TAP。

(4)没有添加Debug;

(5)JTAG_USER_TAP接口与debug_top例化部分连接出错,比如名字不对。

(6)TI60会存在A版本与A1版本有区别不连接不上,2022.8月份之后不存在该问题。

(7)添加了vio和la但是没有添加debug_top.v到工程中,依然编译过去,连接时也会提示UUID mismatch.

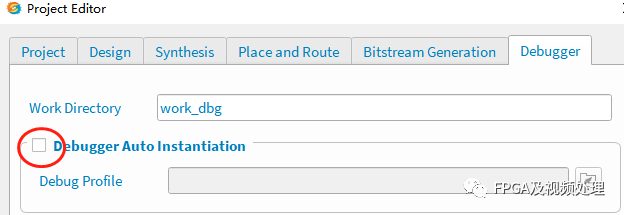

(8)Debugger Auto Instantiation没有打开。

(9)有客户第一次的设计调试信号线 TCK TDO TMS(10K上拉) TDI(10K上拉)是直连的使用正常。第二次在TCK,TDO,TMS和TDI串联了100欧的电阻,并且TCK进行了4.7K下拉,就出现了UUID mismatch。

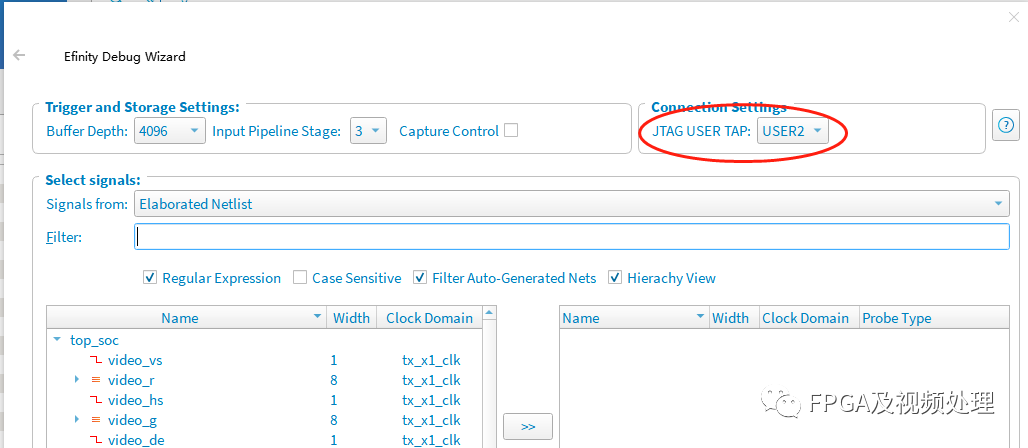

(10)JTAG USER TAP不对应。比如下图选择了USER2,但是连接时选择的是USER1.

(11)在T4,T8,T13中容易出现CRESET_N没有连接到FPGA的下载座子上。这时重新通过JTAG配置FPGA提示进入user mode,但实际上程序没有作用。

审核编辑:汤梓红

-

jf_05501773

2024-01-11

0 回复 举报添加了vio和la但是没有添加debug_top.v到工程中,依然编译过去,连接时也会提示UUID mismatch.请问这个问题怎么解决呢 收起回复

jf_05501773

2024-01-11

0 回复 举报添加了vio和la但是没有添加debug_top.v到工程中,依然编译过去,连接时也会提示UUID mismatch.请问这个问题怎么解决呢 收起回复

-

mysql为什么不推荐使用uuid呢?使用uuid究竟有什么坏处?2023-12-22 3285

-

Efinity debuger常见问题总结-v22024-07-11 3427

-

Efinity debuger常见问题总结-v32025-01-16 2438

-

一文搞清 BLE 蓝牙 UUID2025-12-18 4796

-

关于蓝牙UUID2014-08-20 3105

-

stm32 SWD烧写遇到Contents mismatch at: 08000000H2018-12-13 31395

-

6678点击ccml文件debug时当前的out文件会给所有的core都下载一遍2018-12-28 2365

-

Java的UUID生成工具并发测试2010-11-10 954

-

如何获取APP及其动态库的UUID2017-09-25 1655

-

关于蓝牙服务UUID自定义的简单介绍2021-01-29 5705

-

为什么不选择UUID?UUID有哪些特性2022-10-13 1882

-

在mysql中设计表为什么不建议采用uuid呢?2022-12-02 1396

-

Efinity在Debug时会出现UUID mismatch错误案例分享2023-02-20 2974

-

Efinity debugeri常见问题总结-v12024-05-20 1931

-

Efinity debuger常见问题总结-v42025-06-10 1487

全部0条评论

快来发表一下你的评论吧 !