四种类型的 JTAG 数据寄存器介绍

嵌入式技术

描述

本文将介绍四种类型的 JTAG 数据寄存器,分别是:

Boundary Scan Register (BSR) 边界扫描寄存器

Bypass Register (BR) 旁路寄存器

Device ID Register 设备 ID 寄存器

User Data Register(s) 用户自定义数据寄存器

在讨论边界扫描寄存器之前,重要的是,让我们首先了解为什么我们需要边界扫描寄存器。

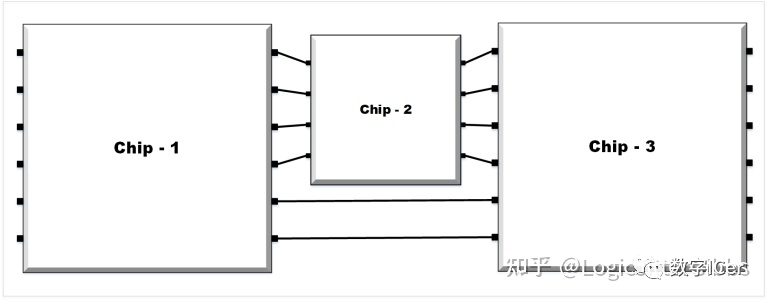

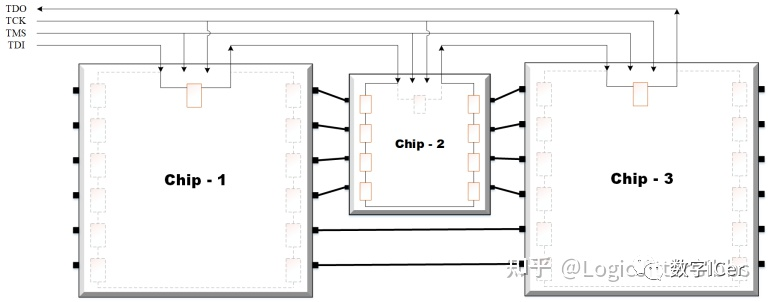

图 1:示例中 PCB 上的 3 片芯片以及它们之间的连接示意图

假设这么一种情况,我们需要将 3 片由不同厂商开发生产的芯片焊接组装在同一块电路板上。这些芯片在出厂时都已经由各自厂商使用自动测试设备( Automatic Test Equipment,ATE)测试通过。

但如果我们在把它们组装到电路板上之后,它们之间的连接性有可能会出现问题,这种情况下,我们如何发现其中的连接故障?如果只是测试连通性问题,我们没法将电路板重新送回 ATE 处再次测试其上的所有芯片,因为 ATE 的花费是非常昂贵的。

在图 1 所示的示例中,Chip 2 的 IO 本身并不是电路板级的 IO,如果出于一些调试原因,我们想通过 Chip 2 的 IO 来访问 Chip 2,那么我们如何做到这一点?

Boundary Scan Register (BSR) 边界扫描寄存器

边界扫描寄存器就是用来解决上述两个问题的。

如果 3 个芯片都支持 JTAG 访问以及边界扫描,那么我们可以控制和观测任何设备的 IO,即使它们不是板级的 IO。和扫描以及 ATPG (Scan and ATPG)的概念类似,我们可以向 BSR 中移入我们想要的数值,并观测 BSR 中的结果,来测试芯片之间的连接性。这类测试被称之为边界扫描测试。

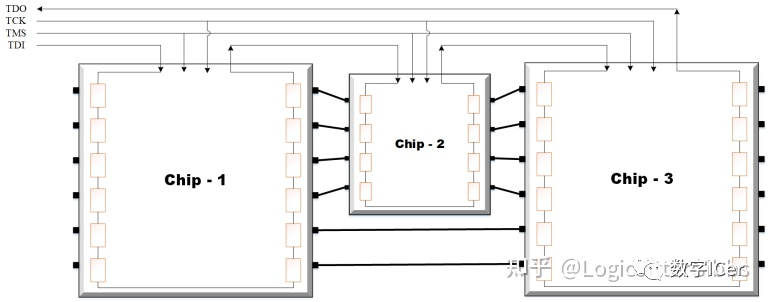

JTAG 接口允许多个设备以 Daisy Chain 的方式连接到同一个 JTAG 接口上。具体来说,TMS 和 TCK 并行地连接到各个设备上,而 TDI 和 TDO 则以图 2 之中的串行方式连接。

Note: 我们在系统任何层级中,都只能有一个 TAP (板级/芯片级/IP 模块级)。因此所有芯片都使用同一个 TAP,而不是每个芯片使用一个专门的 TAP。

图 2:边界扫描(图中橘色的矩形表示的是芯片中的边界扫描单元)

边界扫描寄存器 (BSR) 中的寄存器被插在设备的核心逻辑和 IO 引脚之间。在普通运行模式下,这些单元在通路上会被旁路,从而相当于不存在。在测试模式下 BSR 被使能,可以被用于控制 IO 引脚,以及读取 IO 引脚上当前的数值。

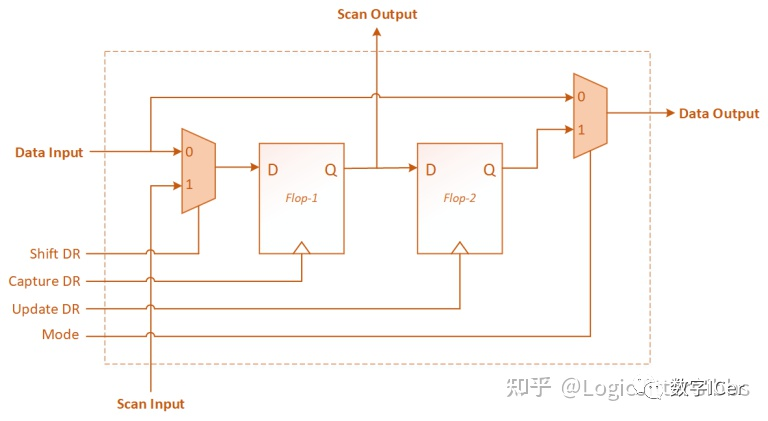

图 3:BSC 内部结构图

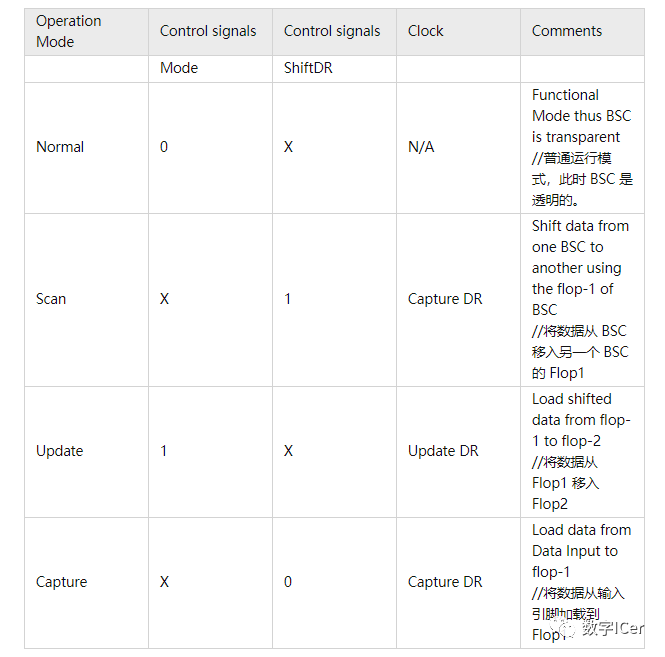

BSC 支持四种模式,每种模式情况如下表所示。

Bypass Register (BR) 旁路寄存器

旁路寄存器是一个位宽为 1 的寄存器,用于提供一条 TDI 和 TDO 之间的直接通路。这条直接通路的存在可以为电路中器件测试提供最小的测试时间开销。假设我们在电路板上有多个串行连接的芯片,如图 4 所示,如果我们想访问其中单个芯片,比如 Chip2。在没有旁路寄存器存在的传统做法中,我们需要将数据移位经过 Chip1 和 Chip3 中所有 BSC,才能访问 Chip2 中的 BSC,这增加了太多不必要的移位时间开销。为了避免上述延迟,我们需要旁路 Chip1 和 Chip3 中所有 BSC,这样数据穿过 Chip1/3 等 JTAG 设备时,每个 JTAG 设备只需要一个时钟周期延迟。

在上述示例中,具体来看:

如果我们穿过整个 Chip1 和 Chip3,那么需要 12 + 8 + 12 = 32 clocks。

但如果我们旁路 Chip1 和 Chip3,那么只需要 1 + 8 + 1 = 10 clocks。

当需要旁路芯片时,我们需要将 Bypass 寄存器对应的 opcode 加载到指令寄存器中,使指令译码器逻辑建立一条只穿过 Bypass 寄存器的旁路 TDI-TDO 路径。

图 4:旁路寄存器使用方式示例

Device ID Register 设备 ID 寄存器

ID 寄存器仅用于设备识别。假设我们有多个共享调试接口或者 TAP 的 JTAG 设备。为了确保我们正在访问正确的调试接口,每个设备的有一个 ID 寄存器,其中的数值(即设备 ID 代码)是独一无二的。设备 ID 用于使用户或者调试工具识别并确认自己访问的是正确的调试接口。

User Data Register(s) 用户自定义数据寄存器

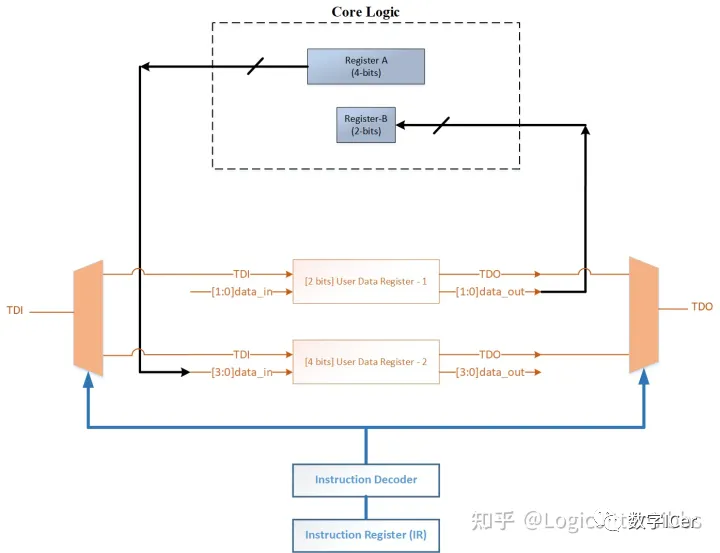

这些用户自定义的寄存器用于在调试时,控制或者观测核心逻辑中的内部功能寄存器和内部端口,如图 5 所示。一般来说,通过 JTAG 可以访问的内部功能寄存器,提供了 JTAG 访问和正常功能逻辑访问两套接口。你可以参照后一节的 JTAG 访问示例,来了解我们是如何通过用户数据寄存器来访问内部功能逻辑寄存器的。

图 5:如何通过用户数据寄存器来访问内部功能逻辑寄存器的示意图

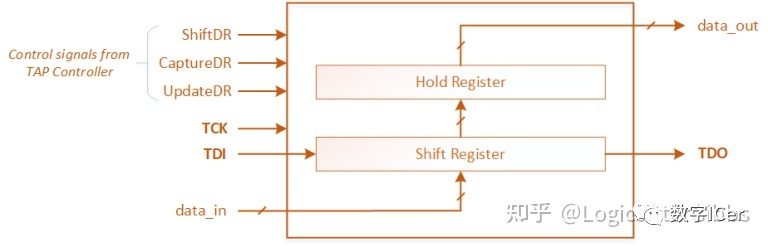

和指令寄存器类似,用户数据寄存器中也包括了两级寄存器,如图 6 所示。Hold 寄存器保持先前的数据,Shift 寄存器则在不影响当前数据的情况下,逐步移入新的数据。用户数据寄存器的控制信号来自于 TAP 控制器,具体的控制信号数值取决于当前 FSM 状态机的状态,使用户数据寄存器 Shift 寄存器移入/移出用户数据(即 Shift-DR 状态下的串行更新过程),或者使 Shift 寄存器的内容传递到 Hold 寄存器中(即 Update-DR 状态下的并行更新过程)。

值得注意的是,我们可以设计多个用户数据寄存器,每个寄存器有不同的 opcode。当我们装填特定的 opcode 到指令寄存器后,对应的用户数据寄存器才会转变为可读可写,可控制也可以观测相应的内部功能逻辑。

图 6:用户数据寄存器示意图

编辑:黄飞

-

负反馈的四种类型是什么2024-08-08 14726

-

负反馈的四种类型及判断方法2024-08-02 7532

-

寄存器分为基本寄存器和什么两种2024-07-12 3250

-

四种类型的MOSFET的主要区别2023-11-07 5587

-

什么是移位寄存器?数字电路中的寄存器类型有哪些呢?2023-09-20 10068

-

NoSQL数据库的四种类型2023-04-25 6134

-

STM32四种库对比:寄存器、标准外设库、HAL、LL2021-03-05 3618

-

寄存器的特性和四大种类2020-06-19 20779

-

四种温度传感器的数据介绍2020-02-28 1691

-

MPU6050寄存器的各种类型详细说明2019-08-08 3512

-

请问GPRS在附加图片中的寄存器是属于哪种类型的寄存器?2019-05-13 1108

-

LED路灯电源雷击的四种类型介绍2017-10-20 1264

-

数据寄存器,数据寄存器是什么意思2010-03-08 13173

-

模拟电路网络课件 第三十一节:负反馈放大电路的四种类型2009-09-17 1933

全部0条评论

快来发表一下你的评论吧 !