JTAG Operation示例

电子说

描述

通过此前一系列文章熟悉 JTAG 架构后,让我们用一个完整的示例来了解用于 Debug 访问的 TAP 是如何工作的。

假设这么一个调试场景,我们出于调试需求,需要 JTAG 能够访问并修改设计中一个 3 比特位宽的控制信号。在正常的 functional 模式中,该控制信号数值为 3'b111;但出于一些调试目的,我们想要把它改成 3'b100。以下是通过 TAP 实现这一点的过程。

假设设计中的 JTAG 指令寄存器(IR)位宽为 4 比特。

首先我们需要在 JTAG 设计中增加一个 3 比特位宽的用户数据寄存器(User DR),并将其输出连接到我们想要修改的控制信号上。接下来,我们为该 User DR 指定一个 opcode,比如 4'b1010(因为 IR 为 4 比特,因此 opcode 同样为 4 比特)。在设计中添加该 User DR 时,需要将其复位值设定为 3'b111(为什么?复位值对应于该控制信号在 functional 模式中需要的数值,即 3'b111)。

这样一来,User DR 在任何 JTAG Update 事件更改数值前,将驱动该信号为 3'b111。一般来说,在芯片上电过程中,JTAG 会比其他逻辑更早退出复位状态,因此,该控制信号能赶在被其驱动的逻辑退出复位之前,确保其数值为所需的 3'b111。

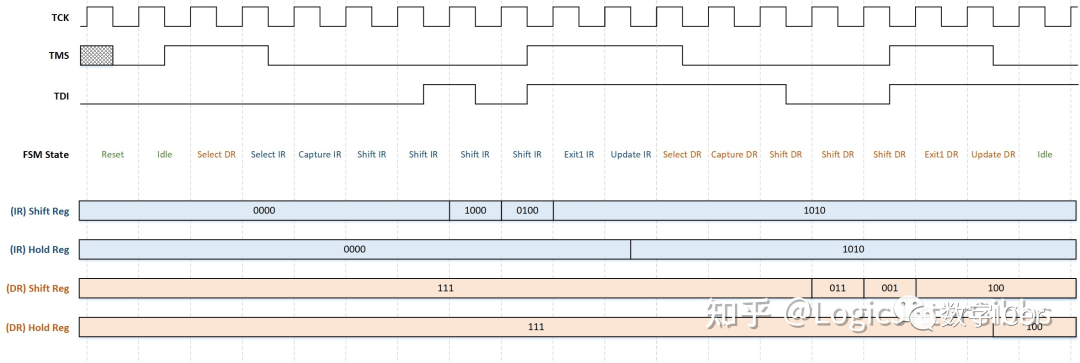

图 1- 示例的时序图

图 1 中的时序图展示了如何将 User DR 的数值更新为 3‘b100 的过程。该时序图来自 JTAG 工业标准,其中的 TMS 和 TDI 以及 IR/DR Hold Register 在时钟下降沿更新数值,而 FSM 状态以及 IR/DR Hold Register 则在时钟上升沿跳变数值。

图 1 中的 16-状态 FSM 从 Test-Logic Reset 状态开始工作,通过设置 TMS 的时序使状态机进入 Shift IR 状态。

接下来通过 TDI 端口数据寄存器对应的 opcode(4’b1010)移入指令寄存器。shift 和 hold 寄存器的初始值均为复位值 0,4'b1010 由从 LSB 到 MSB 的顺序串行地移入指令寄存器中。

通过设置 TMS 的时序使状态机进入 Update IR 状态。在 Update IR 状态中,IR 的 hold 寄存器更新为 Shift 寄存器中的值,指令译码器解码该指令的数值,建立起一条 TDI 和用户数据寄存器之间的通路。

接下来,FSM 退出 Update IR 状态,转移至 Shift DR 状态,此时串行地向 DR shift 寄存器中移入所需的数值 3'b100,由从 LSB 到 MSB 的顺序。在数据 3'b100 完全加载到 Shift 寄存器中后,FSM 跳转到 Update DR 状态。在该状态中,DR hold 寄存器更新为 3'b100,就在此时,需要修改的控制信号数值也从复位值 3’b111 改变为 3'b100。

审核编辑 :李倩

-

什么是JTAG?用途是什么2022-10-17 11318

-

JTAG简介 JTAG和SWD之间的区别2021-07-23 71827

-

ARM的JTAG调试结构2020-08-27 3956

-

怎么在Xilinx FPGA上获得JTAG详细文档的最佳位置2019-01-24 4559

-

jtag接口是什么_jtag接口定义2018-01-11 32909

-

ARM JTAG 调试原理2016-03-10 1032

-

cc3200 移植file operation 和tcp出现的rtos问题2016-02-24 4471

-

LT1017:Circuitry for Single Cell Operation2012-01-06 885

-

JTAG功能及系统设计2011-03-30 1744

-

JTAG调试原理(推荐)2009-05-27 650

-

JTAG先进的功能和系统设计,JTAG Advanced C2009-05-16 780

-

JTAG口及其对Flash的在线编程2009-04-16 783

-

PMU Mode Operation for the MAX2008-12-25 1938

-

什么是jtag接口 jtag接口定义 JTAG ARM2007-12-20 54129

全部0条评论

快来发表一下你的评论吧 !