适用验证ASIC的Veloce硬件仿真加速平台

EDA/IC设计

描述

众所周知,未来十年,互联网数据量预计将会井喷。随着 5G 的扩建、智能社区基础设施的发展、汽车数据流和其他数据生成的持续增长,保持这些系统正常运行的网络将会面临越来越大的压力,承载的数据量与日俱增。

从 2021 年到 2025 年,全球数据消耗量预计将增加一倍以上,从 79 ZB 增至 181 ZB。平均连接速度也将在未来几年内大幅提高,其中固定互联网连接速度从 46 Mbps 增至 110 Mbps,Wi-Fi 连接从30 Mbps 增至 92 Mbps,移动连接从 13 Mbps 增至44 Mbps(所有数据均相较于 2018 年)。

因此,网络设备制造商面临巨大的压力,确保路由器、交换机和全球网络的其他关键部件能够继续领先于容量曲线的变化。这是通过使用更多的连接来增加网络规模以及增加每个连接的带宽来实现的。

于是,这些设备的压力便转化为对构成网络盒核心的ASIC 的严苛要求。芯片的尺寸和复杂性与日俱增,如果没有新的方法,这些芯片的设计和验证将会威胁到上述关键网络系统的发布。

由于验证仍旧占据设计进度预算的很大一部分,它在缩短完成设计所需的时间方面起到极大的杠杆作用。在相较于过去,以更彻底和更快速的方式验证网络芯片方面,西门子 EDA 的 Veloce 硬件仿真加速平台发挥着关键作用。

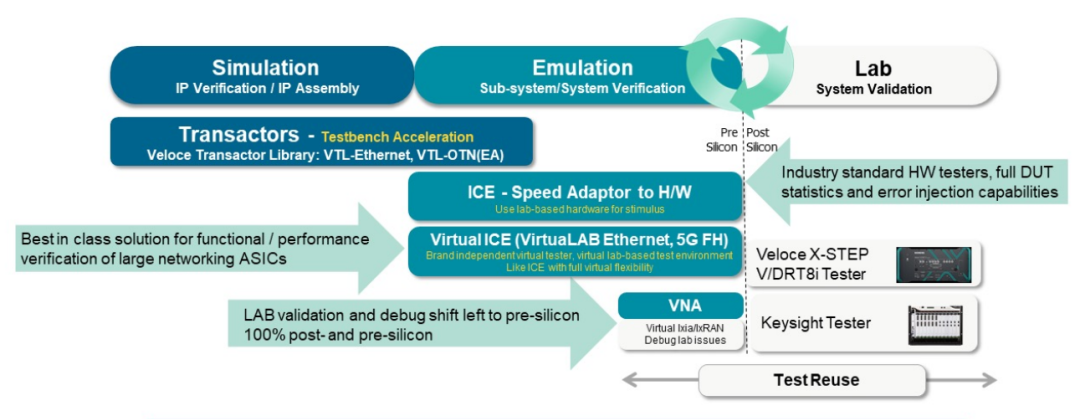

▲仿真、Veloce 硬件仿真加速和硅后验证处在一个连续体上,允许测试案例在三者之间平滑移植。

Veloce 硬件仿真加速平台是一款完整的解决方案,适用于全面验证先进网络 ASIC。

● VirtuaLAB 以太网解决方案、虚拟 OTN 解决方案、Veloce 网络应用程序和 VirtuaLAB 5G Fronthaul 解决方案等虚拟化工具,抽象出了许多新协议的详细信息,大大加快了设计的上市速度。

● 软件和硬件可以并行验证,更轻松地识别和解决两者中存在的错误。

● Veloce Strato+ 平台的容量为各种网络 ASIC 提供了所需的灵活性和可扩展性,极大地改善了 ASIC之间的设计复用。

编辑:黄飞

-

硬件仿真器需求攀升 Veloce平台稳坐钓鱼台2013-11-26 2578

-

Veloce平台在大规模SOC仿真验证中的应用2010-05-28 2356

-

Veloce Apps硬件仿真平台2016-04-15 3482

-

可测性DSP软硬件协同仿真验证平台设计2011-06-09 1252

-

Mentor Graphics在其企业验证平台中新增ARM AMBA 5 AHB验证IP2015-11-12 1584

-

Imagination使用Veloce平台进行PowerVR Wizard光线追踪GPU验证2015-12-21 3815

-

Mentor Graphics 发布 Veloce Apps:开启硬件仿真新纪元2016-02-26 1562

-

Mentor Graphics硬件加速仿真服务使用Veloce 硬件加速仿真平台加速验证2016-04-20 3010

-

Mentor Graphics Veloce 硬件加速仿真平台协助 Barefoot Networks 验证全球首个完全可编程开关2016-07-20 1601

-

UVM验证平台执行硬件加速2017-09-15 1418

-

忆芯科技利用Veloce 硬件加速仿真平台进行高速企业级固态硬盘存储设计2018-07-12 2248

-

Veloce仿真环境下的SoC端到端硬件加速器功能验证2018-03-28 4723

-

利用硬件加速器提高仿真速度时的验证平台考虑2018-03-05 1557

-

西门子数字化工业软件推出Veloce CS硬件辅助验证和确认系统2024-05-08 1802

-

西门子Veloce硬件辅助验证平台升级2025-02-10 1422

全部0条评论

快来发表一下你的评论吧 !