数字扫频仪中衰减电路设计

测试测量实验

描述

数字扫频仪在现代电子教学实验和工业测量中应用广泛,它是一种专门用于测量电子设备中某些电路频率特性的专用仪器。目前,国内已经出现了一些数字频率特性测试仪,通过对市面上现有的主要产品进行使用、测试和研究,发现多数仪器的输出衰减步进值仅能达到1dB,还有一些仪器输入部分没有衰减电路,没有输入衰减电路的仪器在测试较大增益的放大电路时存在明显的缺陷。针对以上这些问题,本文提出了数字扫频仪中衰减电路的设计方法,给出了电路原理图以及计算公式,并验证了方案的有效性和正确性。

1 衰减网络的作用

由于不同被测网络对其输入信号的功率要求不同,因此利用输出衰减电路可对测试仪输出信号功率进行调节。而为防止被测网络输出信号过大而导致测试仪过载,则需用输入衰减电路对被测信号进行衰减。仪器中的衰减电路还可起到隔离作用,从而减小被测网络与仪器信号源、被测网络与幅度相位检测电路之间的相互影响。

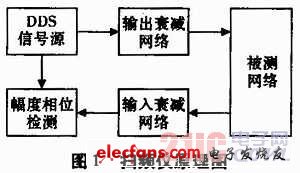

扫频仪的原理图如图1所示。DDS扫频信号源产生的扫频信号一路送到幅度相位检测电路作为参考基准,另一路送到输出衰减网络。输出衰减网络可使扫频信号的幅度按0.1 dB步进进行衰减。输出信号经过被测网络,送到测试仪的输入衰减网络,使得被测信号符合幅度相位检测电路的输入要求。幅度相位检测电路对被测网络的输入、输出信号进行模拟鉴相和检波,然后将所得到的关于被测网络频率特性的模拟量经ADC采样转换为数字量。最后,CPU处理幅度相位检测电路中的数据时,还需要把输出衰减以及输入衰减的特性计算在内。因此,衰减电路的性能与精度,直接影响整个频率特性测试仪的测量精度,故衰减电路是在频率特性测试仪中非常重要的一部分。

2 步进值为0.1 db的衰减网络

采用阻抗匹配型衰减器是最常用的衰减方式,此类衰减器插入损耗低,不影响系统的频率特性,且制作简单,成本较低。但在实际应用中当衰减步进很小时,不容易找到符合要求的电阻。并且由于电阻阻值小,衰减电路精度受电阻阻值误差的影响较大。因此,可采取压控增益放大器实现小步进值的衰减,并与采用阻抗匹配网络实现大步进值衰减的方式相结合。电路结构简单、操作方便,且成本较低。

2.1 模拟乘法器

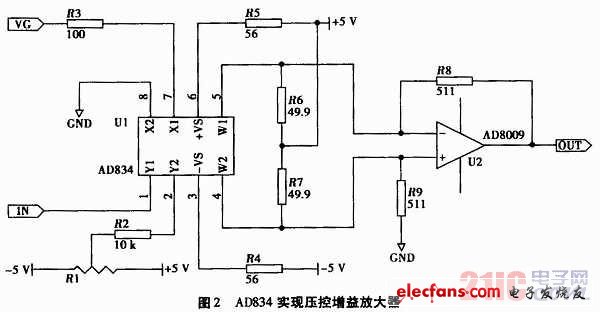

采用模拟乘法器AD834和固定增益放大器便可构成压控增益放大器(VCA)。AD834是一款宽频带、四象限、高性能的模拟乘法器。输入输出均为差分方式,由于其输出端的集电极开路差分电流结构,不仅可以有效地抑制由输入端直接耦合到输出端的直通分量,还可以保证电路有很宽的频率响应。其频率响应范围为DC~500 MHz,乘方误差小于5%,且工作稳定,受温度和电源电压的影响小。因此,AD834非常适合应用于扫频仪这种对输出信号有很高要求的系统中。在固定增益放大器之前,模拟乘法器可作为电压可控的衰减器。其电路图如图2所示。

AD834的输入信号是可控的电压,其输出为集电极开路的差分电流。在这种情况下,运算放大器ADS009实现了电流到电压的转换,并且使用阻值均为511 Ω的反馈电阻R8和R9实现了增益范围为-70 dB~+12 dB的电压增益控制。当VG约等于0时,增益为-70 dB,当VG为1 V时,增益为12 dB。控制电压VG可以是正的,也可以是负的,还可以是完全差分的。当VG为正电压时,输出信号与输入信号同向,当VG为负电压时,输出信号与输入信号信号反相。

如图2所示,在扫频仪衰减电路中,最好使用Y作为乘法器的信号输入端,因为Y端口比X端口具有更好的线性。虽然AD834的输入电路有20 kΩ,但每个输入端仍有45 μA的偏置电流。在本设计中采用单端的输入方式,如果信号源的内阻为50 Ω,输入端便会产生1.125 mV的失调电压。因此在Y2端口,加上一个大小和极性可调的直流电压可有效地消除这一误差。由于本设计中输入方式均采用单端的输入方式,因此采用远离输出端的Y1作为信号输入端,以减小输入端直接耦合到输出端的直通分量。VG作为驱动源具有较差的高频特性,因此在姗端串联一个100 Ω的电阻R1可以减小信道上可能存在的噪声。

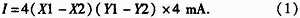

AD834实现的衰减电路其计算过程为:输入端X1和X2输入的差分电压与输入端Y1和Y2的差分输入电压相乘,再与芯片内部所决定的1 V相乘,所得的结果再除乘法器内部的一个阻值为250 Ω的精密电阻,从而得到输出电流,其公式表示为:

I是W1和W2的差分电流,X1、X2、Y1和Y2表示该输入端的电压值。因此,当差分输入端均为1 V时,I为4 mA。AD8009的输出电压可以简单地表示为:

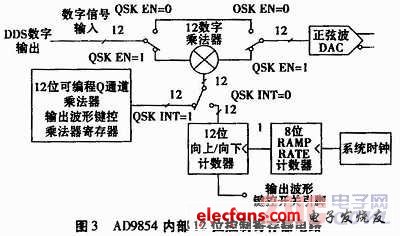

2.2 DDS芯片内部数字乘法器

有些DDS芯片,具有输出波形键控功能(OSK),如AD9854。如果信号源采用AD9854,则可充分利用DDS芯片的内部资源,通过配置其内部的12位数字乘法器对输出信号的幅度进行调节,且这种方式成本较低,不用增加外围电路,提高了资源的利用率,其原理框图如图3所示。

AD9854中的OSK功能允许用户对输出信号的幅度以及时间斜率进行控制。用户可对AD9854内部控制寄存器0x20中的OSK EN(bit5)进行设置来选择12位数字乘法器。如图2所示,当OSK EN设置为1时,数字乘法器被选中,用户可通过设置数字乘法器来改变输出信号的幅度。当OSKEN设置为0时,数字乘法器被旁路,输出信号将满幅输出。当对12位数字乘法器每一位均设置为0时,则乘法器的输入信号与0相乘,则输出值为0。当对12位数字乘法器每一位均设置为1时,则表示乘法器的输入信号与4095或4096相乘,几乎为满幅输出。按照此依据,则DDS信号源可按二进制编码规则,可任意设置使其输出另外4094个不同的幅度值。具体实现方法与衰减量的对应关系如表1所示。

采用这种方式进行衰减的同时,送入到幅度相位检测电路中的参考信号同时改变。因此,在做数据运算时,应把信号源端的衰减量计算在内。

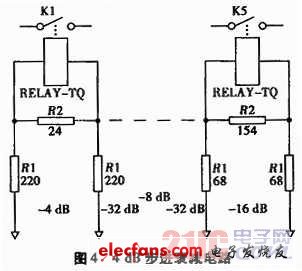

3 步进值为4 dB的衰减电路

扫频仪中可采用0.1 dB步进衰减网络与4 dB步进衰减网络相结合的方式。4 dB步进衰减电路可采用兀型的阻抗匹配衰减电路,由衰减量为-4 dB、-8 dB、-16 dB以及2个衰减量为-32 dB的П型电阻网络和作为开关的继电器组成。其电路如图4所示。

使用1%的电阻,可以实现非常高精度的电阻衰减网络。实际测试的衰减量分别为:-4.02 dB、-7.97 dB、-16.04 dB以及-31.97 dB。按照误差传递公式,可计算出-4dB、-8 dB、-16 dB、-32 dB衰减网络的误差范围,其合成误差传递公式为:

式中,y为系统误差。根据误差合成公式可计算出其他各级衰减网络的误差范围,其分析结果如表2所示,误差合成公式为:

4 结束语

本文提出了扫频仪中衰减器的设计方法。根据不同的信号源可以采用不同的衰减电路。采用模拟乘法器AD834实现的压控增益放大电路最大可以实现-70dB的衰减,其频率范围宽、工作稳定、噪声小、精度高。通过配置AD9854内部数字乘法器,同样可以实现精确的衰减功能,提高了资源的利用率。整个设计可采用0.1 dB步进与4 dB步进衰减网络相结合的方式,操作简便、测量范围广、精度高,降低了制作成本。

-

【FPGA参赛作品】基于FPGA的数字存储扫频仪2012-07-07 6198

-

低频数字扫频仪2013-04-03 3096

-

基于直接数字合成的扫频测试电路设计2009-06-18 681

-

带中心频标的扫频仪电路图2009-04-09 3445

-

FPGA数字存储扫频仪(源代码+电路图+PCB图)2012-12-06 3246

-

基于正交DDS单边带调制扫频源电路设计与实现2017-07-30 1361

-

基于ICL8038的自动扫频电路设计2021-03-18 1849

全部0条评论

快来发表一下你的评论吧 !