知道这一点,射频系统设计能力上个台阶

描述

你是否还在为你接收机中的邻信道抗扰性头疼不已?

怎么就没达到指标要求呢?

到底要整哪部分呢?

更换滤波器的形式,提高滤波器的抑制度?但是到底要提高多少?

改变一下链路中的增益,会不会有效果?

优化一下本振的相噪?但到底要优化多少。

今天这篇文章就给你讲清楚。

假设,链路的动态范围是OK的,也就是说,强的干扰信号和小的有用信号一起进入接收机,不管采用何种手段,需要保证,这两个信号到达ADC前面时,两者的功率差,是能满足ADC的SFDR的,即ADC能够同时识别这两个信号。

这时,邻信道抗扰性的好坏,就主要与以下两个因素相关:

(1) 本振相噪

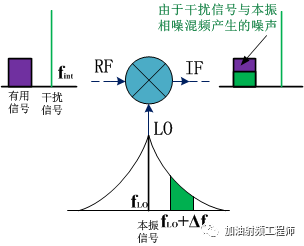

干扰信号会与本振相噪,通过混频器,在有效中频处产生噪声,进而影响信号的SNR,如下图所示。

(2) 混频前链路中对干扰信号的抑制度

上面的两个因素是联动的,混频前链路中对干扰信号的抑制度增加1dB,对本振相噪的要求就会降低1dB。

所以,可以由邻信道抗扰性指标,推算出要求的本振相噪。如果本振由于其他限制,达不到要求的指标,就可以用滤波器来协助。

有人说,我觉得那些公式太烧脑,我想闭眼就能计算出来。

没问题,我给你们整理成excel计算工具了。

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

求助,为何作为USB从设备时,M4521能免晶振,而M452没说这一点?2023-06-19 437

-

用编程方式禁用滑块我怎样才能做到这一点?2022-12-05 474

-

PCB厚铜板的设计,这一点一定要注意2022-08-16 3017

-

【经验分享】PCB打板,只做错了这一点,直接损失上百万!2022-07-18 2278

-

直角减速电机真的可以节省空间吗?它是怎样做到这一点的?2021-11-22 1246

-

轻薄与高性能可否兼具?最新的AERO 15 OLED版做到这一点?2019-08-27 3931

-

在用到stm32的adc的时候需要注意外部无法操作这一点吗?2019-07-31 1947

-

请问我该如何停止这一点,并获得准确的阅读?2019-06-13 1238

-

空调能效等级对消费者的意义真的就只是省电这一点吗2019-05-17 8780

-

我希望PSOC-5在使用UBFSUART时中断,每次接收到字节,如何做到这一点?2018-08-28 955

-

W25Q128FV图像写入如何在PSoC5LP中做到这一点?2018-08-16 1836

-

iOS10.2正式版发布 但苹果这一点还是输给了小米2016-12-14 7326

-

如何判断你的电路设计能力2014-12-09 5851

-

一点接地,什么是一点接地,一点接地应注意的问题2009-09-30 28733

全部0条评论

快来发表一下你的评论吧 !