大学毕业设计一席谈之二十七 位同步环路的matlab仿真(6)解惑篇

描述

2023年,本系列的续集来啦。又见面了!重磅系列!全网独一份哦!看完自然就掌握了位同步的知识!

在公众号的中部菜单里面找!

粉丝留言的问题都有解答。关于为什么内插会在0和1两个值附近跳动的问题将在本文做详细解释!我还为此画了图,以帮助粉丝理解!

之前写了五篇文章。2022年,在写本系列文章的时候,读者发来问题,自然要解答。我非常喜欢有问有答的互动过程。先看是什么问题!

蔡老师,我之前看了公众号位同步的文章,程序仿真通过了。有两个问题想请教您:

1、经过farrow滤波后,y(I)和y(Q)是最佳采样信号,那么恢复的位同步时钟是哪个量,是NCO吗?我看点数又是符号数的两倍,怎么理解呢?

2、位同步恢复的时钟和最佳采样如果工程上实现的话,怎么在时域上对应?即一个时钟对应一个码元。

对于IQ两路信号,如何实现位同步呢?给出案例程序,结合程序讲解!QPSK信号在位同步环路中就是使用了IQ两路信号。实际中位同步怎么使用呢?这里要补充讲解!用环路实现位同步只是其中的一种方式!前向纠错也可以实现位同步。

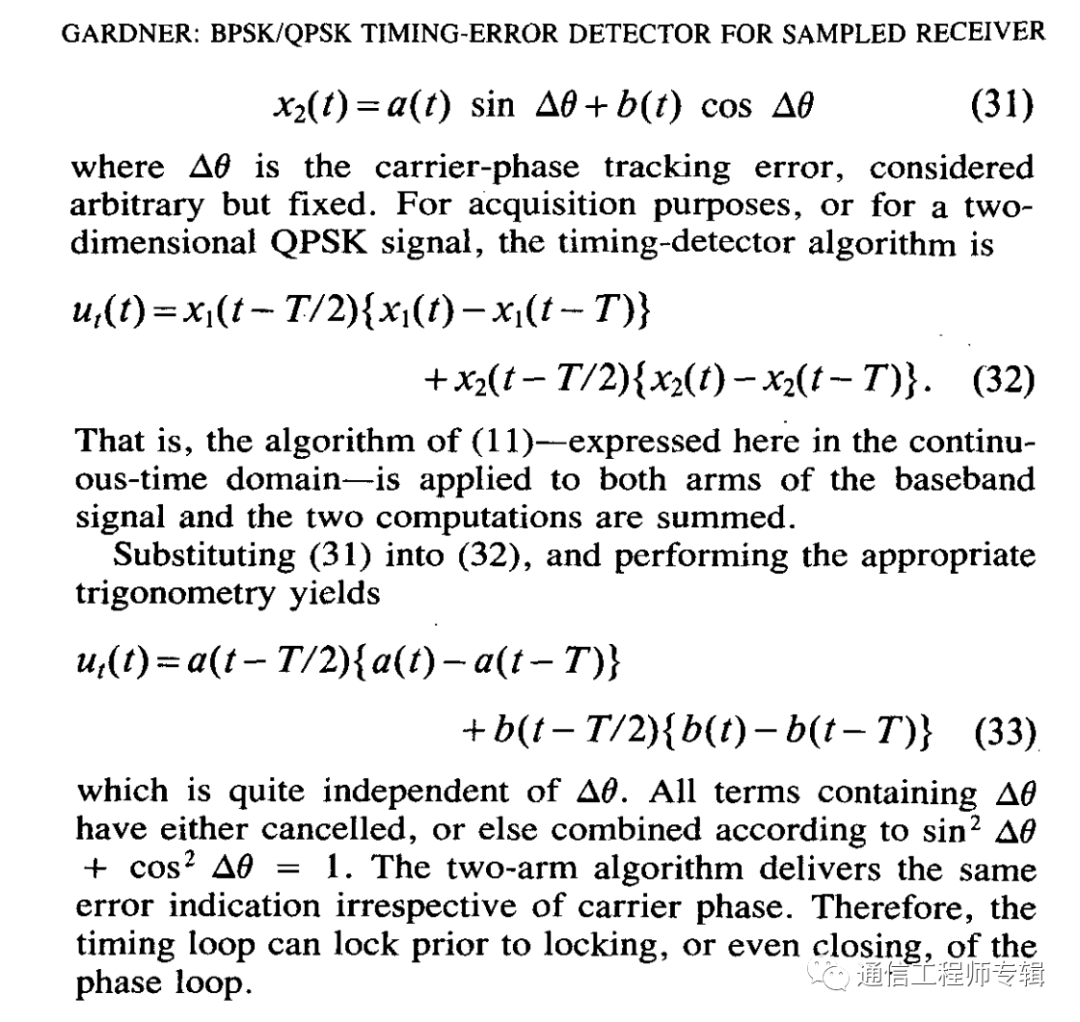

先看QPSK信号用于环路中的定时误差检测公式!下一篇文章就会涉及到此公式!不急,一步一步的学。先搞清楚环路涉及的相关概念!

代码该怎么改呢?

原文标题:大学毕业设计一席谈之二十七 位同步环路的matlab仿真(6)解惑篇

文章出处:【微信公众号:通信工程师专辑】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 通信网络

-

大学毕业设计一席谈之二十五 GMSK差分解调仿真(7)在AIS系统中的应用之理论仿真2023-09-13 1808

-

大学毕业设计一席谈之二十五 GMSK差分解调仿真(6)在AIS系统中的应用之总体规划2023-09-11 1864

-

大学毕业设计一席谈之四十八 词频统计(5)函数优化2023-06-09 973

-

大学毕业设计一席谈之四十八 词频统计(3)自编函数!2023-05-28 1041

-

大学毕业设计一席谈之四十v2 CRC校验(3) 结合编译码2023-05-26 867

-

大学毕业设计一席谈之九 多种编码方式的通信系统仿真(6) RS码联合卷积码仿真2023-05-25 1226

-

大学毕业设计一席谈之九 多种编码方式的通信系统仿真(4) RS码仿真2023-05-21 1262

-

大学毕业设计一席谈之四十一 压电信号的睡眠检测算法(6)函数和系数固化2023-04-17 989

-

大学毕业设计一席谈之四十一 压电信号的睡眠检测算法(4)浮点转定点2023-04-12 1060

-

大学毕业设计一席谈之二十七 位同步环路的matlab仿真(8)误码性能2023-02-10 693

-

大学毕业设计一席谈之二十七 位同步环路的matlab仿真(7)更正错误和加入频偏2023-02-09 1237

-

大学毕业设计一席谈之四十七 音频信号分频混响器设计(1)2023-01-14 1398

-

大学毕业设计一席谈之四十六 集群产品中的物理层算法仿真(3)函数内容和文档2023-01-10 1028

-

大学毕业设计一席谈之二十 BPSK相干解调仿真(14)信噪比等效!2021-12-30 2500

全部0条评论

快来发表一下你的评论吧 !