插值法帧同步(ISE/Verilog/CXD301)

描述

1 运行平台

硬件:CXD301数字信号处理板 系统:win7/64;win7/32;win10/64 软件:ISE/ModelSimSE/Verilog/Matlab

2 主要功能及性能指标

3.2.1主要功能

1)产生基带原始数据

2)帧同步信号提取

3.2.2主要性能指标

1) 发送端

系统时钟:50MHz

基带数据码率:195.3125kbps

数据内容:帧长16位,帧同步字长7位,同步字为1011000

2) 接收端

系统时钟:发送端送来的数据时或信号,195.3125kbps

同步方式:具有搜索、校验、同步三种状态:帧长、帧同步字、搜索容错位数、校核容错位数、同步容错位数可通过修改程序参数快速设置。

3 程序结构框图说明

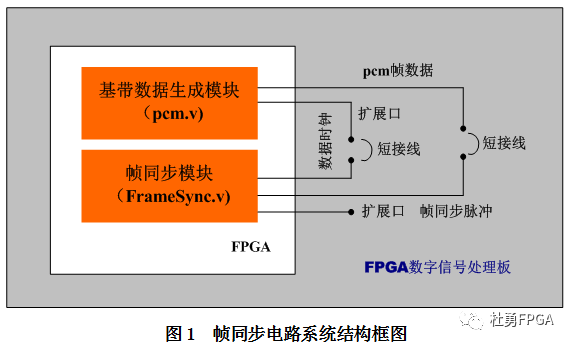

帧同步电路系统主要由基带数据生成模块(pcm.v)、帧同步模块(FrameSync.v)模块组成。

基带数据生成模块生成的原始数据(1.5625Mbps)送至开发板上扩展口,经短接线由第35脚送回FPGA芯片;数据生成的同步时钟信号也经扩展口硬件环回至帧同步模块。为便于测试环路同步及失步状态,输入端设计了一个数据选择控制逻辑,通过按键控制输入数据。帧同步的详细工作原理及实现方法请参见《数字通信同步技术的MATLAB与FPGA实现》或观看杜勇老师讲解视频。

4 资料清单

1)FPGA工程源程序(提供网盘链接)

2)开发工具(提供网盘链接):ISE/

ModelSim/Verilog HDL/Matlab2014a/串口调试助手

安装方法请关注B站UP主:杜勇FPGA 观看“FPGA环境安装”合集

3)工程代码讲解视频(杜勇老师主讲,可在线观看)

主要包括功能说明、FPGA代码讲解、ModelSim仿真过程、板载测试方法等完整的设计测试流程。

程序功能说明(试看)

系统测试视频(试看) FPGA程序设计视频及FPGA工程源程序(付费后可见)

审核编辑 :李倩

-

插值法帧同步解析2023-03-06 1227

-

一文简析插值法帧同步2023-02-10 1519

-

插值法帧同步ISE/Verilog/CXD301介绍2023-02-08 2084

-

帧同步通常采用的方法有逐位调整法和置位调整法,对比分析哪个好?2021-04-14 2123

-

verilog实现三次样条插值2018-05-13 5183

-

采用FPGA实现同步、帧同步系统的设计2017-11-07 1286

-

Verilog实现闰年的判断(ISE8.21中调试通过)2016-06-07 1527

-

基于FPGA的帧同步系统设计方案2013-11-11 5947

-

FPGA设计中帧同步系统的实现2012-08-11 4251

-

一种基于插值算法符号同步的硬件设计2010-07-05 992

-

帧同步,帧同步是什么意思2010-03-17 24802

全部0条评论

快来发表一下你的评论吧 !