单粒子翻转效应的FPGA模拟技术 (下)

电子说

描述

4

旁路电路注入故障

旁路电路技术的实现原理和扫描链技术类似,在原有的电路结构上添加附加电路来使电路能够模拟单粒子翻转效应 ^[25-26]^ 。以寄存器为例,在正常状态下寄存器保持其原本的功能,在故障注入模式下通过外部控制信号驱动附加电路从旁路修改寄存器的数值。

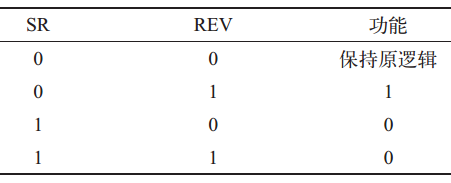

文献[27]介绍了一种旁路电路注入故障的电路结构,基于Xilinx Virtex-5的FPGA实现,带旁路电路的寄存器结构如图4所示。该电路在原本的寄存器结构上添加了3个查找表(Look-Up-Table, LUT)和额外的输入信号,修改寄存器的复位信号SR(Set/Reset)和翻转信号REV(REVerse)的输入值来实现故障注入功能。默认模式下寄存器对应的真值表如表1所示。

表1 默认模式寄存器真值表

图4中,输入信号inj为故障注入使能信号,Original_CE、Original_R和Original_S分别连接寄存器原始的时钟使能CE、复位Reset和置位Set信号。如果inj为0,该寄存器等同于普通的寄存器,而inj为1时,3个查找表就会根据寄存器的输出值Q生成相反的值并写入寄存器。

图4 带旁路电路的寄存器结构

文献[28]的电路修改方式更加简单,仅在原始寄存器结构上增加了一个异或门。替换前后的寄存器结构如图5所示。当故障注入信号Inject信号为高电平时,寄存器的输入端数据会发生翻转,而Inject信号为低电平时,寄存器的输入端数据保持原始状态。和文献[27]相比,区别在于故障注入时,文献[28]的寄存器数值一定会进行翻转,而文献[27]则可以模拟更加复杂的情况,因为单粒子翻转效应在作用于寄存器时有固定0、固定1和翻转3种情况,并不一定会导致翻转。但是,文献[28]的电路结构的资源开销比文献[27]小得多,具备一定的优势。

文献[29-30]介绍了另一种旁路电路的实现方式,通过对电路综合后的网表进行修改,将原有的器件库全部替换成为附加故障注入功能的器件库,其中包括寄存器、随机存取存储器(Random Access Memory, RAM)、查找表、逻辑门以及乘法器等,更新后的网表的时序逻辑部分不会受到影响,只是添加了故障注入相关的组合逻辑模块。但其实现过程较为复杂,器件库的修改需要耗费大量的时间进行功能和时序验证。同时器件库和FPGA型号是紧密联系的,更替FPGA芯片将可能导致器件库无法使用,因此迁移性较差。

和扫描链技术相比,旁路电路技术省去了串行移位故障数据的过程,故障直接注入到待评估寄存器中,从而提高了故障注入速度。旁路电路同样可适用于任意规模电路,而且可以针对电路中的其他存储元件(LUT、RAM等)设计故障电路,适用范围更广,故障敏感节点的定位精度也高于扫描链。其主要缺陷会带来额外的资源开销,此外还可能增加关键路径的延时,对时序造成负面影响。

除了故障注入速度的差异,文献[31]同样提到了数据交互过程造成的庞大时间开销,文中基于RS232传输故障激励数据,传输速度配置为115 kbit/s,单次数据传输过程需花费14 ms,而故障注入执行过程仅占2 ms,因此导致故障注入速度偏慢。

5

故障注入方式对比和展望

5.1 故障注入方式对比

FPGA模拟技术主要用于评估超大规模集成电路设计对单粒子翻转效应的敏感性。因此本文从评估速度、电路开销和敏感点定位精度3个方面进行对比,故障注入方式具体性能对比如表2所示。

表2 故障注入方式性能对比

FPGA模拟技术中的重配置技术存在速度瓶颈,虽然通过部分重配置可以显著提高效率,但是与修改电路结构的方式相比较,重配置技术故障注入速度稍慢。若基于扫描链去实现,其串行移位的故障注入模式会带来一定的时间开销。而旁路电路方式可使得电路即时响应故障,不会产生额外的时间开销。

在电路开销方面,由于重配置所需要的硬件电路都固化在FPGA芯片内部,所以额外需要的电路开销是最小的。考虑到扫描链可以复用可测性设计的扫描链结构,所以电路开销稍低。电路开销最大的是旁路电路,因为每个寄存器外围都需要配备译码选通电路和故障注入电路,但是随着FPGA的技术开发,单LUT电路能够实现的功能愈加复杂,其占用的电路开销比例也可以不断下降。

在敏感点定位精度上,由于配置文件格式不公开,多数研究采取随机注入或是遍历式注入,但是注入故障后难以在最初的原始设计文件中定位故障节点,这对评估工作非常不友好,难以指导后续的改进工作。由于扫描链是串行结构,定位需要依赖输入激励和输出响应的先后顺序,这会和评估速度形成互相制约的关系。因为如果注入速度过快,对准确采样高速输出响应的工作会提出很高的要求。旁路电路由于具有专用接口电路,因此即使在高速注入情况下,也能准确定位注入故障的位置。

5.2 故障注入方式展望

重配置、扫描链和旁路电路3种方法的实现结构不一样,优化的思路也会有所不同。

重配置在评估速度上表现不佳,主要是由于上位机和FPGA之间频繁通信造成较大的时间开销。如何让测试激励以更快的速度配置到FPGA中是未来的提高方向。采用DDR缓存测试激励,以及采用类似Xilinx ZYNQ架构的芯片作为测试平台,都是可行的方式。在确定注入故障定位上,可行的思路有对比配置文件格式和配置后器件位置,对配置文件进行破解。但是需要按照电路版图结构从大到小逐次解析,并区分LUT、RAM等多种存储元件,工作量比较庞大 ^[32]^ ,所以重配置技术的改善工作更适合FPGA设计厂商实施。

在有可测性设计的电路中,扫描链技术是非常合理的选择。但是,为了提高测试效率,如何压缩测试激励的数量,以及测试响应的高效对比,是扫描链技术未来的发展方向。此外,扫描链的电路结构也可以进行一定的优化,主要在提高运行速度和降低开销两方面进行针对性的改进,扩充可测性设计的研究范畴。

旁路电路的改进方向是进一步压低电路开销。这方面可以考虑相邻电路之间复用故障注入电路,从而降低电路开销。需要注意的是,旁路电路往往和测试平台的器件库密切相关,所以未来在设计电路时可以将电路修改方式设计成通用脚本,通过算法和器件库建立联系,从而增加其适用范围。

此外,由于3种方案的优势各不相同,未来的评估平台也可以结合多种方式。比如可利用旁路电路故障注入的准确性弥补重配置技术的精度缺陷,提高注入速度,同时也可以通过重配置技术避免旁路电路相关故障注入模块的资源开销。这样不仅平台的评估效率有所提高,评估电路的适用范围也变得更加广泛。

6

** 总 结 **

随着集成电路工艺迈入纳米时代,现有FPGA模拟技术面临的最大挑战是待评估电路规模过于庞大导致评估时间大幅增加。如何在设计资源允许的情况下,尽可能提高模拟单粒子翻转效应的故障注入速度,并尽可能确定待评估电路中SEU敏感区位置,是FPGA模拟单粒子翻转效应的重要研究方向。从上述内容可以看出,重配置、扫描链和旁路电路技术假以时日,均能在评估速度、电路开销和定位精度等性能指标上取得进展,使之更适合用于评估超大规模集成电路设计对单粒子翻转效应的敏感性。

-

皮秒脉冲激光技术在AS32S601单粒子效应评估中的应用2025-04-03 1448

-

理解FPGA中的单粒子翻转2023-11-23 5287

-

单粒子翻转效应的FPGA模拟技术 (上)2023-02-09 3067

-

航空电子设计之“单粒子翻转”问题2022-07-13 5608

-

有效容忍单粒子多点翻转的加固锁存器2021-06-03 1001

-

在芯片设计阶段如何防护“单粒子翻转”2020-11-29 8820

-

单粒子翻转引起SRAM型FPGA的故障机理阐述2020-01-26 8269

-

如何对ADC、DAC、PLL进行单粒子翻转容错设计2019-12-17 2403

-

功率MOS器件单粒子栅穿效应的PSPICE模拟2019-07-30 1410

-

高速ADC的单粒子闩锁和瞬态2018-10-31 4263

-

ARINC659总线的单粒子翻转识别2018-01-29 1236

-

反熔丝型FPGA单粒子效应及加固技术研究2016-01-04 678

-

用SOI技术提高CMOSSRAM的抗单粒子翻转能力2010-04-22 2137

-

随机静态存储器低能中子单粒子翻转效应2009-10-31 882

全部0条评论

快来发表一下你的评论吧 !