扩展I2C与DS28E17的通信距离

描述

系统对I2C总线的要求越来越远。本文解释了DS28E17如何用于延长I2C器件的距离,同时降低成本。

介绍

I2C 总线的最大距离取决于容性负载。在典型应用中,标准模式下的长度限制在几米以内。这是因为系统必须适应400pF的最大总线电容,以满足I2C总线规范(2014年4月6日至4日修订版)中列出的上升时间要求。为了通过在最大允许总线电容以上工作来实现更远的距离,I2C 总线规范允许以较低的速度运行,使用较高的驱动输出设备,使用总线缓冲器将总线分成多个段,或使用开关上拉电路。虽然从表面上看,这些方法似乎是可行的,但它们要么不能满足长距离要求,要么会显着增加成本。另一种选择是使用DS28E17 1线至I2C主桥。

安排

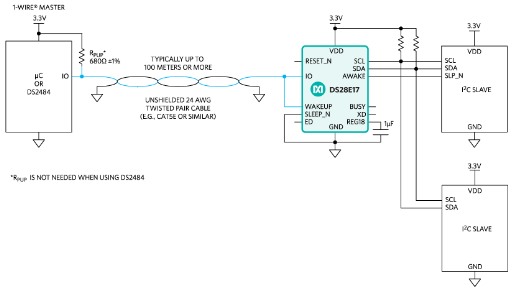

DS28E17 1-Wire--I2C主桥采用不同的方法,采用图1所示的1-Wire®协议。由于协议可以容忍更大的总线电容,因此可以延长距离。1-Wire总线和接地回路采用单导体双绞线,可降低解决方案成本。

图 1.典型应用电路。

考试

通过使用一些简单的电路原理,可以检查图1中的电路总线电容。以下是要采取的基本步骤:

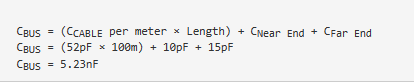

确定系统中每个元件的电容。

每米 CAT5E 电缆电容:52pF/m

近端输入电容(即μC或DS2484):10pF

远端输入电容(DS28E17):15pF计算系统中电缆长度的1-Wire总线总电容。

确定1-Wire主控容性驱动能力(即μC或DS2484)。这需要针对从低到高的转换(即上升沿)来确定,因为这受总线电容的影响最大。高低转换(即下降沿)始终由1-Wire主机以适当的下拉(即~8mA)驱动,通常可以忽略不计。

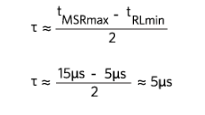

设置时隙时序限制以允许最大上升时间。

tRL= tW1L固件中设置的值:5μs

t星际增长固件中设置的值:15μs

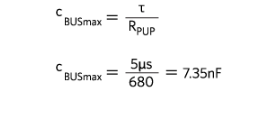

μC 容性驱动能力:

RPUP值:680Ω

确定两个时间常数(VCC的2τ或86.5%)的上升时间。这是由DS28E17对长线路的标准速度读取时隙要求和μC的VIHmax参数(例如,大多数系统通常在VCC x 0.6至VCC x 0.85范围内)设定的。

使用一阶RC电路近似运算可产生μC系统允许的最大容性驱动能力。

DS2484的容性驱动能力更为先进,因为它可以选择使用有源上拉(低阻抗晶体管),在与DS28E17通信时应始终使用该上拉。在台架测试中,结果显示 C总线最大当15-Wire设置为标准速度时,在3.3V时限制为1nF。

验证1-Wire总线电容不超过1-Wire主机的容性驱动能力。

μC 检查:C总线< C总线最大(即 5.23nF < 7.35nF)。

DS2484检查:C总线< C总线最大(即 5.23nF < 15nF)。

调整1-Wire恢复时间(t娱乐) 用于1-Wire主固件中的长线路。

μC 的固件设置为:tREC..FW ≈ 2τ + tRECmin (i.e., 15µs = 2 x 5µs + 5µs).

DS2484的固件设置为:tREC..FW ≈ τ + tRECmin (i.e., 10µs = 5µs + 5µs).

总结

本应用笔记提供了扩展I的替代方法2C总线。它还提供了使用DS28E17在长线路应用中检查总线电容的基本公式和设计理念。

审核编辑:郭婷

CBUS = (CCABLE per meter × Length) + CNear End + CFar End

CBUS = (52pF × 100m) + 10pF + 15pF

CBUS = 5.23nF

CBUS = (CCABLE per meter × Length) + CNear End + CFar End

CBUS = (52pF × 100m) + 10pF + 15pF

CBUS = 5.23nF

CBUS = (CCABLE per meter × Length) + CNear End + CFar End

CBUS = (52pF × 100m) + 10pF + 15pF

CBUS = 5.23nF

-

DS28C16 I2C低电压SHA - 3认证器:安全与性能的完美结合2026-04-01 132

-

基于单片机的I2C总线与AT24C01实验 I2C总线通信原理讲解2023-07-27 5725

-

DS28E18远程I2C和SPI传感器设置指南,内置DS24852023-06-13 3790

-

DS28E18远程I2C和SPI传感器设置指南2023-02-22 2775

-

使用DS28E18的基础知识2023-02-09 2859

-

ESP 12E I2c基卡的I2C IO卡设计2022-08-15 930

-

【蓝桥杯】单片机学习(10)——I2C通信协议与E2PROM2021-11-25 968

-

如何通过DS28E17和微控制器检测100米距离的运动2018-10-11 5259

-

如何使用DS28E17 1线IC扩展IC线路2018-10-09 5849

-

P82B96 I2C扩展器Demo使用简介2010-11-17 1856

-

I2C I/O扩展芯片特性分析2010-07-20 13975

-

P82B715在远距离I2C通信中的应用2010-03-12 2693

-

PCA9698 I2C扩展芯片2009-11-10 1242

-

I2C总线扩展器2009-11-02 774

全部0条评论

快来发表一下你的评论吧 !