什么是CAN总线?-4

描述

在本文中将继续为大家深入讲解信号位采样点位置,波特率偏差,节点容抗和节点数量。

前文内容:

一文读懂CAN总线(一)中:标准CAN和扩展CAN以及CAN消息类型;

一文读懂CAN总线(二)中:CAN总线的位填充机制、错误检测和故障界定、网络拓扑、终端匹配、电缆与接线、差分信号电压幅值。

一文读懂CAN总线(三)中:电缆截面积与通讯距离,波特率、终端匹配电阻与通讯距离,信号延迟与通讯距离和节点最小间距。

信号位采样点位置

信号位采样点是指CAN节点识别一个电平逻辑的位置。CAN标准把总线上的每一位都细分为不同的阶段,如下图所示。

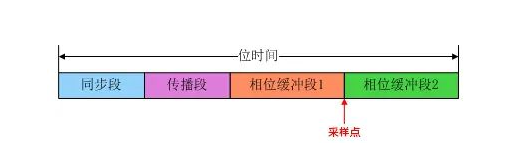

△每一个数据位的分段示意图

在图中可以看到,每个位被分为同步段、传播段、相位缓冲段1和相位缓冲段2四个连续部分。

其中采样点位于相位缓冲段1之后,同步段、传播段、相位缓冲段1和相位缓冲段2的持续时间都是可以编程的,因此采样点位置也是间接可编程的。

一般CAN节点是每个位采样一次(也可以采样3次,多用于低速场合),采样点位置都在一个位的50%以后的区域,这是为了让信号电平趋于稳定。

采样点越靠后,波形越稳定。但也不是越靠后越好,当采样点位置超过95%时,因为传输过程中的位偏差,可能会引起错误。

CIA推荐采样点为一个位时间的87.5%处,实际项目中,一般设置为70%~90%,大部分汽车厂商规定采样点为70~80%。

采样点略靠后,比如80~90%,有利于远距离传输。提高节点波特率寄存器中的同步跳转宽度SJW值(加大到3个单位时间),可以加大位宽度和采样点的容忍度。

波特率偏差

由于受到晶振影响,CAN通讯波特率实际值与理论值会有偏差。如果两个节点之间波特率偏差较大,容易造成误码率增大或通讯失败等问题。

CAN标准规定,设定的理论波特率与实际波特率偏差不得超过±1%;节点需要容忍的波特率偏差不得小于±3%。

节点容抗

在CAN通讯电路设计过程中,节点容抗是容易被忽略的。节点容抗包括收发器引脚电容、PCB走线电容、ESD器件电容以及其它连线电容。

CAN标准对节点容抗有严格定义,容抗影响上升沿下降沿斜率,节点容抗增大,上升沿和下降沿会变缓,导致位时间畸变,误码率增加。上升沿和下降沿变缓会使得信号延迟变大,在高波特率下,影响信号传输质量和通讯距离。

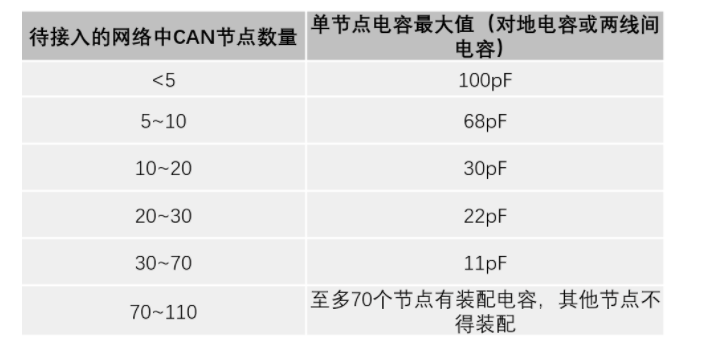

△单节点电容最大值

节点容抗不易测量,需要专门仪器。在电路设计时,要对结合数据手册中给出的典型值,对CAN接口电路使用的器件总电容值进行估算。

对于高波特率情况下,单节点电容推荐<100pF,多节点电容推荐值见上图。低波特率应用可以放宽要求。

节点数量

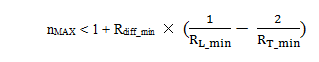

可以连接到网络上的节点数量由收发器可以驱动的最小负载阻抗来决定。最大节点数量由下面的公式给出(考虑最坏情况):

其中:

Rdiff_min:收发器差动输入阻抗最小值

RL_min:收发器可驱动的负载电阻最小值

RT_min:终端匹配电阻最小值

在上式中,收发器差动输入阻抗最小值(Rdiff_min)和收发器可驱动的负载阻抗最小值(RL_min)由收发器芯片决定,终端匹配电阻最小值(RT_min)由传输电缆特性阻抗以及具体应用决定。

-

CAN总线通讯原理-原来这么简单!#总线通讯 #总线传输 #汽车CAN总线 #电路知识安泰小课堂 2025-04-24

-

CAN总线基础知识汇总#CAN #CANoe #汽车总线北汇信息POLELINK 2024-11-04

-

什么是CAN时钟?#CAN #汽车CAN总线 #CANoe北汇信息POLELINK 2024-10-29

-

什么是CAN总线通信?CAN总线工作原理2024-02-19 10514

-

CAN总线访问与仲裁机制#汽车CAN总线北汇信息POLELINK 2023-10-20

-

can总线为什么要用双绞线?can总线不用双绞线可以吗?2023-09-14 7551

-

高速CAN速率 CAN总线位的4段2023-07-25 2904

-

CAN总线的位定时与同步机制#汽车CAN总线北汇信息POLELINK 2023-07-17

-

CAN 总线错误检测机制#can总线北汇信息POLELINK 2023-05-26

-

高速CAN总线和低速CAN总线的特性2023-04-07 4033

-

CAN总线为什么这么火,CAN总线是什么2022-01-15 6507

-

CAN总线多节点通信异常问题解决2019-07-01 6235

-

CAN总线概述及应用_CAN总线的应用案例(汽车CAN总线应用)2018-05-07 36234

全部0条评论

快来发表一下你的评论吧 !