DS2141A、DS2143、DS2151、DS2153与非多路复用总线接口

描述

本应用笔记包含将非多路复用总线处理器连接至以下达拉斯半导体T1或E1成帧器和单芯片收发器(SCT)所需的信息:DS2141A、DS2143、DS2151或DS2153。这些器件最初设计用于与使用多路复用总线配置的处理器接口。通过一些额外的外部逻辑和对软件的微小更改,任何非多路复用处理器都可以连接到这些设备。对设计人员来说,显而易见的好处是处理器的范围更广,能够与这些设备接口。应用笔记包含一张图表,说明了如何将多路复用地址和数据总线连接到处理器独立地址和数据总线。它包含必要的达拉斯半导体总线时序图。最后,它提供了有关如何编写软件的信息,该软件将允许总线接口读取和写入达拉斯半导体器件。目标是为设计人员提供使硬件和软件与设备通信所需的所有信息。

DS2141A、DS2143、DS2151和DS2153包含一些内部电路,使其能够更容易地连接至具有非多路复用地址/数据总线的外部控制器。在DS2141A、DS2143、DS2151和DS2153等多路复用方案中,存在一个信号(通常称为地址选通或地址锁存使能),表示总线上存在有效地址。该信号是必需的,因为地址和数据线共享同一总线。在非多路复用方案中,控制器可能无法提供此信号,因为地址和数据线是分开的。DS2141A、DS2143、DS2151和DS2153包含一些板载电路,如果采用非多路复用总线,可在内部创建地址锁存器。

此内部地址锁存器的创建过程如下。在Intel时序设置中,当DS2141A、DS2143、DS2151和DS2153上的ALE引脚为高电平时,如果WR引脚变为活动电平(即低电平),则地址将锁存于WR的上升沿。在摩托罗拉时序设置中,当AS引脚为高电平而R/W引脚为低电平时,如果DS引脚变为活动电平(即高电平),则地址将锁存于DS的下降沿。

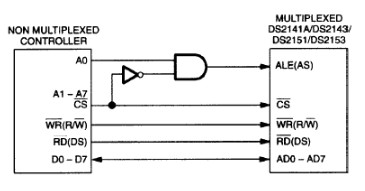

例如,在非多路复用系统中,A0可以连接到ALE(或AS)输入。请参见图 1。DS2141A、DS2143、DS2151和DS2153的每次读取或写入都包含两个操作。要写入DS2141A、DS2143、DS2151和DS2153,控制器首先写入地址,然后写入数据。为了读取DS2141A、DS2143、DS2151和DS2153,控制器首先写入地址,然后读取数据。控制器会将地址视为数据。地址将驻留在奇数字节中,而数据将驻留在偶数字节中。有关计时信息,请参见图 2 至 4。DS2141A、DS2143、DS2151和DS2153数据资料中列出的参数也适用于非多路复用总线工作。

图1.非页面模式内存接口。

图2.非多路复用英特尔读取计时。

图3.非多路复用英特尔写入计时。

图4.非多路复用摩托罗拉计时。

审核编辑:郭婷

-

ds2141a,ds2143,ds2151,ds2153接口的西门子peb20452017-04-10 1034

-

DS2141A , DS2143 , DS2151 , DS2009-04-29 847

-

DS2141A, DS2142, DS2151, DS2152009-04-20 1250

全部0条评论

快来发表一下你的评论吧 !