ADC学习笔记(一)

模拟技术

描述

众所周知,ADC主要用于对模拟信号进行数字采集,以进行数据处理。我们周围的信号一般都是不断变化的模拟量,如光、温度、速度、压力、声音等。然而,我们大多数人都使用数字设备。如果我们想方便地使用和处理信息,就需要将模拟量转换为数字量,并传送到微控制器或微处理器。那么ADC转换是如何实现的呢?这是一个什么样的过程?阅读下面的笔记,你一定会对模数转换器有更全面、更系统的了解。

在电子信息系统的学习中,我们或许早就被告知现实世界是模拟的,而数字化的模拟世界则越来越展现更多的风采。但是所谓的数字和模拟只是相对的而已,你可以把模拟量当做无穷数字量的组合,也可以把数字量当做具有不同间隔特征的模拟量。这模数之间的差别也就是采样和量化的差别而已!

那么Analog如何才能走到Digital呢?

一、ADC几个步骤

1、采样和保持

如果把模拟信号比作无限采样点的数字信号,那么我们就需要采取其中一些有限点才能进行真正的数字化传输。采多少点?怎么采?

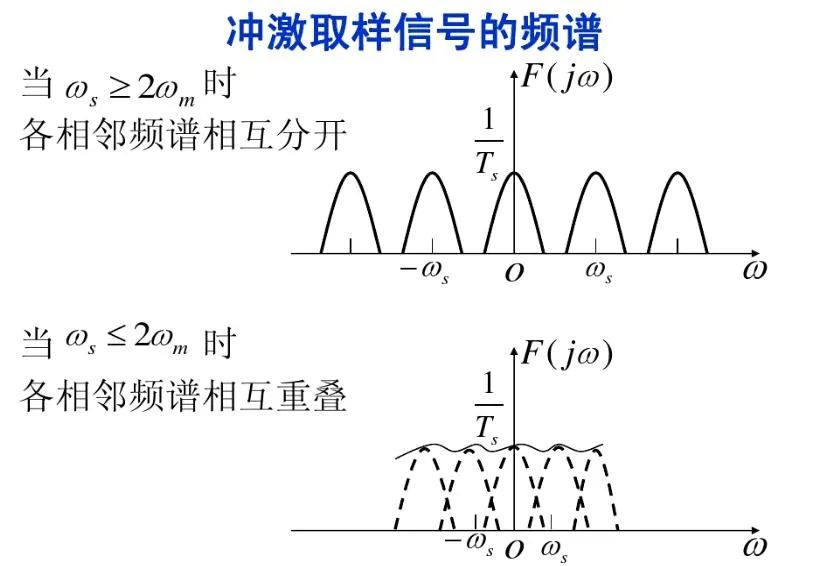

奈奎斯特(Nyquist)采样定理:

简单来说就是采样频率必须大于信号频率的2倍,fs≥2fn。这样才能重新恢复信号。如果不,会因为频谱混叠而无法复原,具体原因自行查找公式推导及分析。如下图频谱

保持的意思简单理解就是让采样后的数值保存到下一步转换。

2、量化和编码

所谓的量化是把采样后的N多个点数值按照一定标准和步骤转化为数字式的0和1,这个过程根据方式的不同可以分为很多种ADC类型,因此具有不同的性能特性,见下文。

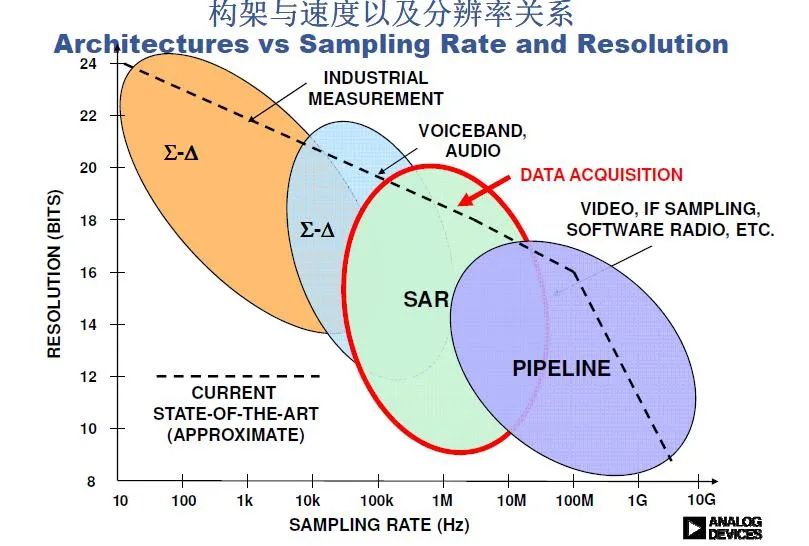

二、ADC的几种架构

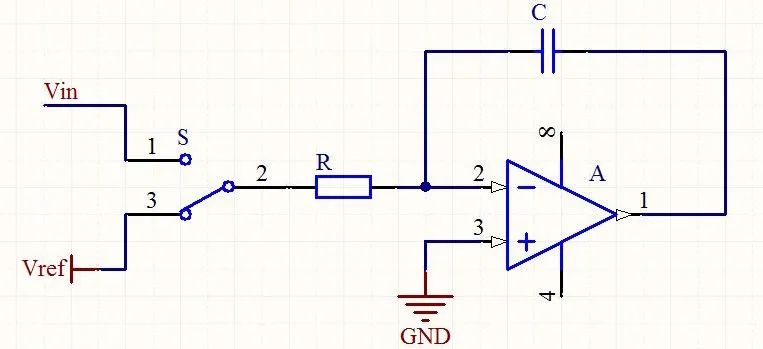

1、积分型ADC

顾名思义,积分ADC的基本原理就是利用运放对输入信号和参考信号进行积分输出,这里参考信号一般与输入信号极性相反,这样输出电压就会有上升时间和下降时间,根据计数器来统计时间,最后按照函数关系得到采样信号的值。

特征简介:

A:积分时间决定转换精度,因此牺牲转换速度可以提升精度,在早期的一些仪表转换精度要求不高的场合应用,后来的ADC很少采用这种架构了。

B:抗噪声能力强。对于零点正负的白噪声,积分时可以消除。

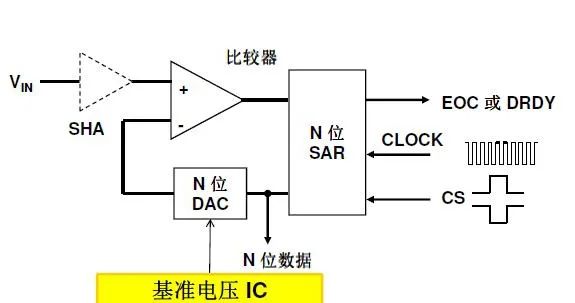

2、逐次比较型SAR

顾名思义是利用比较的方式来转换输出数字量,这个用来比较的值由DAC产生,如下图:初始化DAC的输出由寄存器设置为1/2Vref,然后由比较器判断大小来决定输出1或0,进而进行下一步再次设置寄存器输出DAC,如此循环到最后一次LSB。依次输出的0和1即为转换后的数字量。算法核心就是二分法搜索,类似于猜数字值的游戏。

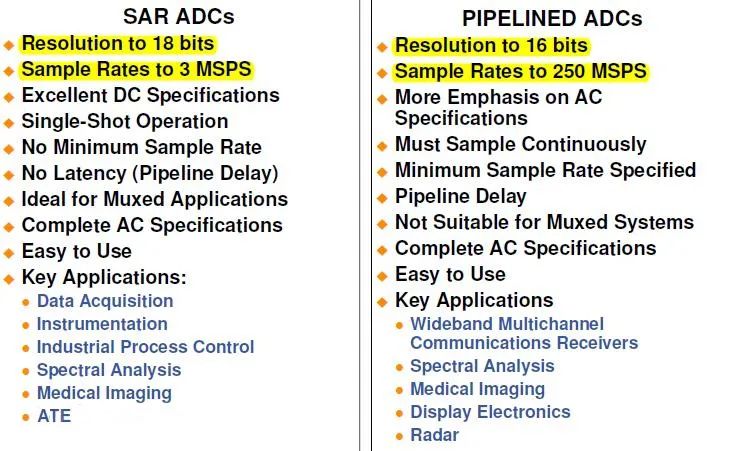

特征简介:

A:100K到1M的中等速度,12到16位的中等精度,综合性能较好,因此是目前应用最多的ADC架构之一。

B:精度主要决定于DAC的转换精度,因此DAC需要校准,比较器也需要满足高速和能够匹配系统的较高精度。

C:功耗可调,由转换速度决定,因此也限制了高速应用。

D:总之SAR型ADC的内部各组成模块需要组合设计性能匹配最优。

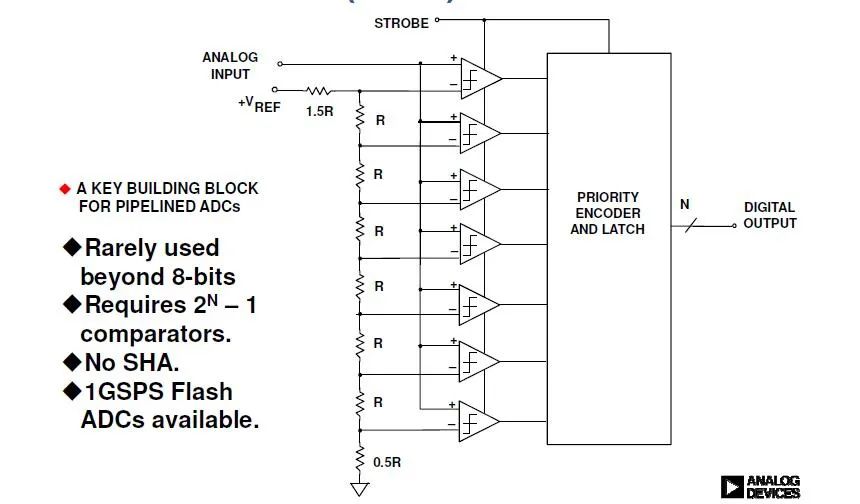

3、Pipeline流水线型ADC

基本原理如图,利用多个比较器进行并行处理,很明显,高速!

特征简介:

A:很明显够快,比较器并行处理。

B:功耗大,面积大,自然是因为比较器多。

C:分辨率不够,也是因为功耗大,多数小于16位。

D:转换周期需要不断校准以保证一定精度。

两种ADC架构的比较:

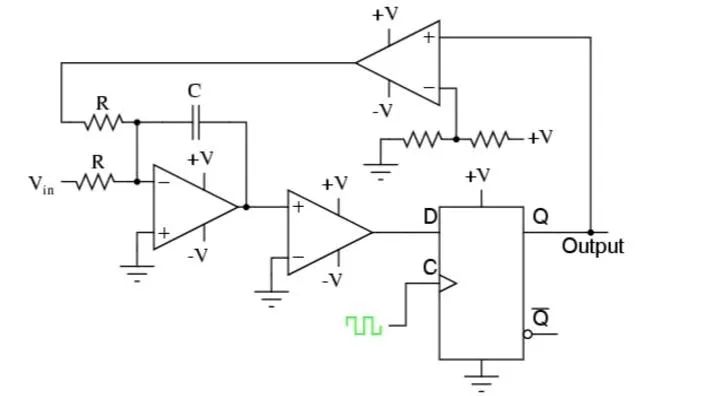

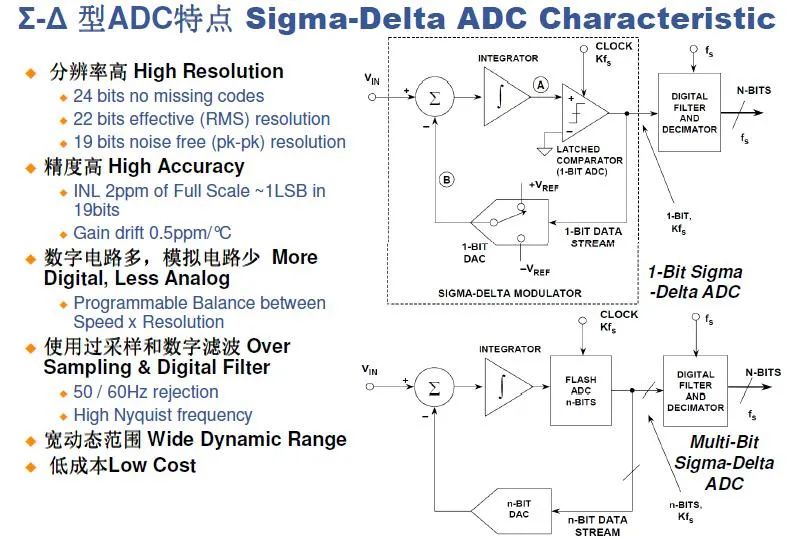

4、Σ-Δ型ADC

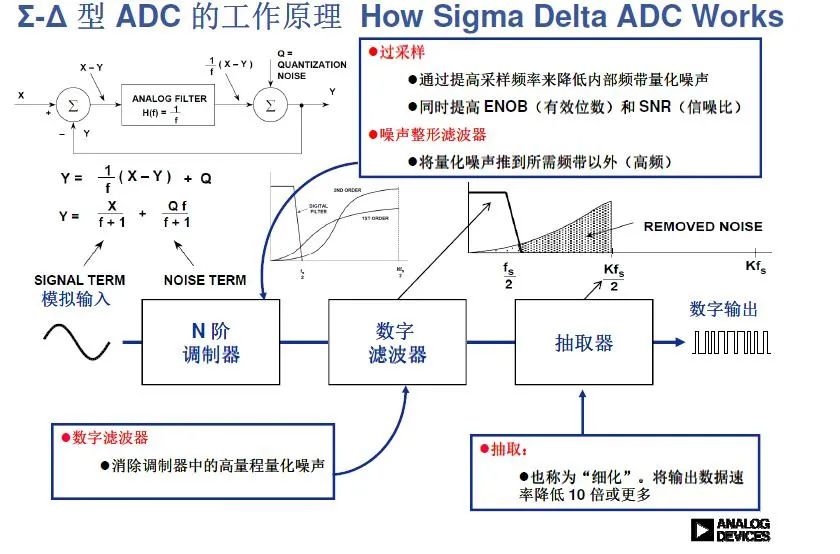

Sigma-Delta 型ADC也是目前应用相当多的一种ADC架构,尤其是在高位数分辨率的ADC设计上,这种调制型的ADC转换设计尽可能采用数字电路来处理并结合算法实现更好的性能。核心技术点:过采样和噪声整形。

Sigma-Delta调制过采样:

如图,sigma-delta的意思是差分求和,我们来顾名思义一下这个过程:

假设第一个积分运放输出1,则到后面Q输出也为1,第二个运放输出则为+V。

+V反馈到第一个运放输入,驱动积分器向反方向输出,待采集信号Vi也会驱动积分器输出,综合而言如果积分器输出为0,第二个比较器反馈回来的就是-V,以驱动积分器向输出。这个环路最后的目的是实现运放的基本特性:反相端应该为0!

这样整个输出的1的个数比例对应的电压值其实就是待测信号的电压值!能否理解?就是通过对误差的不断累积求和得到对应值!Q会输出一串01值即完成。

过采样:

上述过程中的触发器时钟非常快,远大于奈奎斯特采样要求,这样可以将量化噪声推到更高频段内。量化噪声:数字量化的最小单位存在的误差被称为量化噪声,即1LSB和2LSB之间的误差值。

噪声整形:

前一步得到的高速01数字流可以通过数字方式进行处理得到最后的输出结果。因为在过采样过程中是以速度换取精度的方式来操作的,高速但是噪声大,在噪声整形过程中通过数字滤波器和抽取电路把噪声消除并降低最终的信号输出速率,实现高精度的数据转换结果!

如下图总结:

几种ADC架构的简单比较:

大家在学习ADC的过程中一定有很多问题,我这边也总结了一些学习中遇到的问题,现在分享给大家,希望能从中学习到一些有用的知识。

Q1

设计一个电路是怎么样的一个过程啊?如何从架构开始一步一步到满足性能要求的电路来? 特别是各管子的参数是靠手算出来的还是工具仿真出来的?

先初步手算的 然后仿真精细化。比如BGR,先确定电流、功耗、输出电压等基本指标,然后选择电路结构,再进行手算。有了初步参数,就可以仿了,然后再调。设计的尺寸还要看工艺和版图的可行性

Q2

同步sar逻辑和异步的区别是什么呢?哪个更好一些?

同步SAR更多是应用于低速,一般采样率不会超过5MHz,而且高速时钟需要外灌溉;异步SAR可以做到很高速,对于40nm这种工艺,单通道可以到100MHz左右,如果是Finfet工艺,可以更高。由于异步SAR ADC在面积和功耗上远远优于pipelined ADC,在精度要求不是太高的应用领域(不超过10Bit),异步SAR可以代替pipeline了。

Q3

计算SNR的时候,谐波功率也算到噪声功率吗?计算ENOB用的是SNR还是SNDR?

是信号和其他所有比,当然这个也要看定义,有的地方把snr和sndr区分开,sndr是信号比谐波+噪声,snr就是信号比噪声了。事实上大家大部分情况下说的snr就是sndr,不特别强调的话,习惯性默认snr就是sndr。就是说通常说snr是加上了谐波失真的sndr,而不是仅用enob公式算出来的snr。

Q4

对怎么做一些屏蔽,隔离,匹配,floorplan等等能不能给说一说,因为毕竟我们要跑的频率还不低呢。

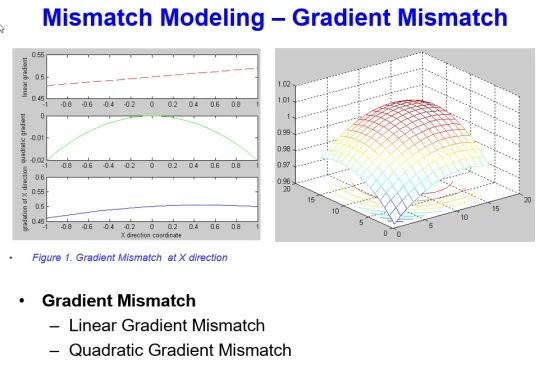

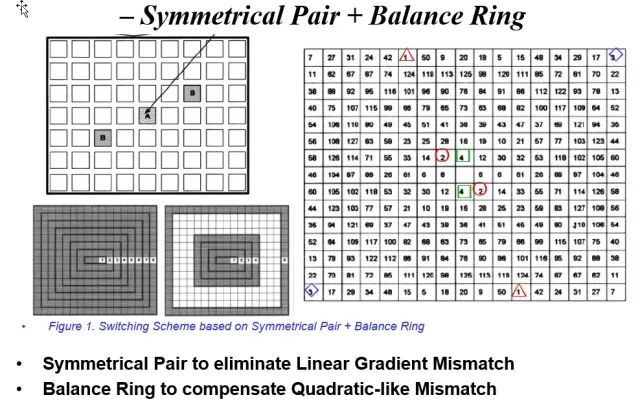

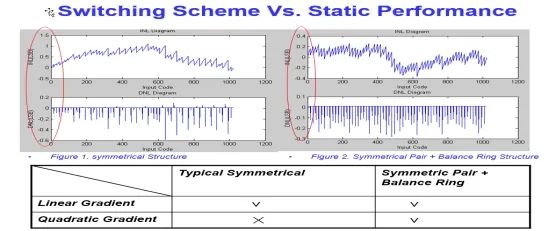

说白了就是DAC的布局布线,这可以是一个专门的Topic。我们通常所说的中心对称图形其实大部分只能消除一阶的系统失配,但是一不小心就可能放大高阶失配。涉及到我们SAR ADC里面的CDAC,要分情况来讨论,如果是低速的高精度SAR ADC,由于速度低,我们的CDAC可以采用很多方式来消除系统失配。但是对于高速SAR ADC,一个电容拆分的越散,虽然系统匹配越好,但是布线越复杂,寄生效应越明显,对速度的影响越大。我在做100MHz采样率这种数量级的SAR ADC的时候,我们的总电容其实都不大的,LSB电容不足1fF,整个SAR ADC的面积也很小,具体到CDAC,也就100*100左右。我们会更多地从速度的角度触发,MSB电容做一些拆分散开,其他电容以layout优先,layout舒服了,电路性能才能上去。这里有几张关于DAC Layout的图给大家看看,大概需要考虑到哪个程度。

一阶线性匹配和高阶非线性失配都要考虑,最终layout布局要能消除或者减弱所有mismatch。

类似的有Q^2随机游走式布局。

平衡环的方式,目的就是要将DAC的器件单元完全打散,消除一阶和高阶系统mismatch,最终的目的都是为了在恶劣的环境下实现较低的INL。

Q5

仿单级放大器是应该去跑仿真仿瞬态仿真合适还是交流仿幅频特性曲线合适?

不矛盾,这两都需要跑,或者是需要跑哪些仿真得看实际需求。AC或者STB是得到幅频特性,诸如低频增益、GBW、稳定相关的PM和GM等这些参数。但是AC毕竟只是基于某个特定工作点的电路性能,实际中OP的输出输入都是有一定范围的,工作点偏了OP性能肯定也会发生改变,跑Tran,对Tran波形做DFT就能够知道信号的质量,DFT是对OP输出信号的线性度进行定量计算,反映了不同工作点情况下的OP性能参数变化(增益的变化、GBW的变化等)。

Q6

我在想是不是我不做太高速的,可以不用太在意这个频域的东西?因为我们是挂在MCU上的一个模块,万一不行,我就让他们软件多给点时间去采结果。

大家先看DFT谱线图的物理意义很重要,从不懂到似懂非懂再到明白,总要有个过程,该经历的痛苦要经历的。事实上工作好多年不会用DFT分析信号线性度的大有人在,这种情况下就比较被动了,每次要请人帮忙搭建仿真Bench,关键是仿完心里还底气不足。你们学完能有个似懂非懂的状态就差不多了,答疑的时候我再帮大家梳理一遍,从似懂非懂到明白也就是一线之隔,一瞬间的事儿。

Q7

其实我对归一化,dB的意思也没理解透。

谱线的Y轴是dB就是说这根谱线的功率吧,这个能理解。

这里的功率,是指某信号在某点的电流电压积么?

高考,各地的满分不一样,假设湖北满分750,上海满分600。现在分别有2个学生A和B,A是湖北考生,B是上海考生,A考了600分,B考了500分,我们怎么来判断他们谁的成绩更好呢?单单比较分值的绝对值没有意义,我们把总分归一化到100分上来,A=600/750100=80分,B=500/600100=83.3分,简单来说B成绩更好。这就是归一化,以统一的标准来衡量。

Q8

我感觉明明简单的一个误差指标,但是却要搞出这么多分散的指标来表达这个误差,太晕了,ADC判断误差,这个看起来觉得应该好理解,就是搞出各种误差指标,这下就难理解了

对信号归一化的意思是,所有频谱对应的功率值都除以信号功率值,由于纵坐标已经变成了log轴,所以直接减法就行。

20log10(A/B)=20log10(A) - 20*log10(B)

在DFT频谱里面,信号功率是最大值,对应着考试的满分,对信号归一化就是对满分归一化。

Q9

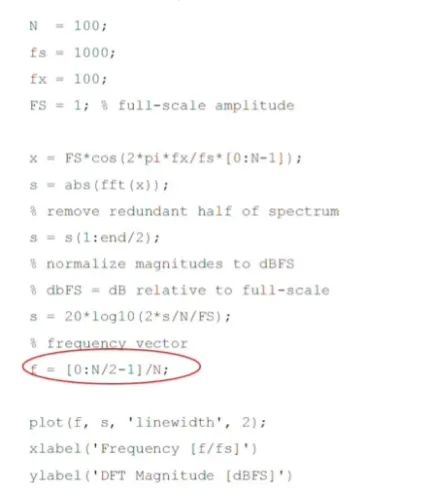

s=20log10(2s/N/FS); 对数里面2*s/N/FS什么意思?

好问题,你发现了程序里的一个小bug。

Q9.1

直接log10(s),不对吗?

2s/N/fs=s(2/N/fs),其中2/N/fs是一个常数。我们关注FFT的结果只关注信号和谐波以及噪声之间的相对差值,所以所有的s元素都乘以一个常数是不影响结果的。

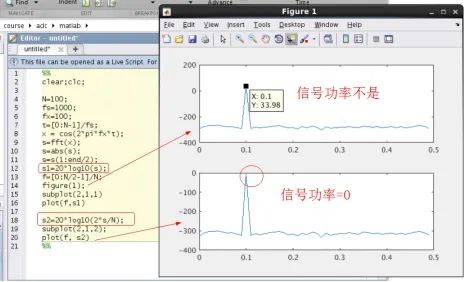

但是这里的归一化确实不对,s是fft结果,如何对s进行归一化呢?最简单粗暴的方法是 log之后 s=s-max(s)。

如果按照DFT的理论公式,归一化的方法应该是2s/N,为什么要2呢?我们在此之前只取了N/2个点,丢了一半,这里的2是补那一半回来。为什么/N呢?因为时域采了N个点,对应频域也是N个点,/N的意思是求平均。

所以这里的代码里多了一项/fs,正确的应该是s=20log10(2s/N)

从这个图你们应该能看的更清楚,第一章图的FFT结果没有对信号进行归一化,信号的值不为0,第二张图仅仅是对信号进行了归一化,信号显示为0,噪底整体下移。

如果看不懂就略过,毕竟是乘以一个常数。我建议你们以后归一化就直接 s = s-max(s),简单粗暴好理解。

-

STM32Cube学习笔记2023-09-20 632

-

AN003 ADC 应用笔记2023-02-27 646

-

ADC学习笔记(二)2023-02-09 3025

-

C语言和STM32学习的一些学习笔记2022-03-24 1271

-

学习一下S32K3的ADC模块2022-03-01 4059

-

ESP32 单片机学习笔记 - 04 - ADC和定时器2022-01-17 923

-

嵌入式知识-ARM裸机-学习笔记(12):ADC模数转换器2021-12-22 875

-

STM32 ADC 学习笔记2021-11-30 981

-

STM32学习笔记一、 IO模拟串行通讯2021-11-29 1014

-

【学习笔记】单片机汇编学习2021-11-14 1091

-

STM32的ADC学习历程2021-09-27 2140

-

Altera FPGA CPLD学习笔记2021-09-18 1670

全部0条评论

快来发表一下你的评论吧 !