解析一些常见的寄存器

电子说

描述

现代CPU内部除了 运算器和控制器, 还有一个常见的组件: 寄存器 ,是CPU内部用来存放数据的一些小型的存储区域,用来暂时存放参与运算的数据以及运算结果。我们了解了计算机各个硬件读写速度的差异,其中从存储器速度、容量和价格的关系金字塔图发现:最上层的寄存器速度最快,容量最小,价格也最昂贵

下面我们来看看几个常见寄存器:

数据寄存器(DR)

数据寄存器(Data Register,DR)又称数据缓冲寄存器,数据寄存器用于存放操作数,其位数应满足多数数据类型的数值范围,其主要功能是作为CPU和主存、外设之间信息传输的中转站,用以弥补CPU和主存、外设之间操作速度上的差异。

数据寄存器用来暂时存放由主存储器读出的一条指令或一个数据字;反之,当向主存存入一条指令或一个数据字时,也将它们暂时存放在数据寄存器中。

数据寄存器的作用是 :

- 作为CPU和主存、外围设备之间信息传送的中转站;

- 弥补CPU和主存、外围设备之间在操作速度上的差异;

- 在单累加器结构的运算器中,数据寄存器还可兼作操作数寄存器。

地址寄存器(AR)

地址寄存器(Address Register,AR)用来保存CPU当前所访问的主存单元的地址。其本身可以具有通用性,也可用于特殊的寻址方式,如用于基址寻址的段指针(存放基地址)、用于变址寻址的变址寄存器和用于堆栈寻址的栈指针。地址寄存器的位数必须足够长,以满足最大的地址范围。

由于在主存和CPU之间存在操作速度上的差异,所以必须使用地址寄存器来暂时保存主存的地址信息,直到主存的存取操作完成为止。

程序状态寄存器(PSW)

程序状态寄存器(PSW),用来保存各类运算指令或测试指令的结果的各种状态信息 除此之外,程序状态字寄存器还用来保存中断和系统工作状态等信息,以便CPU和系统及时了解机器运行状态和程序运行状态。程序状态寄存器 是构成 运算器的重要组成部分

累加寄存器(AC)

累加寄存器通常简称累加器(AC),是一个通用寄存器。

累加器的功能是:当运算器的算术逻辑单元ALU执行算术或逻辑运算时,为ALU提供一个工作区,可以为ALU暂时保存一个操作数或运算结果。显然,运算器中至少要有一个累加寄存器。

乘商寄存器(MQ)

在运算器中,乘商寄存器主要负责数据的乘法与除法运算并可保存运算结果,是运算器的基本组成部分,是运算器三个基本寄存器之一。

程序计数器(PC)

程序计数器(PC),具有寄存信息和计数两种功能,一般用来 存放下一条指令在主存储器中的地址 。

在程序执行之前,首先必须将程序的首地址,即程序第一条指令所在主存单元的地址送入PC,因此PC的内容即是从主存提取的第一条指令的地址。

当执行指令时,CPU能自动递增PC的内容,使其始终保存将要执行的下一条指令的主存地址,为取下一条指令做好准备。但是,当遇到转移指令时,下一条指令的地址将由转移指令的地址码字段来指定,而不是像通常的那样通过顺序递增PC的内容来取得。

指令寄存器(IR)

指令寄存器(Instruction Register,IR), 用来保存当前欲执行的指令 。

当执行一条指令时,首先把该指令从主存读取到数据寄存器中,然后再传送至指令寄存器。

指令包括操作码和地址码两个字段,为了执行指令,必须对操作码进行测试,识别出所要求的操作,指令译码器 就是完成这项工作的。指令译码器对指令寄存器的操作码部分进行译码,以产生指令所要求操作的控制电位,并将其送到微操作控制线路上,在时序部件定时信号的作用下,产生具体的操作控制信号。

指令寄存器中操作码字段的输出就是指令译码器的输入。操作码一经译码,即可向操作控制器发出具体操作的特定信号。

MAR、MDR

另外寄存器不只存在CPU中,存储器中也存在寄存器,比如MAR、MDR

- MAR:存储器地址寄存器,用于存放将被访问的存储单元的地址。作用和AR类似

- MDR:存储器数据寄存器,用于存放欲存入存储器中的数据或最近从存储器中读出的数据。作用和DR类似

其中MAR位数反映储存单元的个数,即最多能表示多少个不同的状态;MDR位数=储存字长=每个储存单元的大小

小结

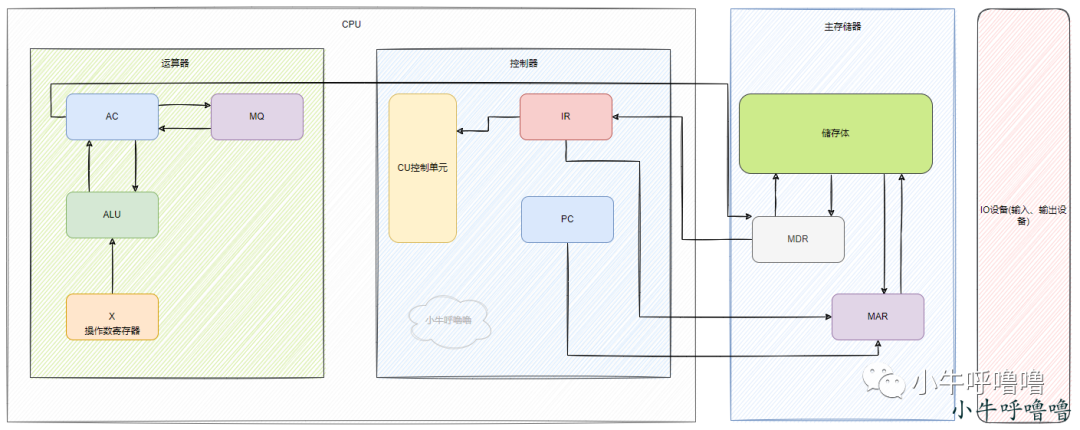

将上面各个寄存器组合起来,我们可以画出一幅计算机更细化的组成图:

当存储器开始读操作的时候,存储器将指定地址单元内的指令读至MDR,再由MDR送至IR。IR将指令中的操作码送到CU中,用来分析指令并发出各种微操作命令序列。再加指令中地址码送到MAR,用来去操作数

在CPU内部必须给ALU提供数据,因此ALU必须可直接访问MDR,ALU的外围还可以有另一些寄存器AC、MQ、X,这些寄存器用于ALU的输入、输出以及用于和MDR及用户可见寄存器交换数据。

在CPU的控制和状态寄存器中,还有用来存放程序状态字PSW的寄存器,该寄存器用来存放条件码和其他状态信息。在具有中断系统的机器中还有中断标记寄存器等等。

-

labview读取三菱plc寄存器内容2023-12-27 4504

-

芯片DFX:Coresight的寄存器一览2023-11-02 2587

-

基于DWC2的USB驱动开发-DOEP接收相关的DMA寄存器详解2023-07-19 2958

-

解析CPU中的寄存器2022-09-19 5250

-

如何在VHDL中实现一个简单的寄存器2022-07-29 5575

-

寄存器组CM3拥有通用寄存器组和一些特殊寄存器2021-12-16 1055

-

寄存器、锁存器和触发器三者对比2021-04-14 5375

-

51单片机的一些特殊寄存器资料说明2019-07-26 1462

-

开发一个Linux调试器就必须要知道寄存器和内存!2019-05-14 1981

-

基于stm32的GPIO寄存器学习解析2018-01-11 14136

-

寄存器与移位寄存器2016-05-20 1298

-

CSD寄存器解析2016-01-06 1057

-

ARM寄存器详解2010-07-10 3306

-

寄存器,寄存器是什么意思2010-03-08 22414

全部0条评论

快来发表一下你的评论吧 !