如何处理挠性电路,适应不同系统间的在线传送带传输?

描述

将表面贴装元件直接集成到挠性电路的蚀刻铜焊盘图形上,与刚性电路板的组装工艺没有什么不同。然而为了最大限度地提高机器人组装效率,提高挠性电路的产量,电路设计工程师需要提供一种格式,以支持在线组装工艺所需的所有特征。

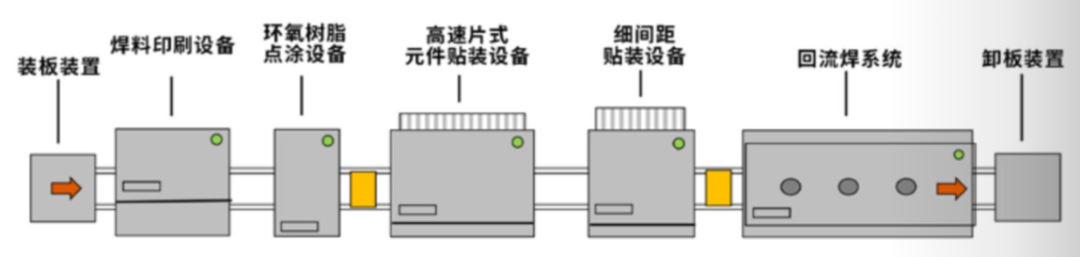

表面贴装组装有3个主要工艺阶段:焊膏沉积、元器件放置和回流焊工艺。为了最大限度地提高制造效率,为完成这些功能而开发的自动化系统均被设计为能够适应不同系统间的在线传送带传输(图1)。

图1:传送带式SMT组装生产线基本配置

传送带系统虽然可调节,但至少需要两个平行的边缘来支撑电路,将其从一台设备传送到另一台设备。虽然针对传送带传送设定刚性电路板较容易,但在批量生产环境中加工挠性材料需要在组装过程的每个阶段为薄膜电路提供支撑。对于中低批量应用,可准备符合输送带要求的拼托板夹具,以在组装的每个阶段固定单个挠性电路;而要求大批量组装工艺的产品则需要更有效的解决方案。

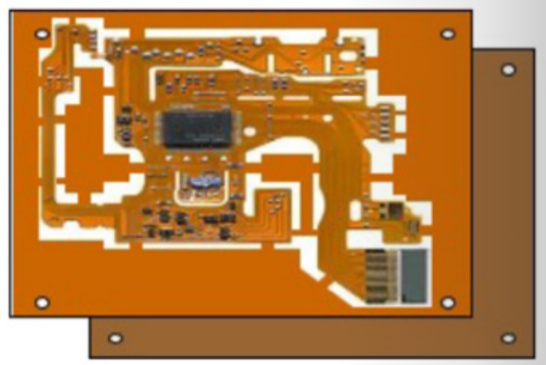

为了更好地适应传送带的操作,挠性电路可以由电路制造商提供临时的刚性载体拼板支撑。图2展示了具有较复杂外轮廓的单个挠性电路组件。如果没有刚性支撑材料和专用的、针对于产品的载体拼托板夹具,精密的焊膏沉积和元件放置将是不可能的。

图2:固定于统一拼板格式内的挠性电路

制造公司已经为拼板布局开发了广泛的解决方案,以促进高效操作,支撑组装工艺中各种外形的电路:

单个单元格式(中、大型电路)

多单元阵列格式(行和列布局)

嵌套阵列格式(最大化面积利用率)

在处理小外形挠性电路时,多单元阵列格式已被证明既高效又经济。

拼板挠性电路

为挠性电路应用开发的载体拼板被设计用于提供传送带所需的统一、刚性板轮廓,在每个组装工艺中为挠性电路提供物理支撑。为了固定单个单元和多个单元挠性电路,设计师需要提供类似于小接线片的连接特征。为了提供能将挠性材料连接到载体拼板轮廓的区域,挠性基底材料需要向外延伸以匹配载体拼板轮廓。将挠性材料连接到刚性载体拼板的粘合膜必须保持不接触挠性电路轮廓。

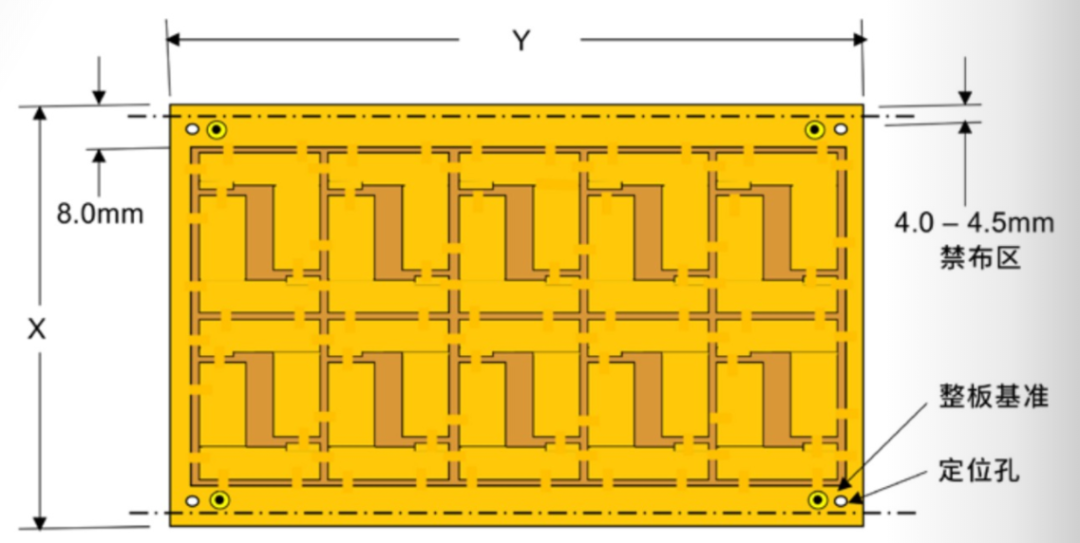

图3所示的多单元拼板案例代表了为最大化小型、不规则形状挠性电路单元的材料利用率而设计的一组单元。此案例图示为以相反朝向或“嵌套”阵列格式排列的挠性电路单元。

图3:相反朝向阵列格式

自动化组装所需的关键特性

支撑拼板必须包括以下几个关键属性:

承载拼板的边缘间隙能够无障碍地进入输送带支撑带。

挠性电路单元的外部需要设置两个或更多的工装孔,以在组装后的分离过程中固定拼板。

在焊膏沉积过程中,需要在拼板边缘区域附近放置相同数量的“整板基准目标”,以帮助拼板对准。

焊膏沉积系统使用相机来精确定位基准目标,使焊膏模板精确对准拼板中央区域内单个电路单元上的焊盘图形特征。

除了整板定位的基准特征外,在元器件安装区域内还需要两个或更多的基准,以便精密自动化元器件的放置。在SMT元器件放置区域内使用多个基准特征将可最大限度地减少挠性材料中的可变收缩或任何工艺变形的影响。

图4是挠性电路的实例,其中SMT元器件贴装在两个区域内,由狭窄的互连段分开。多个基准位置将在每个基准区或端接区域内提供更严格的公差,同时减少对保持其他元件端接区域之间挠性接口部分限定公差的需要。

图4:两个元器件贴装区的基准目标位置

基准目标设计规范

最佳基准目标是没有表面涂层或覆盖层材料的实心圆铜。必须调整基准周围的涂层和覆盖层薄膜材料开口,以在基准周围提供足够的间隙,确保在覆盖层与基本电路层压过程中不会重叠到基准目标特征上。

最佳基准是直径0.25~ 0.50mm(~0.010’~ 0.020’)的实心圆焊盘图形。

为了能够目测定位基准目标,阻焊膜或覆盖涂层必须提供为2倍于基准R的间隙。

基准位置必须与拼板或电路轮廓边缘保持至少4.75 mm(~0.187’)的距离,并提供一致的高对比度。

蚀刻后的铜基准表面无需电镀,但如果控制文件中规定在基铜上进行二次合金电镀,则设计师必须确保基准表面的平整度保持在0.015 mm(0.006’)以内。

最后的建议

为拼板加工规划多个单元电路时,挠性电路设计师应在负责组装工艺的人员与指定制造电路的制造商之间协调最终拼板尺寸和单元结构。

审核编辑:汤梓红

-

#电工 传送带模块jf_09391732 2023-02-18

-

如何用Labview做传送带动画2014-06-05 4582

-

挠性电路的特性及优点2018-08-30 2646

-

怎样去设计基于单片机的传送带计数系统2021-11-25 900

-

如何实现单片机货物传送带检测设计2022-01-19 1026

-

通过YMD系列超级节能变频器实现传送带的节能设计2018-10-25 3272

-

橡胶传送带破损划伤可以修复再使用吗2021-03-23 1331

-

详解非直线传送带动态跟踪技术2021-04-22 2834

-

26-基于单片机的传送带计数系统2021-11-17 669

-

传送带产品计数器系统设计方案2022-05-05 2238

-

矿山传送带导向辊轴承位磨损的修复指南2022-09-23 503

-

西门子1200PLC 传送带控制程序编写及思路2023-03-30 6262

-

STL检测传送带传送方向的示例2023-08-12 1718

-

博途:使用STL函数控制传送带2023-10-12 3607

-

英国真尚有非接触测速传感器LP-DS100传送带速度测量2025-02-26 714

全部0条评论

快来发表一下你的评论吧 !