免调节中频VCO:设计考虑

描述

本文力图探索实现一个免调节、固定频率的中频(IF)压控振荡器(VCO)所需了解的基本设计原理,同时指出保证电路正常工作所需面临的挑战。在多数无线系统的架构中,VCO都是一个关键部件。两次变换系统需要一个固定频率的IF VCO,用来控制中频到基带和/或基带到中频的频率转换。

全文由两部分组成,前一部分力图探索实现一个免调节、固定频率的中频压控振荡器(VCO)所需了解的基本设计原理,同时指出保证电路正常工作所需面临的挑战。在多数无线系统的架构中,VCO都是一个关键部件。两次变换系统需要一个固定频率的IF VCO,用来控制中频到基带和/或基带到中频的频率转换。

两次变换系统需要两个振荡器。典型地,第一个振荡器(RF VCO)可在整个输入波段内调谐,第二个振荡器(IF VCO)工作在预先设定好的单一频率下。RF VCO有现成的模块、IC或分立元件电路可用,以模块或IC更为普遍。而就IF VCO来讲,小体积、低成本的模块几乎无法从市场上找到。这可能是由于中频频率的多变性以及制造过程中无法进行激光微调(调节)的大数值电感所致。因此,IF VCO常常采用分立电路或部分IC的方式实现。

为此,Maxim首创了一种全新概念的VCO IC,应用于无线系统正好可以弥补其他板级RF/IF IC在这项功能上的不足。本文的第二部分将介绍这种IC及其开发情况,并详细阐述它所能实现的简单、价廉的应用。

分立元件VCO能够提供足够的自由度来满足大多数系统的性能要求(调谐范围、输出功率、相位噪声、电流消耗、成本等等)。然而,对于具有较大批量、价格敏感的现代产品,震荡频率的生产线调整是不可接受的。这迫使RF工程师必须设计出一个不需要在安装过程中调整的VCO,即免调整VCO。这项设计任务并不简单,除了要掌握VCO的基本设计原理外,还需要RF工程师花费大量精力来保证设计的一致性,而且在各种变化因素(如元件参数、温度及电源电压等)允许的改变范围内,振荡器始终调谐在正确的频率。下面的讨论试图对这项任务的重要性给出一个评价,同时解释一些和免调节中频VCO设计有关的问题。

VCO拓扑

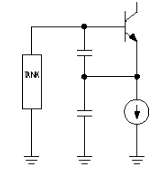

有多种可行的振荡器拓扑都可用于构建一个实用的RF VCO,其中一种已经在许多商品化VCO模块和不计其数的分立VCO电路中得到了成功应用,这就是Colpitts共集电极拓扑(图1)。该拓扑可用于很宽的工作频率范围,从IF直到RF。

图1. 基本Colpitts振荡器

一个灵活、廉价、并具有足够高性能的VCO可基于一个由廉价的表贴电感和变容二极管组成的电感-电容(LC)谐振槽路组成。振荡器槽路是一个并联谐振电路,控制着振荡频率,电感或电容的任何变化都会改变振荡频率。电感和压变电容可以并联或串联模式的网络形式实现可变谐振。

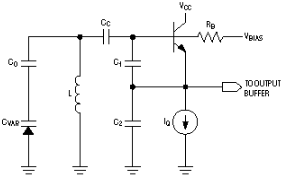

并联模式网络可用于较低频率,因为大值压变电容难以实现而电感可以做得比较大。并联模式配置还便于对振荡器做直观地分析。在本文余下的篇幅中,借助并联模式LC槽路的Colpitts振荡器对免调节IF VCO的设计进行阐述(图2)。

图2. Colpitts拓扑用于VCO

Colpitts振荡器在很多教科书中都有论述(Clarke和Hess 1978,Hayward 1994,Rohde 1998),并已推导出一些通用的和专用于Colpitts拓扑的方程,可用来描述振荡器的工作机理。振荡器在电路中被抽象为一个反馈放大器模型。精确的振荡频率表达可通过此模型中阻抗的平衡而得到,但所得表达式往往很复杂且无助于振荡器的设计。

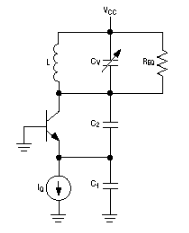

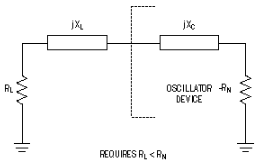

另一方面,对于Colpitts振荡器可以采用一种简化的、精确性稍差的方法来加以分析,并得到一组更清晰、更直观的设计方程,非常有助于一阶振荡器的设计。首先,Colpitts振荡器可重画为一个带有正反馈的LC放大器(图3)。这个视点易于计算环路增益、振荡幅度和相位噪声。为了描述启动过程和振荡频率,最初的电路也可重画为一个负阻加谐振器结构(图4)。从上述两个视点得到的一系列方程联合起来构成一组Colpitts振荡器的设计方程(Meyer 1998)。

图3. LC放大器模型

图4. 映像放大器模型

Colpitts振荡器的基本设计方程

不考虑分布参数,并假定CC 》 C1和C2和C1 》 Cπ (Cπ 为三极管基-射结电容)。振荡频率可按下式计算:

谐振电路的品质因数(QT)可按下式计算:

振荡幅度可按下式估算:

环路增益和起振条件按下式计算:

距离中心频率一定频偏(fm)处Colpitts振荡器的相位噪声(PN)可按下式计算:

免调节VCO的设计考虑

免调节VCO从概念上讲非常简单。只要振荡器具有足够宽裕的调谐范围来消除所有的误差源(如元件容差)所引起的频率偏移,振荡频率的调整就可以省去。初看起来,这项任务非常简单明了,只需提供足够的调谐范围来覆盖所有的误差源即可。然而,对于一个给定的调谐电压范围,有限的可变电容限制了频率调谐范围,而且,VCO的电性能要求往往进一步将调谐范围限制在更窄的区间内。

不幸的是,过大的调谐范围还会给振荡器带来一些负面影响。很宽的调谐范围要求压变电容至槽路间有很重的容性耦合,这会严重降低谐振电路的品质因数Q。所带来的结果便是更大的相位噪声(谐振幅度与晶体管噪声之比降低);对调谐线噪声更高的灵敏度(这将直接转换为频率调制);压变电容两端过大的电压摆幅;潜在的启动问题;以及给环路滤波器设计带来很大的困难等。这些因素导致的结论就是,过量的调谐范围不受欢迎。事实上,它不应大于吸收所有误差因素的最低需要。

| Glossary |

| CO = varactor coupling capacitance |

| CT = total tank capacitance |

| CVAR = varactor capacitance |

| fm = offset frequency of PN in Hz |

| fO = frequency of oscillation |

| gm = bipolar transistor (oscillator) transconductance |

| in = collector shot noise |

| IQ = oscillator transistor bias current |

| QL = inductor Q |

| QT = tank Q |

| QV = effective varactor Q |

| REQ = equivalent tank parallel resistance |

| RS = varactor series resistance |

| VO = RMS tank voltage |

较宽的调谐范围可通过两个容易理解的途径增大振荡器的相位噪声:降低谐振电路Q值和调谐线噪声的影响。要获得更宽的调谐范围,压变电容必须通过一个更大的电容耦合到谐振电路。这会降低CV (等效可变电容)的Q值,如方程2所示。CV的Q值降低同时使谐振电路净Q值也降低,因而导致相位噪声增加,如方程6所示。

致使相位噪声增加的第二个因素是调谐输入端的热噪声,它会产生频率调制的边带噪声。该项噪声随着调谐范围而增加,并有可能超过振荡器的固有相位噪声。由热噪声引起的相位噪声可由下式计算:

显然,两种情况的相位噪声都随着调谐范围的增加而增大。因此要使免调节VCO保持较低的相位噪声,至关重要的是设定一个恰当的调谐范围,保证带宽要求并能容纳各种可预见的误差源。

由于压变电容耦合的加重,更多的谐振电压摆幅会出现在压变电容两端,而压变电容电压的摆幅必须加以限制以防压变电容被正向偏置。这就限制了谐振电路中的信号功率,因而也就影响到振荡器的相位噪声。最后,当谐振电路的等效串联电阻过大时还会带来起振问题(参见基本方程)。频率调谐范围过宽的VCO可能无法正常起振,尤其是在极限温度下。那么,要实现恰当的调谐范围,首先碰到的问题就是—多少为恰当?

影响振荡频率的误差源

为了适应影响振荡频率的各种误差源,免调节VCO的频率调谐范围必须增加。这些误差源可分为两类:元件参数误差和设计对准误差。设定振荡频率的LC元件当然是非理想的,它们会带来以下问题:

元件之间的差异(容差)

不理想的性能(由于电感、电容以及引线串联电阻等造成有限的频率响应)

电路布线中的分布电容和电感造成的误差

另一方面,设计过程中在对准VCO调谐范围时的不确定因素还会导致设计对准误差。

元件容差

LC振荡器中影响振荡频率的每个容性和感性元件都具有有限的元件到元件精确度,而这种容许误差会给振荡频率带来误差。表1列出了振荡器中频率设定元件的典型容差。

表1. 振荡频率设置元件的容差

| Component | Tolerance |

| Varactor |

±15%at VTUNE = 0.4V, ±10% at VTUNE = 2.4V |

| Inductor | ±5% |

| Capacitors | ±5% |

| Parasitic Capacitance | ±10% |

| Parasitic Inductance | ±6% |

| Oscillator-Device Impedance | ±15% |

设计对准误差

设计对准作为一个振荡频率建立中的误差来源常常被忽视。为了充分利用现有的频率调谐范围,调谐边界必须相对于预期的振荡频率相对称。在建立这个中心点时的任何误差,主要是由元件模型的初始值或平均值的不精确性而引起,都会降低可用的调谐范围。为了在各种温度、电源电压、元件容差等条件下保证振荡频率,调谐范围必须足够宽,以便容纳该误差。

可以利用振荡频率公式计算出总的频率误差,只需对其中的每项元素乘以一个比例因子即可:

还有一个最简单的办法可以计算出各种不同误差所造成的频率偏移,那就是利用一个电子数据表程序,其中包含了详细的基于L、C电路参数的振荡频率公式。

频率偏移和调谐范围

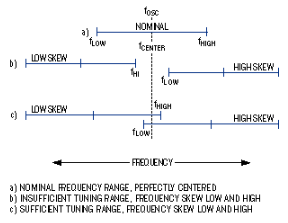

频率调谐范围可通过改变调谐电压获得,从VTUNE(LOW)到VTUNE(HIGH),具有高、低频率边界(fHIGH和fLOW)和一个位于fHIGH和fLOW中点的“中心”频率(fCENTER) (图5)。理想情况下,调谐范围应安排在使fCENTER恰好位于期望频率的位置(图5a)。然而,元件误差和设计对准误差可能会使频率调谐区间发生偏移。

如果在最差情况下,系统提供的调谐电压不足,不能获得足够的频率调谐范围,则期望的振荡频率就无法达到(图5b)。显然,仔细确定调谐范围需求是很有必要的。这可通过以下方法实现,首先计算出所有误差源所引起的频率偏差,然后确定最差情况下的fLOW 《 fOSC且fHIGH 》 fOSC (图5c)。

图5. 调谐范围和频率偏移

设计验证

线路板布局和元件选择完成之后,还需要对设计进行验证和测试(项目甚至超过多数RF电路)。通常,你必须检查调谐范围、启动性能、相位噪声等等性能是否符合设计要求。此外,测试必须基于一个统计有效的生产流程数量之上,以便确定调谐范围和平均中心频率,以及它们相对于预期振荡频率的相对位置。

所有这些工作都是得到一个稳定的、可重复生产并具有预期性能的设计所必需的。这项任务通常需要多次反复,因此,往往要花费数月的时间才能得到一个可以接受、并具有生产价值的分立元件设计。开发一个免调节IF VCO要求仔细的电路设计、各种误差源的周详考虑、电路板的验证以及生产过程监控等,以确保设计的可实施性。现在,Maxim已开发出新款IC来迎接这个挑战(将在第二部分中介绍),解决了VCO的设计难题,同时显著缩短了实现免调节IF VCO所必需的时间。

审核编辑:郭婷

-

中频点焊机电流的调节方法2024-07-14 3920

-

免修整中频VCO:设计考虑因素2023-02-24 2125

-

免调节中频VCO:新型IC简化设计2023-02-10 2205

-

中频压控振荡器所需的设计基础和挑战2023-01-16 2441

-

怎样去实现免调节VCO?2021-04-20 1308

-

超低噪声调节器是怎样为VCO和PLL供电的?2021-04-06 1511

-

中频压控振荡器设计需要考虑什么2020-09-16 1000

-

如何进行免调节中频VCO的新型IC简化设计2020-08-25 600

-

免调节中频VCO设计需要考虑哪些因素?2019-08-22 2872

-

免调节中频VCO的实现2017-11-23 3715

-

MAX147 工作在2.7V的免调节倾斜仪2016-08-18 905

-

免调中频VCO的实现2009-02-08 1243

-

实现免调整VCO1的IC (第二部分)2006-05-07 1207

全部0条评论

快来发表一下你的评论吧 !