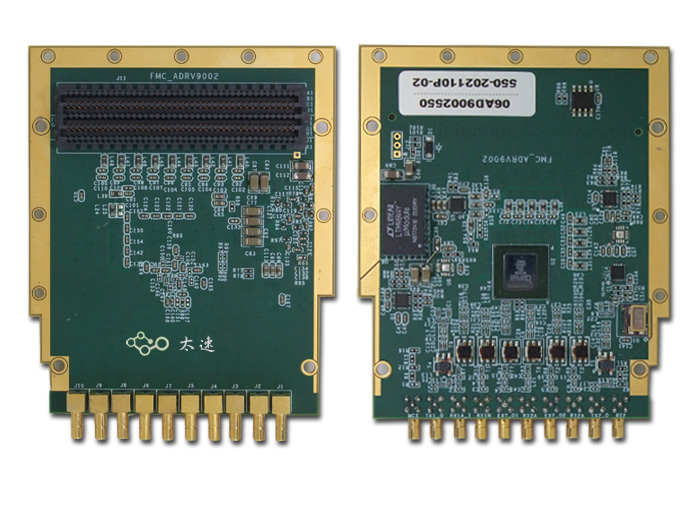

基于ADRV9002双窄带宽带射频收发器的FMC子卡FMC550介绍

电子说

描述

FMC550-基于ADRV9002双窄带宽带射频收发器FMC子卡

一、产品概述

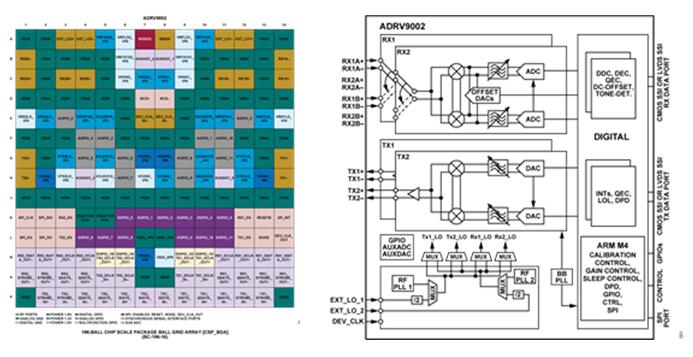

ADRV9002 是一款高性能、高线性度、高动态范围收发器,旨在针对性能与功耗系统进行优化。该设备是可配置的,非常适合要求苛刻、低功耗、便携式和电池供电的设备。ADRV9002 的工作频率为 30 MHz 至 6000 MHz,涵盖 UHF、VHF、工业、科学和医疗 (ISM) 频段、窄带 (kHz) 的蜂窝频段以及高达 40 MHz 的宽带操作。 ADRV9002 能够同时进行 TDD 和 FDD 操作。

收发器包括直接转换信号路径,具有先进的噪声指数和线性度。每个完整的接收器和变送器子系统都包括直流失调矫正、正交误差校正 (QEC) 以及可编程数字滤波器,因此数字基带中不再需要这些功能。另外,它集成了辅助模数转换器 (ADC)、辅助数模转换器 (DAC) 以及通用输入/输出 (GPIO) 等若干辅助功能,因而可提供额外的监测和控制能力。

完全集成的锁相环 (PLL) 为变送器、接收器和时钟部分提供高性能、低功耗小数 N 频率合成。精心选用的设计和布局技术提供了高性能个人射频应用所需要的隔离。

其中集成了全部压控振荡器 (VCO) 和环路滤波器元件,从而尽可能减少外部元件数量。本地振荡器 (LO) 具有灵活的配置选项,并包括快速锁定模式。

该收发器具有低功耗睡眠和监控模式,可在监控通信的同时,节省功耗并延长便携式设备的电池寿命。

完全集成的低功耗数字预失真 (DPD) 针对窄带和宽带信号进行了优化,并实现了高效功率放大器的线性化。

ADRV9002 的内核可以直接由 1.0 V、1.3 V 和 1.8 V 稳压器供电,并通过标准 4 线串行端口进行控制。其他电源用来提供正确的数字接口电平,并优化接收器、变送器和辅助转换器性能。

使用可配置的 CMOS 或低电压差分信号 (LVDS) 串行同步接口 (SSI) 选项,可支持高数据速率和低数据速率接口。

二、优势和特点

• 2 × 2 高度集成的收发器

• 频率范围为 30 MHz 至 6000 MHz

• 变送器和接收器带宽为 12 kHz 至 40 MHz

• 两个完全集成的小数 N 射频频率合成器

• LVDS 和 CMOS 同步串行数据接口选项

• 低功耗监控器和休眠模式

• 多芯片同步功能

• 快速跳频

• 动态配置文件切换,可实现动态数据速率和采样率

• 完全集成的 DPD,适用于窄带和宽带波形

• 可通过 4 线 SPI 完全编程

• 12 mm × 12 mm、196 球 CSP_BGA

• 通过FMC连接器连接FPGA母板(ZC706和ZCU102)

• 采用单个FMC连接器供电

• 包括原理图、布局、BOM、HDL、驱动程序和应用软件

三、产品应用

• 关键任务通信

• 甚高频 (VHF)、超高频 (UHF),以及蜂窝到 6 GHz

• 时分双工 (TDD) 和频分双工 (FDD) 应用

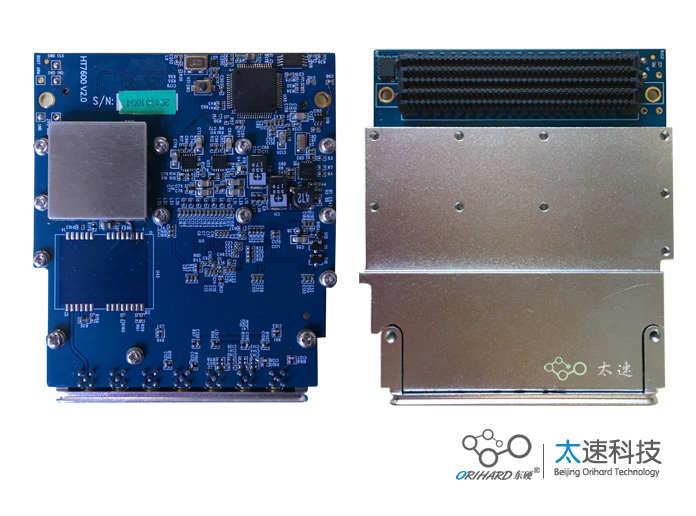

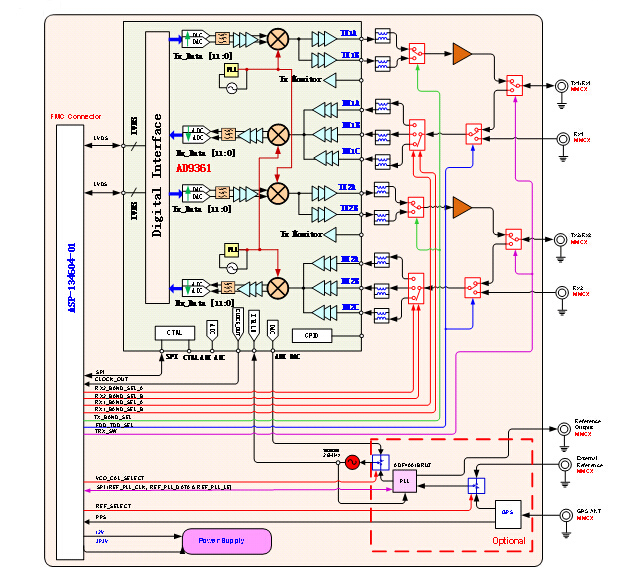

FMC177-基于AD9361的双收双发射频FMC子卡

一、板卡介绍

FMC177射频模块分别包含两个接收通道与发射通道,其频率可覆盖达到70MHz~6GHz,AD9361芯片提供具有成本效益的实验平台,具有达到56MHz的瞬时带宽,更高的灵敏度,灵活的动态范围,广泛适合于SDR(无线电软件),移动基站,WiFi,无线局域网,专用或通用无线电设备等应用。设计者通过使用FMC177,可以有效简单的使用AD9361芯片。

二、主要指标

1. 射频频率:70MHz~6GHz;

2. ADC/DAC采集:12位;

3. 两路TX,两路RX,工作实现方式双工与半双工;

4. RF匹配电阻:50欧;

5. 瞬时带宽:56MHz;

6. 支持直流供电 +12V;

7. 支持GPS;

8. 规格:标准FMC子卡。

三、板子接口特性

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Up to 56 MHz | real-time bandwidth, tunable | |

| 3 | Transmission | >5dBm | CW | |

| 4 | EVM | <1.5% | Typical:5dBm @20MHz bandwidth | |

| 5 | Gain Control Range | >80dB | ||

| 6 | Gain Step | 0.25 dB | ||

| 7 | ACLR | < -45dBc | @ 0dBm LTE output | |

| 8 | Spurious | TBD | ||

| 9 | SSB Suppression | 35dBc | ||

| 10 | LO Suppression | 50dBc | ||

| 11 | DAC Sample Rate (max) | 61.44MS/s | ||

| 12 | DAC Resolution | 12bits | ||

| Rx | 1 | Frequency | 70~6000MHz | |

| 2 | Bandwidth | Up to 56 MHz | real-time bandwidth, tunable | |

| 3 | Sensitivity: | -90dBm@20MHz | Noise Figure < 8dB | |

| 4 | EVM | <1.5% | @ -30dBm input | |

| 5 | Gain Control Range | >60dB | ||

| 6 | Gain Step | 1dB | ||

| 7 | Blocking | TBD | ||

| 8 | Noise Figure | <8db | Maximum RX gain | |

| 9 | IIP3 (@ typ NF) | -25dBm | ||

| 10 | ADC Sample Rate (max) | 61.44MS/s | ||

| 11 | ADC Resolution | 12bits | ||

| 12 | ADC Wideband SFDR | 78dBc | ||

| 1 | Voltage | 3.3V | ||

| 2 | ON/OFF TIME | <6us | For TDD model | |

| 3 | Duplexing Model | TDD or FDD | ||

| 4 | W/ GPSDO Reference | 0.01ppb |

四、应用范围:

SDR(无线电软件); 移动基站,例如Femto‐cells, Pico‐cells, Small‐cells, Micro‐cell 等等;WiFi;无线局域网;专用或通用无线电设备。

五、与FPGA 处理卡搭建系统

本板卡是将FMC177_AD9361 射频收发模块与本公司基于FMC接口K7板卡通过标准的FMC接口相连接。

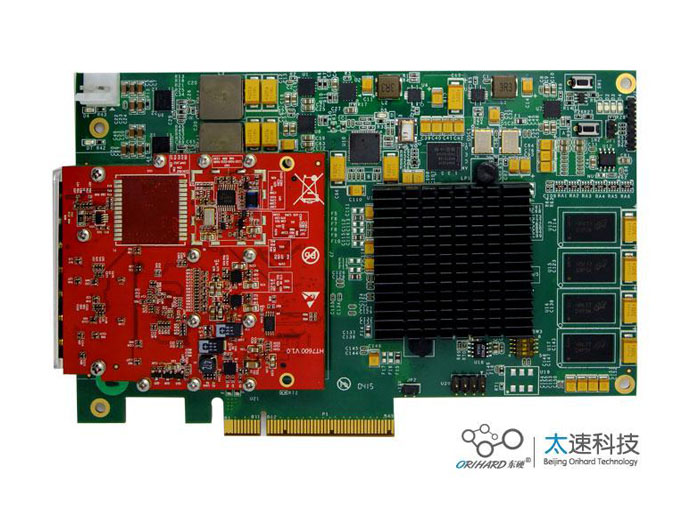

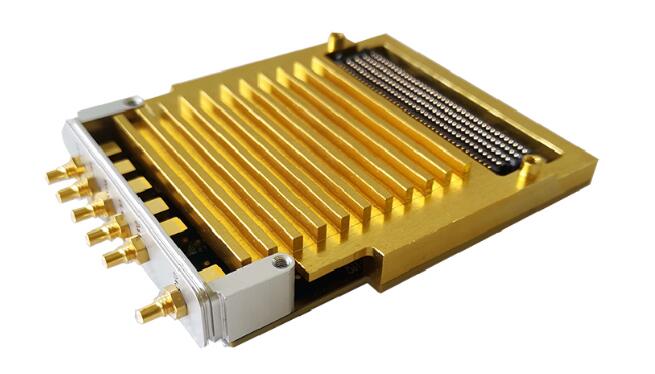

FMCJ465-2路 16bit 12.6GSPS FMC DA子卡

一、板卡概述:

FMCJ465是一款转换速率最高为12.6GSPS 的 DAC 回放板,DAC位数16bit; 板卡基于ADI的AD9172系列DAC设计;板卡支持2路可配置的触发输出/触发输入;DAC的时钟支持内部参考时钟、外部参考时钟、外部采样时钟三种方式;并可提供一个接口同时支持外部采样和外部参考时钟的版本。

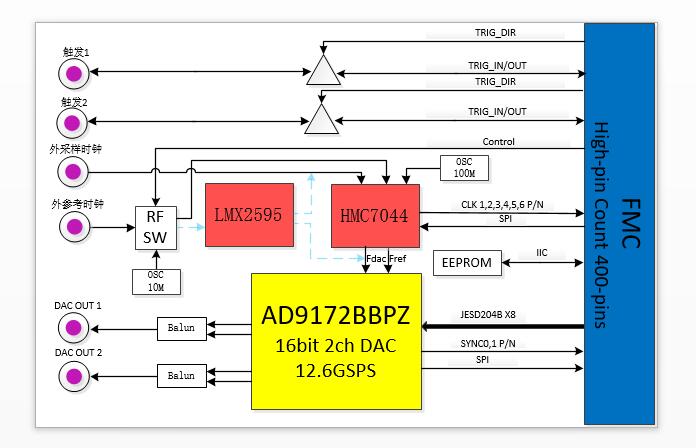

原理框图

二、主要规格:

● 6个SSMC的连接器,其中2个为模拟信号输出1(DA 0)和2(DA 1);一个为外部采样时钟输入(CLK);一个为外部参考时钟输入(RCK),2个为可由载板配置成输入或者输出的同步触发信号(TR1和TR2)

● 外部CLK也可同时兼容外采样和外参考时钟(需事先提出需求)

● 适应范围:完全符合Vita57.1规范,包括结构件,子卡尺寸,面板连接器,正反面器件的限高等,大大提供了子卡的通用性和适配性

● 多种散热方式:风冷或导冷

● AC耦合输入

● 内外部时钟可灵活选择

● HPC高引脚数连接器

● 工作温度:商业级0℃~+70℃ ,工业级-40℃~+85℃

三、板卡性能:

模拟输出

● 输出耦合方式:交流耦合;

● 输出路数:2路;

● 输出频率:10MHz ~ 6000MHz;

● 满量程输出电流:16~26mA(RSET=5KΩ),可编程;

● 输出阻抗:50 Ohm;

● 连接器:SSMC;

数模转换器 DAC

● 单芯片方案;

● 分辨率:16bit;

● 最大更新率:12.6GS/s

● DAC输入兼容JESD204B子类1

时钟

● 支持内参考或外部参考:10MHz,功率0~6dBm

● 支持外部采样时钟最高:12.6 GHz; 功率0~6dBm

● 输入阻抗:50 Ohm;

● 耦合方式:交流耦合;

触发

● 外部触发输入:3.3V LVCMOS或LVTTL;

● 触发输出:3.3V LVCMOS或LVTTL;

● 最大频率:200MHz;

● 连接器:SSMC;

FMC 接口

HPC: ASP-134488-01;

● DP_C2M(0-7),LVDS 1.0V

● LA(00-33),LVDS或者LVCMOS或者LVTTL

● CLK(GBTCLK0,1;CLK0),LVDS 1.8V或2.5V

功耗

● +12V: <0.6 A;

● +3.3V: <0.1A;

● Vadj:<0.2A;

四、其他支持:

● 提供Verilog bit文件

● JESD204B Core

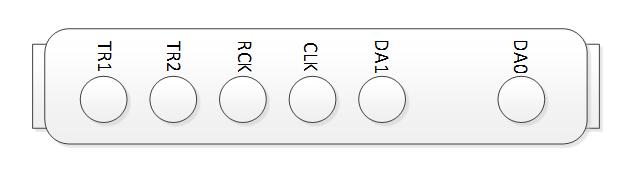

五、前面板

|

前面板描述 序 信号 描述 1 DA 0 模拟信号输出1 2 DA 1 模拟信号输出 2 3 CLK 外部采样时钟(亦可作为外部采样和参考时钟,需事先提出需求) 4 RCK 外部参考时钟 5 TR 1 触发信号1,可配置成IN或OUT 6 TR 2 触发信号2,可配置成IN或OUT 六、应用(QT7227): ● 软件无线电 ● 宽带MIMO应用 ● 数字波束成形 ● (雷达/声纳)电子战 ● 物理实验 ● 信号智能检测 ● 航空航天和测试仪器 |

| FMCJ450-基于ADRV9009的双收双发射频FMC子卡 |

一、板卡概述

ADRV9009是一款高集成度射频(RF)、捷变收发器,提供双通道发射器和接收器、集成式频率合成器以及数字信号处理功能。这款IC具备多样化的高性能和低功耗组合,FMC子卡为2路输入,2路输出的射频收发卡,配合FPGA工作满足3G、4G和5G宏蜂窝时分双工(TDD)基站应用要求。

二、技术指标

• 双发射器

• 双接收器

• 双输入共享观察接收器

• 最大接收器带宽:200 MHz

• 最大可调谐发射器合成带宽:450 MHz

• 最大观察接收器带宽:450 MHz

• 全集成的小数 N 射频合成器

• 全集成的时钟合成器

• 适用于射频 LO 和基带时钟的多芯片相位同步

• JESD204B 数据路径接口

• 调谐范围:75 MHz 至 6000 MHz

| No. | Items | Specifications | Remark | |

| Tx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | Up to 450 MHz | Tx real-time bandwidth, tunable | |

| 3 | Transmission Power | 17dBm | 100~6000MHz, CW | |

| 4 | EVM | <0.7% | ||

| 5 | Gain Control Range | 32dB | ||

| 6 | Gain Step | 0.05 dB | ||

| 7 | ACLR | < -64dBc | @0dBm output | |

| 8 | Spurious | 60dBc | ||

| 9 | SSB Suppression | 65dBc | ||

| 10 | LO Suppression | 70dBc | ||

| 11 | DAC Sample Rate (max) | 122.88MS/s | ||

| 12 | DAC Resolution | 14bits | ||

| Rx | 1 | Frequency | 100~6000MHz | |

| 2 | Bandwidth | 8 to 200 MHz | real-time bandwidth, tunable | |

| 3 | Sensitivity: | -93dBm@20MHz | Noise Figure <3db | |

| 4 | EVM | <1.5% | @ -30dBm input | |

| 5 | Gain Control Range | |||

| 6 | Gain Step | 0.5dB | ||

| 7 | Rx Alias Band Rejection | 80dB | Due to digital filters | |

| 8 | Noise Figure | <3db | Maximum RX gain | |

| 9 | IIP3 (@ typ NF) | -25dBm | ||

| 10 | ADC Resolution | 16bits | ||

| 11 | ADC Wideband SFDR | 78dBc | ||

| 1 | Voltage | 3.3V& 12V | ||

| 2 | ON/OFF TIME | <6us | TDD model | |

| 3 | Duplexing Model | TDD | ||

| 4 | Power Consumptions | <6w |

三、产品应用

3G/4G/5G TDD 宏蜂窝基站;TDD 有源天线系统;大规模 MIMO;电子战;便携测试设备

四、软件系统

提供支持ZYNQ的 FMC接口测试程序源代码

五、物理特性:

板卡遵循FMC规范,HPC,大小 76.5X69mm。

六、供电要求:

FMC 接口 +12V供电

七、ADRV9009 应用软件

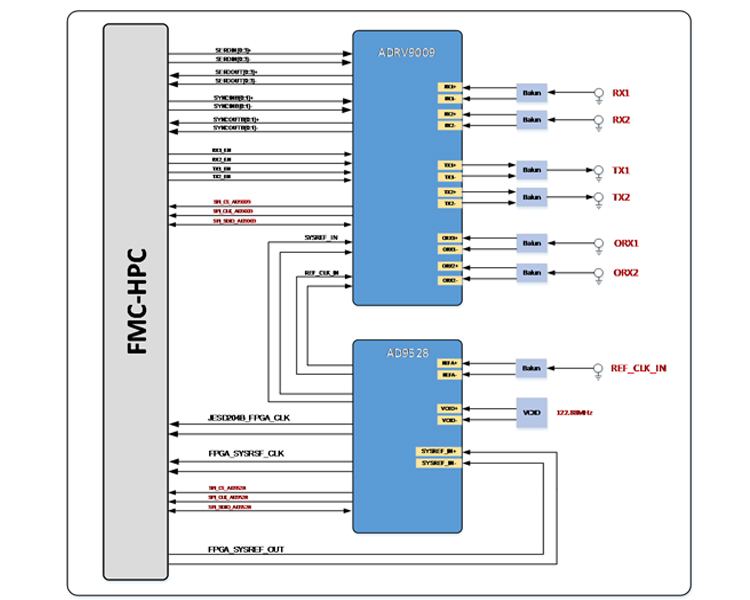

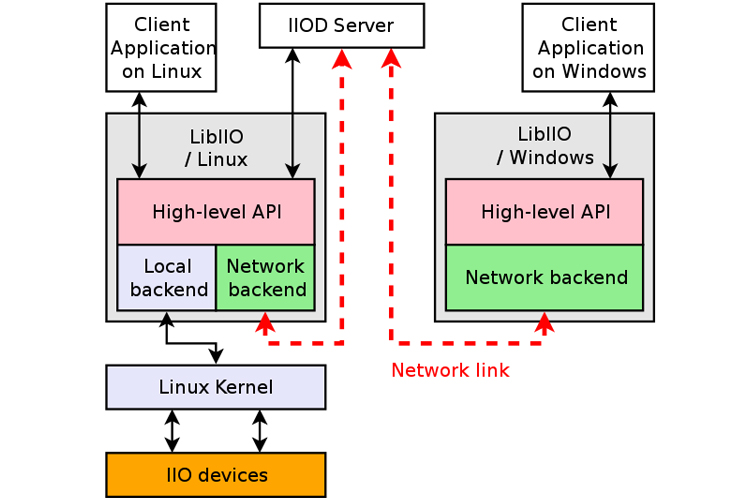

软件架构:

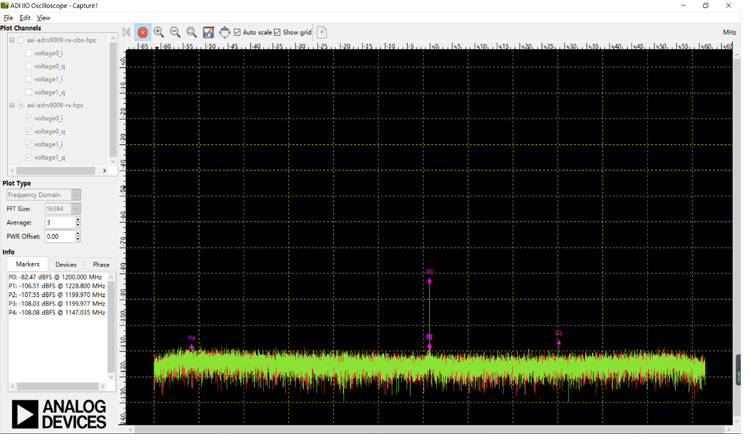

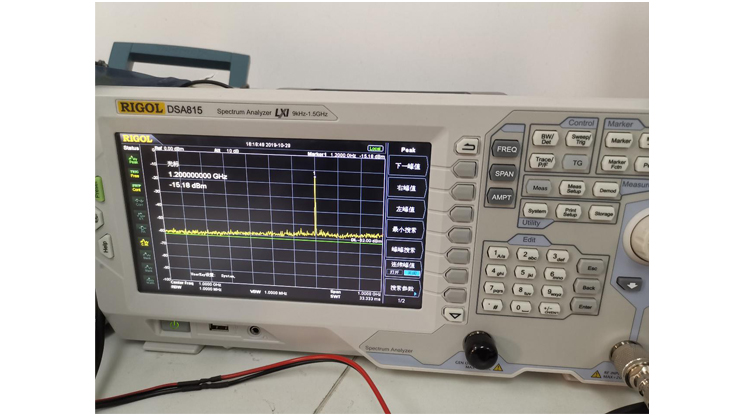

AD 采集1.2G波形:

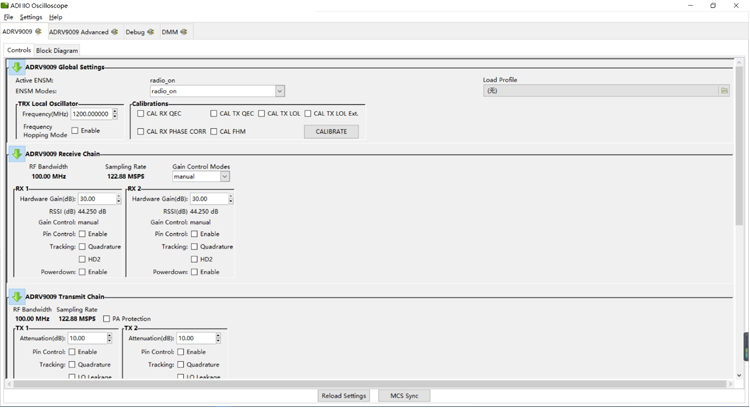

DA 输出设置1.2G及波形:

审核编辑 黄宇

-

中频信号采集卡 FMC子卡设计原理图:FMC145-四路16位125Msps AD FMC子卡模块2026-03-12 216

-

FMC子卡设计方案:FMC210-1路1Gsps AD、1路2.5Gsps DA的FMC子卡2025-08-07 1196

-

Analog Devices Inc. ADRV9003窄带/宽带射频收发器数据手册2025-06-30 998

-

FMC子卡设计原理图:FMC209-基于FMC的4路125MAD输入、2路1GDA输出子卡 中低频信号采集2024-12-30 1150

-

ADRV9002: Dual Narrow/Wideband RF Transceiver Data Sheet ADRV9002: Dual Narrow/Wideband RF Transceiver Data Sheet2023-10-17 102

-

全功能双CameraLink SDR接口 FMC子卡QT7421介绍2023-09-11 2383

-

ADRV9002射频收发器英文手册2023-07-13 733

-

FMC子卡设计原理图:FMCJ450-基于ADRV9009的双收双发射频FMC子卡2023-07-05 2066

-

FMC子卡设计资料原理图:FMC550-基于ADRV9002双窄带宽带射频收发器FMC子卡2023-01-19 866

-

FMC子卡设计方案保存:FMCJ450-基于ADRV9009的双收双发射频FMC子卡2022-07-27 17611

-

如何为ADRV9002设计RF前端电路2022-06-22 3168

-

ADRV9002:双窄/宽带射频收发器初步数据表2021-04-14 1014

-

ADRV9004:双窄/宽带射频收发器初步数据表2021-03-22 1196

-

ADRV9009板卡学习资料:FMCJ450-基于ADRV9009的射频收发模块2020-03-20 3502

全部0条评论

快来发表一下你的评论吧 !