在Vivado中构建自定义AXI4-Stream FIR滤波器IP 1

模拟技术

描述

AMD-Xilinx 的 Vivado 开发工具具有很多方便FPGA开发功能,我最喜欢的功能之一是block design的设计流程。Vivado 中的block design是使用RTL IP形式的图形表示进行设计,在block design中使用 RTL 模块的方便之处在于,它将自动检测某些类型的信号,例如时钟、复位和总线接口,然后,检测这些信号进行IP间的自动化连接。Vivado 中包含大量预构建 IP 模块(官方IP)。

为了方便用户进行相关设计,Vivado 提供了一个内置的 IP 封装编辑器工具,它可以为 AXI IP 生成框架,只需将自己的 RTL 代码插入其中。同时也提供了相关的驱动文件,可以在Vitis中方便调试。

为了演示究竟上面流程“好”在哪里,接下来我们创建一个AXI FIR IP 模块,然后将IP添加到我们设计中最后验证功能。

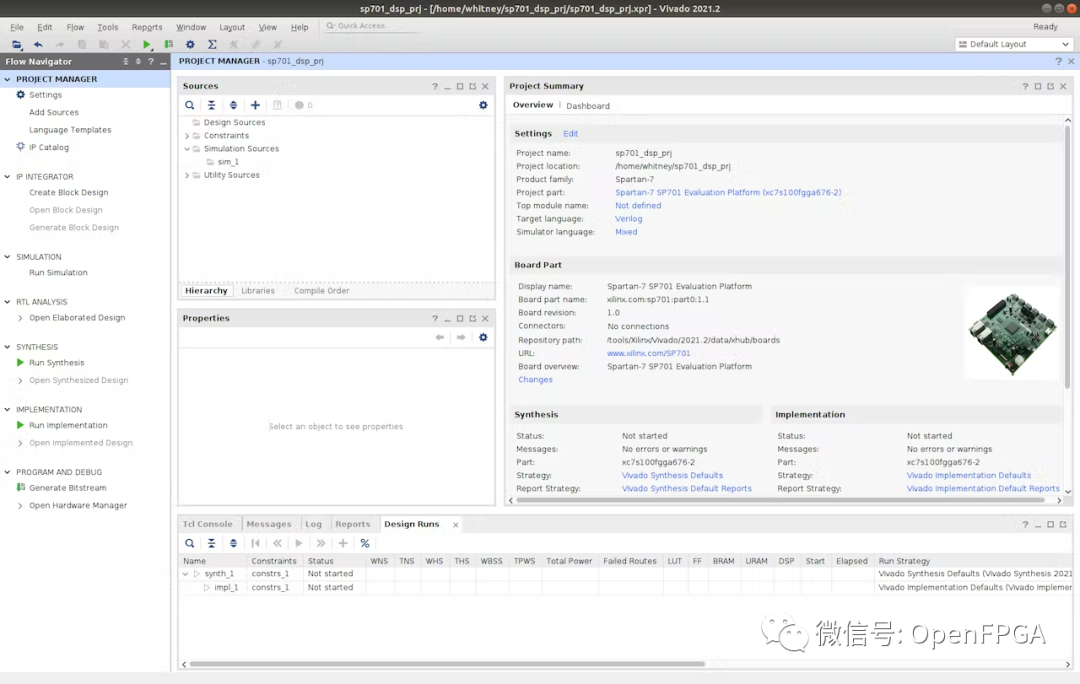

创建 Vivado 项目

首先,启动 Vivado 并针对自己的FPGA创建一个新项目。

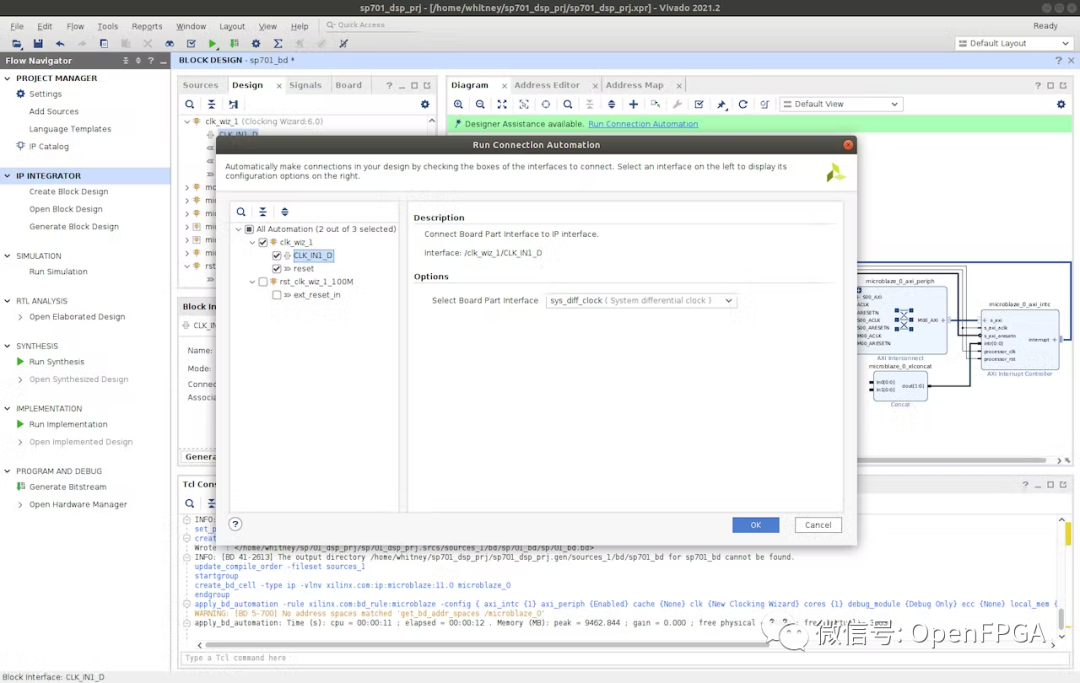

添加 MicroBlaze,对于这个项目来说,使用 BRAM 就足够了。

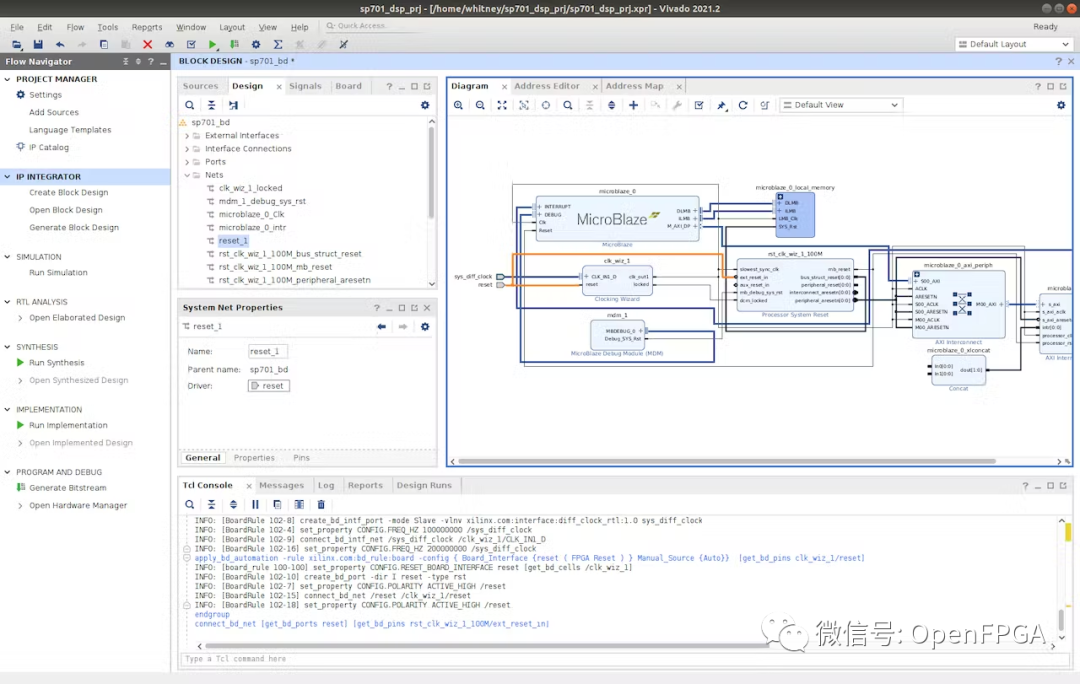

选择 Add IP 选项并搜索 MicroBlaze,将其添加到模块设计中并运行 Block Automation,该模块会在窗口顶部的绿色横幅中弹出。接下来添加中断控制器。

验证并保存块设计,接下来我们将开始我们的IP设计。

创建新的 AXI4 外设

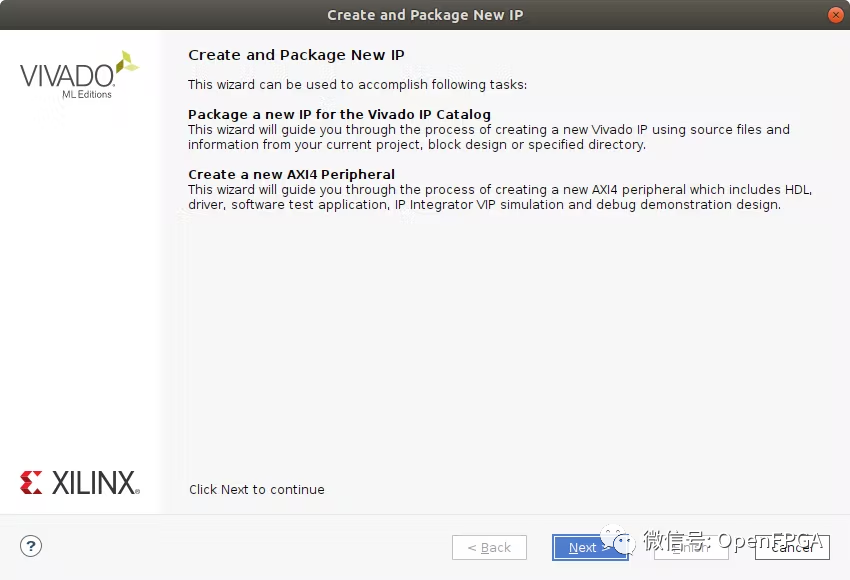

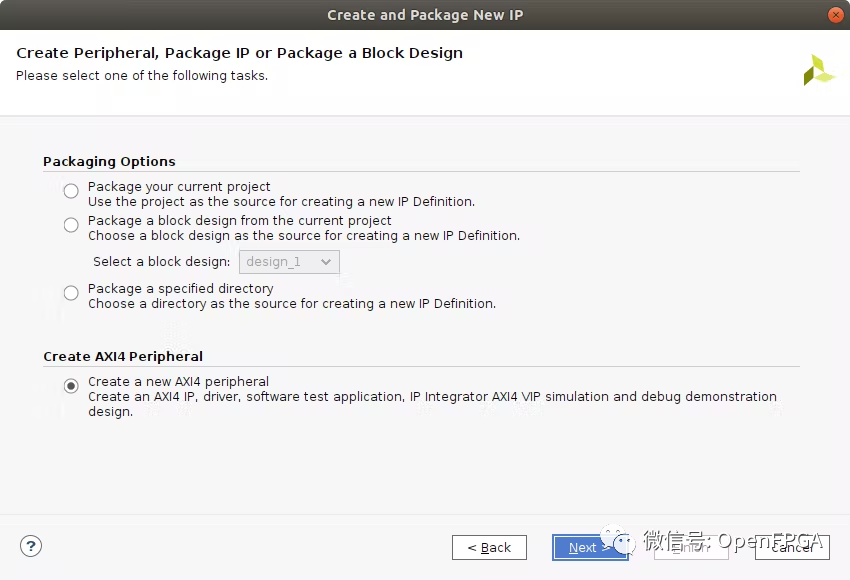

要使用自己的 RTL 创建新的 AXI 外设并将其封装为 IP ,请选择工具>创建和打包新 IP...

在弹出的窗口中,按照提示逐步浏览屏幕,选择Create AXI4 Peripheral选项,指定 IP 块的所需名称、位置目录以及 IP 将具有的 AXI 接口数量以及 AXI类型。

Vivado 中使用了三种主要类型的 AXI:

- AXI4 (full)

- AXI4-Lite

- AXI4-Stream

每种类型都适合不同的用例,在这个项目中,我们正在创建自己的 AXI FIR 滤波器 IP 。由于 FIR 滤波器输入并输出具有已知数据包边界和流量控制要求的恒定数据流,因此 AXI4-Stream 是最适合的类型。它将需要一个从接口来输入数据样本,并需要一个主接口来输出处理后的样本。

作为参考,FIR 是一个运行速度为 100 MS/s 的 LPF,具有 15 个抽头,接收带符号的 16 位数据并输出带符号的 32 位数据。它有一个从 1MHz 到 10MHz 的通带和一个从 20MHz 开始的阻带。

接下来,选择编辑 IP并单击完成。IP 包编辑 Vivado 项目将重新打开一个gui。

-

一文详解Video In to AXI4-Stream IP核2025-04-03 3054

-

自定义AXI-Lite接口的IP及源码分析2023-06-25 5156

-

在Vivado中构建自定义AXI4-Stream FIR滤波器IP 22023-02-10 3047

-

构建自定义AXI4-Stream FIR滤波器的步骤2022-11-07 3793

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10917

-

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍2022-07-03 10916

-

关于AXI4-Stream协议总结分享2022-06-23 3338

-

AXI-stream数据传输过程2021-01-08 2904

-

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建2020-12-21 4797

-

请问AXI4-Stream到Video核心的技巧有什么?2019-11-08 3449

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4781

-

如何使用Vivado功能创建AXI外设2018-11-29 7894

全部0条评论

快来发表一下你的评论吧 !