在Vivado中构建自定义AXI4-Stream FIR滤波器IP 2

电子说

描述

将自定义 RTL 添加到 AXI4-Stream IP

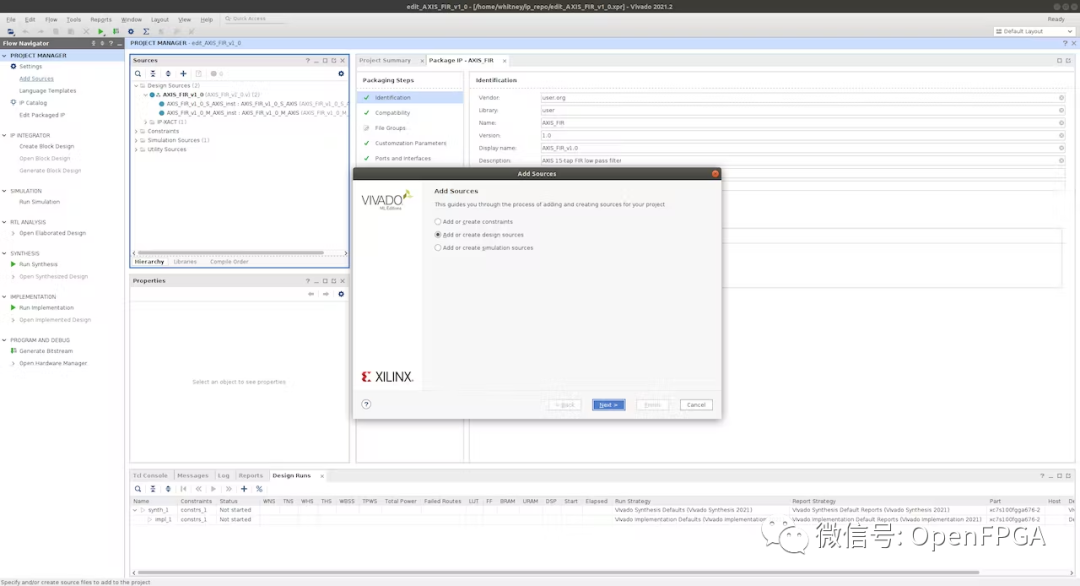

从Flow Navigator中选择Add Sources添加我们要设计的 FIR Verilog 文件。

在使用 Add Files 选项指向 FIR Verilog 文件后,取消选中Scan and add RTL include files into project复选框。由于这不是一个普通的 Vivado 项目,并且 Verilog 代码被打包到一个 IP 块中,因此选中该选项后将引发错误。

添加后,源层次结构更新并且 FIR Verilog 文件独立于 AXI Verilog 源文件。

根据生成 IP 编辑器 Vivado 项目时所做的选择,会为此 AXI4-Stream 外设生成三个 RTL 源文件:

- 从接口功能 RTL。

- 主接口功能 RTL。

- 具有物理接口声明和主从接口实例化的顶层文件。

在设计之前,需要将几个默认未启用的可选 AXI4-Stream 接口信号添加到主 AXI 端口和从 AXI 端口。大多数 DSP IP 模块,例如 DDS 利用了 AXI4-Stream 额外的keep 和 tlast信号。

添加这些可选信号很简单,但最初并不清楚。导航到Package IP窗口中的Customization Parameters选项卡。

主接口和从接口都需要添加它们,因此右键单击每个接口并选择Edit Interface 。

在“Parameters”选项卡中启用HAS_TKEEP ,方法是单击每个选项,然后单击单个箭头将其从左列移动到右列。

然后切换到Port Mapping选项卡,将 tkeep 和 tlast 映射到 AXI IP 块的物理接口。在Interface's Logical Ports列和IP's Physical Ports列中分别匹配 tkeep 和 tlast 信号。然后在下面的Mapped Ports Summary列中验证它们的映射。

由于默认情况下不启用 tkeep,因此还必须手动将其端口声明添加到所有三个 AXI 接口 RTL 源文件的用户定义端口声明部分。它还需要添加到顶级 AXI 包装器中的 AXI 主接口和从接口实例中。

在注释Add user logic here标记的部分中实例化 FIR Verilog 模块。

现在,虽然 AXI 接口的基本功能分别在每个 RTL 源文件中自动生成,但如何从输入数据流中提取数据并传递到自己的自定义逻辑中由自己来定义。以及如何将自定义逻辑的数据输出馈送到主 AXI 接口进行输出。因此,会在三个自动生成的 RTL 源文件中注意到相同的 Add user 逻辑。

另一点需要注意的是,AXI4-Stream 接口的功能需要进行一些修改,以便将 tkeep 和 tlast 信号功能添加到主 AXI 接口和从 AXI 接口。

这个项目的最后一个独特的要求是,因为这个逻辑的核心是一个 FIR 滤波器,所以主从 AXI 接口和 FIR 都需要由相同的时钟作为 FIR 采样时钟。所以只是将从 AXI 接口时钟传递给 FIR 和主 AXI 接口。

-

一文详解Video In to AXI4-Stream IP核2025-04-03 3066

-

自定义AXI-Lite接口的IP及源码分析2023-06-25 5174

-

在Vivado中构建自定义AXI4-Stream FIR滤波器IP 12023-02-10 1551

-

构建自定义AXI4-Stream FIR滤波器的步骤2022-11-07 3797

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10930

-

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍2022-07-03 10925

-

关于AXI4-Stream协议总结分享2022-06-23 3348

-

AXI-stream数据传输过程2021-01-08 2909

-

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建2020-12-21 4801

-

请问AXI4-Stream到Video核心的技巧有什么?2019-11-08 3456

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4791

-

如何使用Vivado功能创建AXI外设2018-11-29 7900

全部0条评论

快来发表一下你的评论吧 !