在Vivado中构建自定义AXI4-Stream FIR滤波器IP 3

模拟技术

描述

封装 AXI IP 块

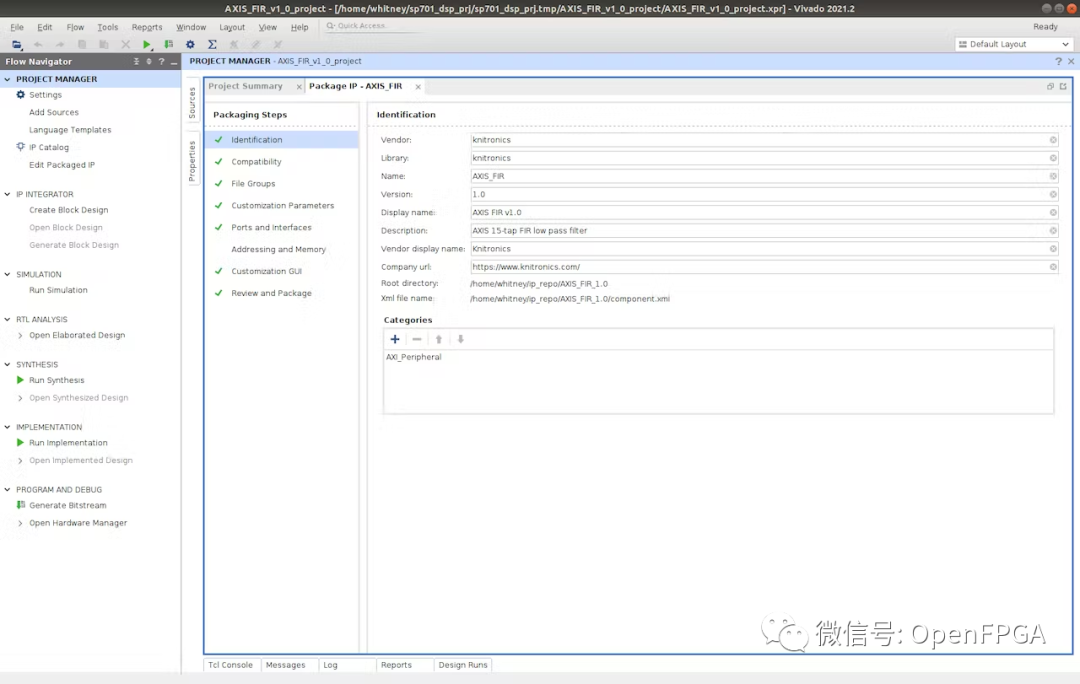

返回到 Package IP 窗口,让我们浏览每个选项卡并验证,然后最终将其打包。

第一个选项卡中是输出 AXI 外设 IP 包的基本显示信息。

第二个标签很重要。默认情况下,AXI 外设 IP 仅支持启动 IP 包编辑器的主 Vivado 所针对的 FPGA 芯片系列。大多数时候,可能希望能够将 AXI 外设 IP 块与其他 Xilinx FPGA 芯片系列一起使用,就需要添加我们需要的目标FPGA芯片。

对于其余选项卡,默认需求即可。

在最后一个选项卡中,单击窗口底部的Package IP按钮。将出现一个提示,询问是否要关闭 IP 编辑器 Vivado 项目。

此时,FIR AXI IP 块被打包并放置在 Package IP 窗口的第一个选项卡指定的目录中的存储库中。

将自定义 AXI4-Stream FIR 添加到项目

现在自定义 FIR AXI IP 模块已经完成并封装,我们可以返回原始 Vivado 项目,将其添加到模块设计中。

我们的验证项目如下:

其中DDS IP设置如下:

创建仿真平台

首先创建仿真文件,并在sim文件夹下的 Sources 选项卡中,右键单击它并选择Set as Top 。

在这种情况下,只需在块设计中实例化块设计,并为其提供差分系统时钟和主 FPGA 复位。一旦接收到时钟和复位信号,相位增量状态机就会自行运行。

``timescale 1ns / 1ps`

module sp701_bd_tb;

reg clk_p, clk_n, reset;

always begin

clk_p = 1; clk_n = 0;

#5;

clk_p = 0; clk_n = 1;

#5;

end

always begin

reset = 1;

#40;

reset = 0;

#1000000000;

end

sp701_bd sp701_bd_i (

.reset(reset),

.sys_diff_clock_clk_n(clk_p),

.sys_diff_clock_clk_p(clk_n)

);

endmodule

这里注意一下主 AXI 接口输出信号和 tlast、tvalid 和 tdata 需要进行初始化。否则仿真将会报错。

单击Flow Navigator窗口中的Run Simulation并选择Run Behavioral Simulation 。

注意仿真结果显示格式。

参考

https://www.hackster.io/

总结

上面的一些创建细节没有全部展现,因为本身对于IP的创建不是我们的核心,我们只想说明使用目前这种BD设计可以达达简化设计,尤其是目前Verilog的一些缺点。

最后说一下调试中的注意点,就是使用ILA查看AXI-Stream输出时候,会造成FIR的时序与采样混淆导致 FIR 不再工作,可能会查看不到任何波形,使用AXIS的专用调试IP即可,后续我们在说明这方面的知识。

-

一文详解Video In to AXI4-Stream IP核2025-04-03 3066

-

自定义AXI-Lite接口的IP及源码分析2023-06-25 5174

-

在Vivado中构建自定义AXI4-Stream FIR滤波器IP 12023-02-10 1551

-

构建自定义AXI4-Stream FIR滤波器的步骤2022-11-07 3797

-

AXI4 、 AXI4-Lite 、AXI4-Stream接口2022-07-04 10930

-

AXI4-Stream Video 协议和AXI_VDMA的IP核介绍2022-07-03 10925

-

关于AXI4-Stream协议总结分享2022-06-23 3349

-

AXI-stream数据传输过程2021-01-08 2909

-

如何吧AXI4-stream时钟转换器tkeep设置为null?2020-05-08 4182

-

请问AXI4-Stream到Video核心的技巧有什么?2019-11-08 3456

-

自定义sobel滤波IP核,IP接口遵守AXI Stream协议2019-08-06 4791

-

如何使用Vivado功能创建AXI外设2018-11-29 7900

全部0条评论

快来发表一下你的评论吧 !