FPGA学习-USB 3.0协议理解

描述

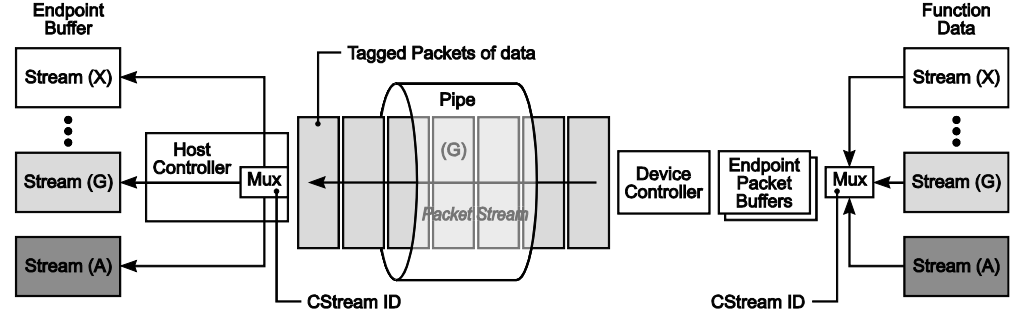

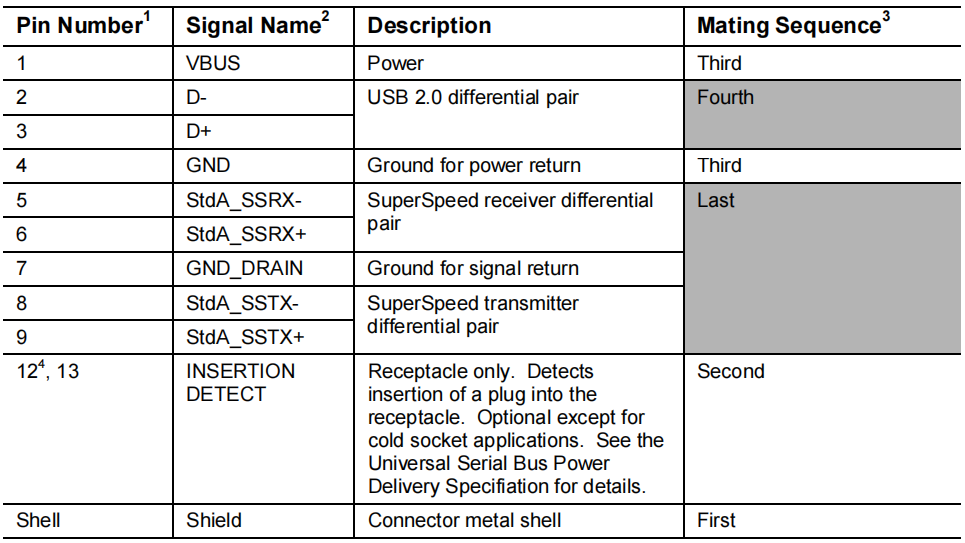

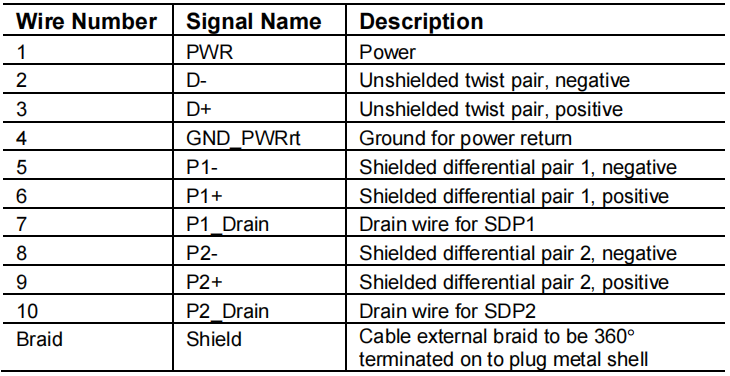

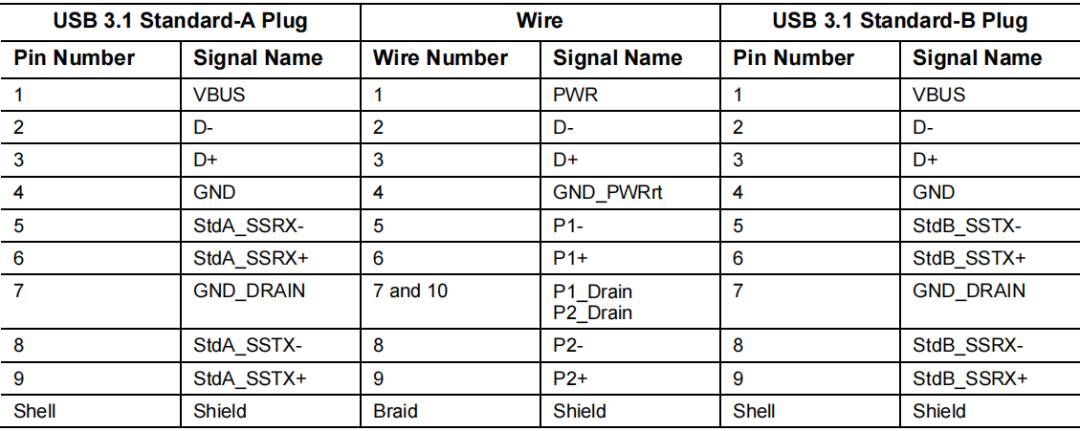

USB3.0和USB2.0相比,在线缆上从4根线(Vbus、GND、D+、D-)变为了8根线(Vbus、GND、D+、D-、SSRX+SSRX-SSTX+SSTX-),可见增加的4根线都是和超速相关的,新增加的超速有两类,分别为:超速Gen 1(5.0 Gbps), 超速+Gen 2(10 Gbps),还兼容USB2.0的3类速率:low-speed (1.5 Mbps), full-speed (12 Mbps), and high-speed (480 Mbps)。从设计可以看出,USB3.0的重点解决的问题是速率,最高10Gbps。

扫描二维码获取

更多精彩

FPGA设计论坛

欢迎关注至芯科技

至芯官网:www.zxopen.com

至芯科技技术论坛:www.fpgaw.com

至芯科技淘宝网址:

https://zxopen.taobao.com

至芯科技FPGA初级课程(B站) :

https://space.bilibili.com/521850676

至芯科技FPGA在线课程(腾讯课堂) :

https://zxopenbj.ke.qq.com/

至芯科技-FPGA 交流群(QQ):282124839

更多资料下载欢迎注册 http://www.fpgaw.com

扫码加微信回复加群

邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA学习-USB 3.0协议理解

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- FPGA

-

USB 3.0开发板 USB3.0+fpga开发板 FPGA开发板2018-09-20 2069

-

USB 3.0开发板 USB+FPGA开发板 FPGA开发板2018-10-18 2711

-

USB 3.0开发板 USB3.0+FPGA开发板2018-11-21 7554

-

USB 3.0开发板 USB3.0+FPGA开发板 FPGA开发板 USB开发板2019-01-08 1135

-

USB 3.0开发板 USB3.0+FPGA开发板 FPGA开发板2019-01-15 1520

-

USB 3.0开发板 USB+FPGA开发板 USB开发板2019-01-22 1053

-

USB3.0协议2022-03-13 15059

-

USB3.0调试手册2017-08-08 2733

-

基于FPGA的USB3.0协议高速通信架构2021-06-01 1446

-

FPGA和USB3.0通信-USB3.0协议简介2021-11-02 7203

-

FPGA和USB3.0通信-USB3.0 PHY简介2021-11-09 10910

-

FPGA和USB3.0通信-FX3硬件设计简谈2021-12-01 1512

-

FPGA和USB3.0通信-USB3.0 PHY介绍2021-12-20 2073

-

USB3.0协议规范(中文)2022-10-24 1743

-

基于FPGA的USB3.0回环传输测试方案2023-10-01 7825

全部0条评论

快来发表一下你的评论吧 !