了解一下DC-DC的layout

电子说

描述

DC-DC的电路比LDO会复杂很多,噪声也更大,布局和layout要求更高,layout的好坏直接影响DC-DC的性能,所以了解DC-DC的layout至关重要。

1. Bad layout

EMI,DC-DC的SW管脚上面会有较高的dv/dt, 比较高的dv/dt会引起比较大的EMI干扰;

地线噪声,地走线不好,会在地线上面会产生比较大的开关噪声,而这些噪声会影响到其它部分的电路;

布线上产生电压降,走线太长,会使走线上产生压降,而降低整个DC-DC的效率;

2. 一般原则

开关大电流回路尽量短;

信号地和大电流地(功率地)单独走线,并在芯片GND处单点连接;

① 开关回路短

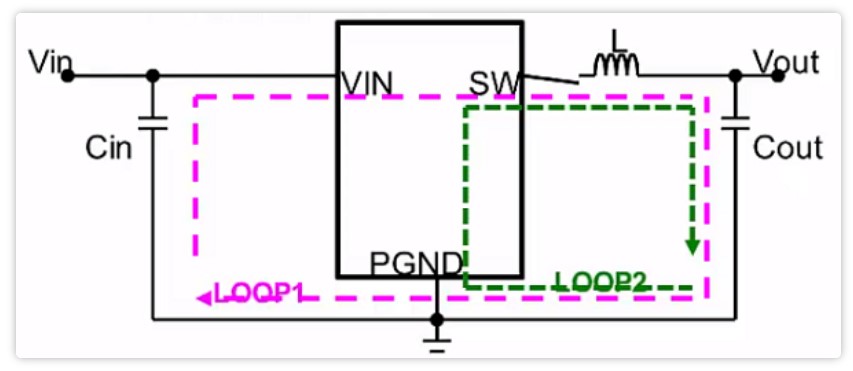

下图中红色LOOP1为DC-DC高边管导通,低边管关闭时的电流流向;绿色LOOP2的为高边管关闭,低边管开启时的电流流向;

为使这两个回路尽量小,引入更少的干扰,需要遵从如下几点原则:

电感尽量靠近SW管脚;

输入电容尽量靠近VIN管脚;

输入输出电容的地尽量靠近PGND脚;

使用铺铜的方式走线;

为什么要这么做?

走线过细过长会增大阻抗,大电流在此大阻抗上会产生比较高的纹波电压;

走线过细过长会增大寄生电感,此电感上耦合开关噪声,影响DC-DC稳定性,造成EMI问题;

寄生电容和阻抗会增大开关损耗和导通损耗,影响DC-DC效率;

② 单点接地

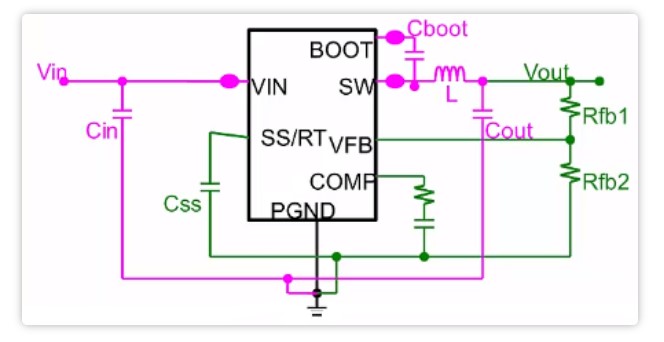

单点接地,指的是信号地和功率地进行单点接地,功率地上会有比较大的开关噪声,所以需要尽量避免对敏感小信号造成干扰,如FB反馈管脚。

大电流地:L,Cin,Cout,Cboot连接到大电流地的网络;

小电流地:Css,Rfb1,Rfb2单独连接到信号地的网络;

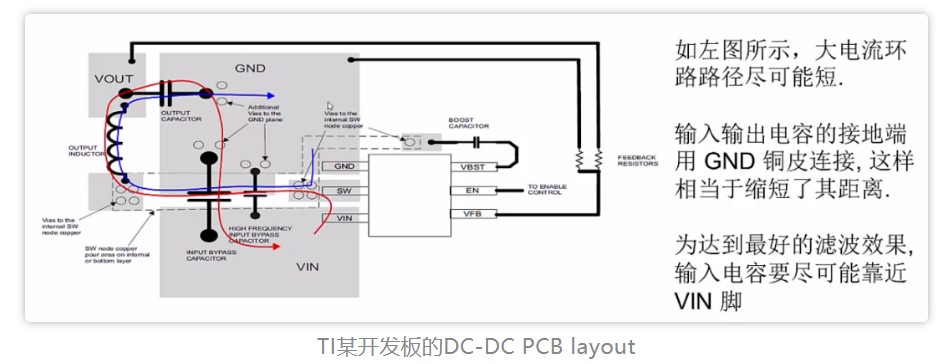

下图是TI的一个开发板的layout,红色为上管开时的电流路径,蓝色为下管开时的电流路径;如下的layout有如下比较好的优点:

① 输入输出电容的GND用铜皮进行连接,摆件时,两者的地尽量放一起;

② DC-DC Ton和Toff时的电流路径都很短;

③ 右边小信号是单点接地,距离比较远,免受左边大电流开关噪声的影响;

3. 实例

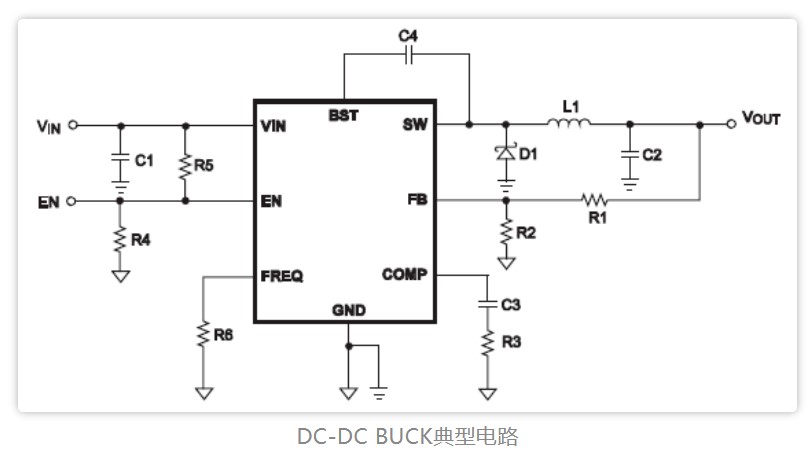

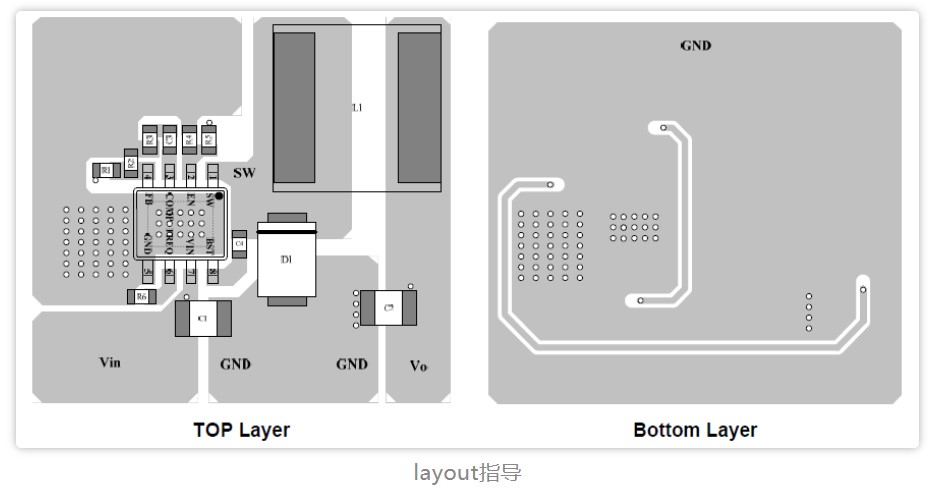

如下给出一个典型DC-DC BUCK电路的layout,SPEC中给出如下几点:

输入电容,高边MOS管,和续流二极管形成的开关回路尽可能小和短;

输入电容尽可能靠近Vin Pin脚;

确保所有反馈连接短而直接,反馈电阻和补偿元件尽可能靠近芯片;

SW远离敏感信号,如FB;

将VIN、SW,特别是GND分别连接到一个大的铜区,以冷却芯片,提高热性能和长期可靠性;

4. 小结一下

DC-DC电路的layout至关重要,直接影响到DC-DC的工作稳定性和性能,一般DC-DC芯片的SPEC都会给出layout指导,可参考进行设计。

审核编辑:刘清

-

DC-DC电源基础知识(PPT版)2025-06-19 330

-

DC-DC 的 PCB布局设计小技巧2025-03-11 7084

-

DC-DC的PCB设计注意的点2024-01-17 1146

-

5条DC-DC PCB layout建议2024-01-16 1736

-

DC-DC的Layout要点(2)2023-07-15 6142

-

推荐一个DC-DC电路设计工具2023-03-17 7260

-

DC-DC的PCB设计2022-09-06 1626

-

DC-DC PCB layout指导说明2022-05-12 1120

-

DC-DC转换器和AC-DC转换器的区别及功能2021-11-17 7102

-

DC-DC的layout有哪些原则2021-11-16 2047

-

DC-DC PCB layout 指导2021-11-09 946

-

DC-DC中PCB设计的layout2021-09-13 8151

-

请问大家能推荐一下DC-DC升压电路?2019-04-04 2349

-

pwm dc,如何更好的设计PWM DC-DC系统?2017-10-28 5465

全部0条评论

快来发表一下你的评论吧 !