Xilinx FPGA重构技术介绍

描述

重构技术介绍

重构技术是一项非常实用的技术,从比特属性上来分类可以分成全部重构和局部重构。全部重构即在重构时将配置整个FPGA器件的比特文件重新加载一次,对FPGA进行一次完整的编程配置;局部重构与全部重构有所不同,局部重构时加载的比特文件只是一个部分比特,该部分比特对特定区域进行重新配置。

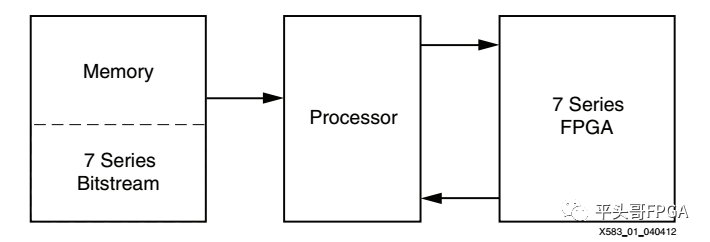

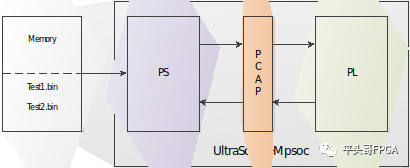

针对Xilinx不同系列的器件,进行重构的方式会有所区别,对于非Zynq系列的器件,重构的实现需要借助FPGA器件之外的处理器来实现,重构接口为SelectMAP,非Zynq系列器件的重构框图如图 1所示;Zynq系列的由于自身嵌入了ARM处理器,可以无需借助其他处理器而实现重构的功能,Zynq系列器件的PS侧可以通过PCAP接口对PL侧完成重构,但是Zynq7000和UltraScale+Mpsoc在具体实现时所使用的库函数会有区别,两者的重构实现不能互用。

图 1 非Zynq系列器件的重构框图

本文档主要针对的器件为UltraScale+Mpsoc系列,通过PCAP接口对PL侧进行重构,重构框图如下所示:

图 2 UltraScale+Mpsoc系列重构框图

重构步骤

建立工程

详细操作在此不做详述,具体可以参考《Vivado Design Suite Tutorial Embedded Processor Hardware Design》,为了验证需要,硬件允许的情况下可以编写一段闪灯程序。

建立BlockDesign

详细操作在此不做详述,具体可以参考《Vivado Design Suite Tutorial Embedded Processor Hardware Design》,建立BlockDesign后,加入一个Zynq Mpsoc IP核,需要指出的是,为了能实现重构,需要在此IP核中使能SD卡,DDR以及UART(方便调试),并根据硬件的实际情况对它们的参数进行设置。根据需要添加其他IP。

编写编译代码

完成前面的步骤之后就可以建立自己的用户程序,主要是通过PS来实现对PL测逻辑的重构

验证调试

在进行验证调试前需要做好准备工作,如前所述,PL侧可以通过两个实现,生成两个频率不同的闪灯程序的bit文件,由于重构时只能使用bin文件,所以需要将bit文件转换成bin文件,在Vivado中的Tcl Console中使用write_cfgmem指令可以将bit转换成bin文件,具体指令如下:

write_cfgmem -format BIN -interface SMAPx32 -disablebitswap -loadbit "up 0x0 文件名.bit" "bin文件名"

生成好的bin文件需要拷贝到Memory中,通常都使用SD卡来存储重构的bin文件。

以上准备工作就绪之后就可以Debug调试了,建议Debug调试时将启动模式设置成Jtag模式。

演示Demo

本章节通过搭建演示环境和工程对重构的实现进行板级验证。

演示环境

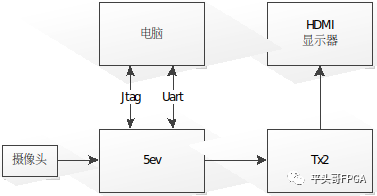

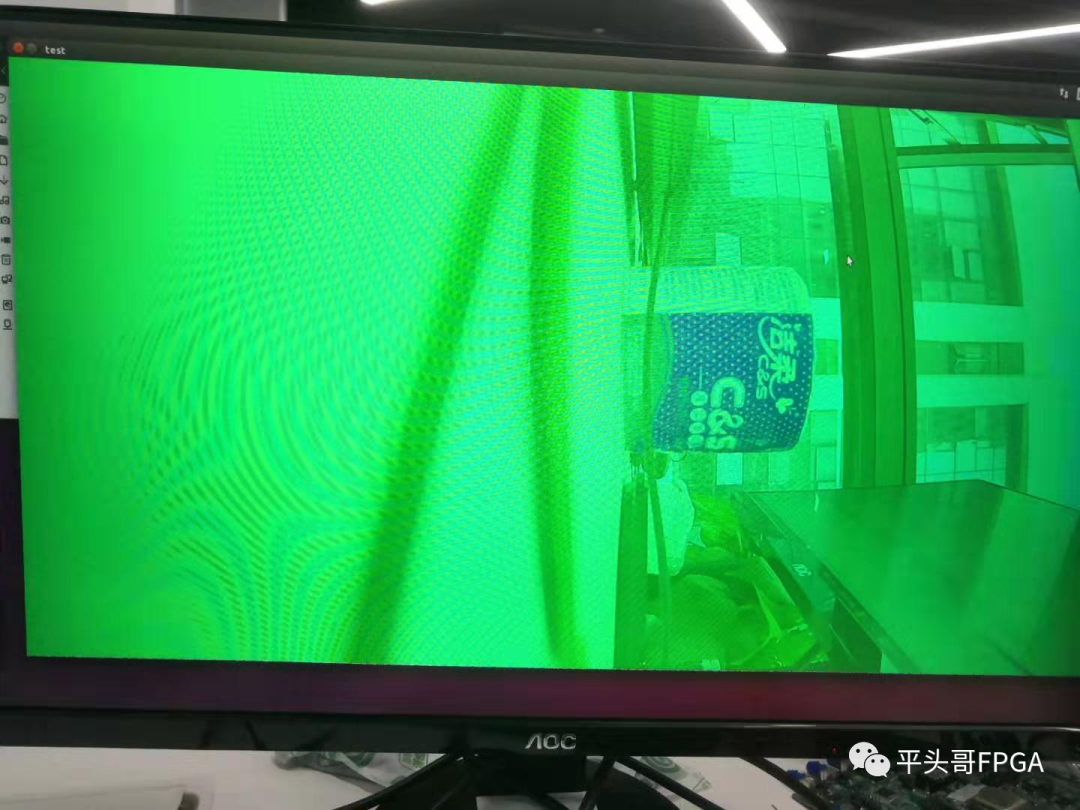

演示的软件搭建包含两个工程,一个用来采集和显示摄像头原图,另外一个工程对摄像头进来的数据做了处理,将像素点中的一个颜色分量置为0,最终显示的图像前景色为绿色。

演示的硬件包含一块5ev的板子,一块图像显示的板子,一台HDMI接口的显示器,一台电脑、一个摄像头,一根fakra接口线、一个Xilinx下载器和一根串口线(非必须,具体的演示环境框图如下:

图 4 演示环境框图

演示结果

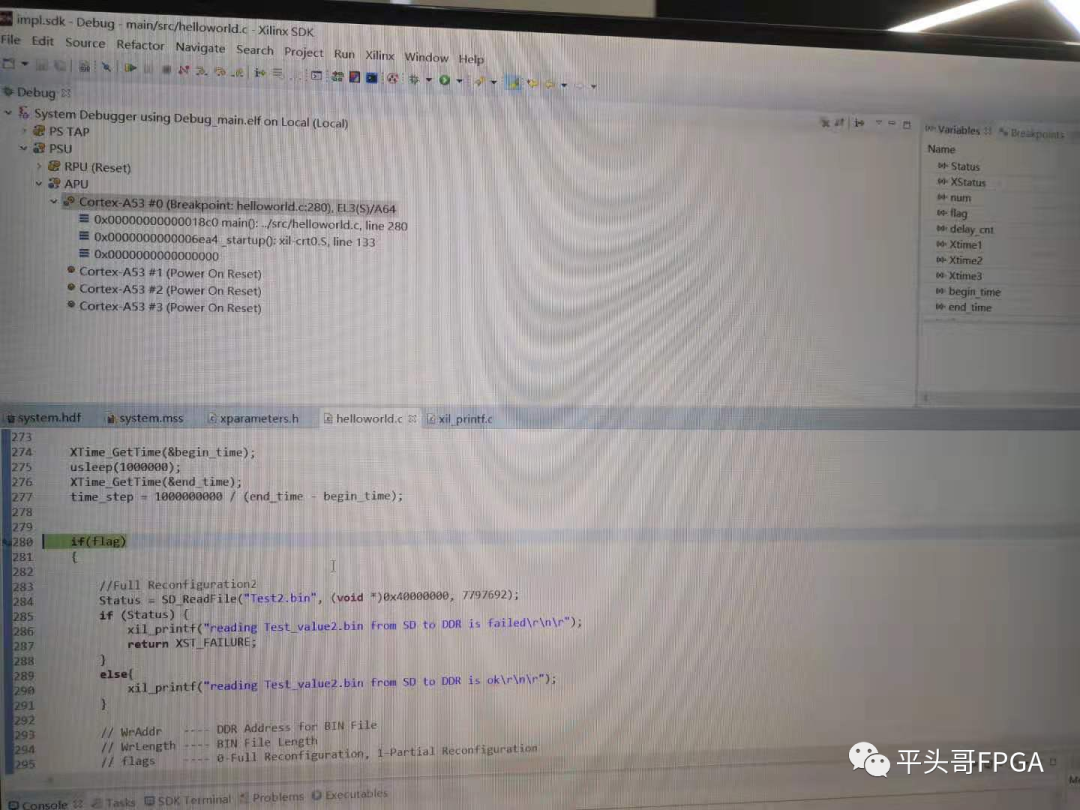

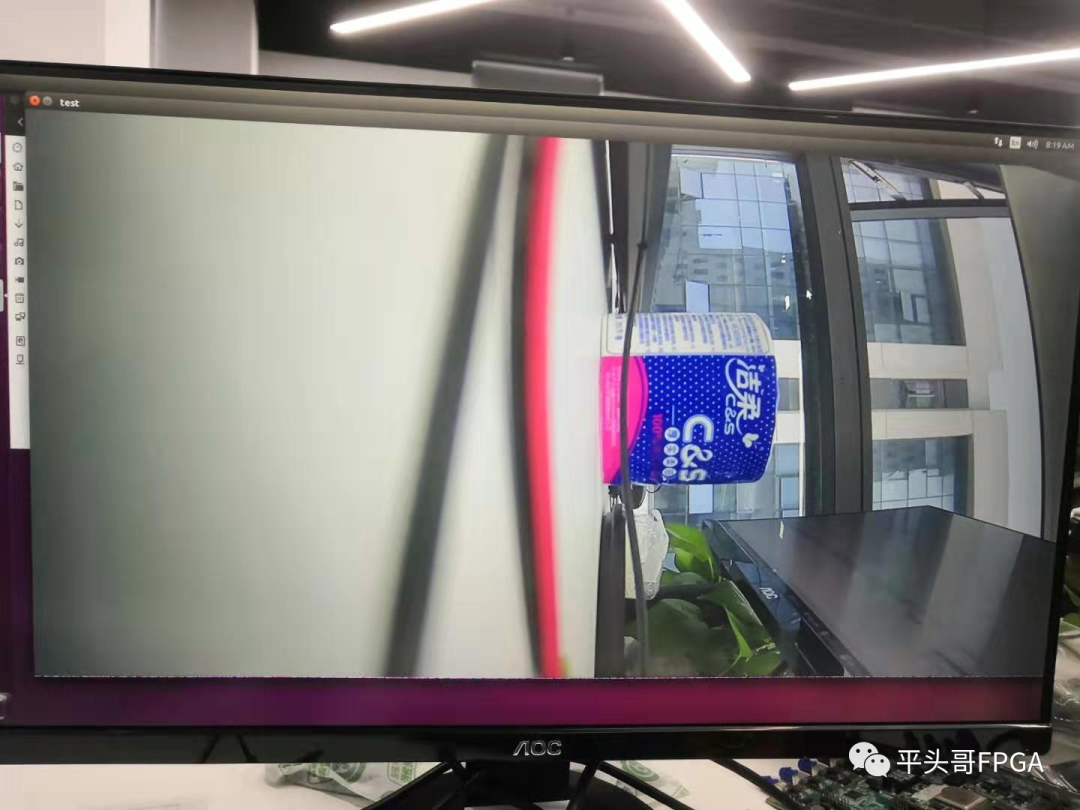

在SDK中下载程序后,在line280行打上断点,如图 5所示,手动控制程序的运行,每运行一次F8,重构一次PL程序,可以看到显示的图像前景色会发生变化,具体运行结果如图 6、图 7所示,以作参考。

图 5 调试断点设置

图 6 Test1.bin运行结果截图

图 7 Test2.bin运行结果截图

审核编辑:刘清

-

关于FPGA可重构技术分析2022-11-03 1442

-

Xilinx FPGA管脚物理约束介绍2022-07-25 6166

-

FPGA动态可重构技术是什么,局部动态可重构的时序问题解决方案2021-07-05 4604

-

怎么实现基于FPGA可重构智能仪器的设计?2021-05-06 1575

-

Xilinx FPGA的FMC介绍2020-01-28 7051

-

采用FPGA实现可重构计算应用2019-07-29 2901

-

如何在FPGA动态局部可重构中进行TBUF总线宏设计2018-12-14 1473

-

Virtex5 FPGA在ISE + Planahead上部分可重构功能的流程和技术要点2018-07-04 4790

-

基于CPLD的FPGA快速动态重构设计2017-11-22 1585

-

Xilinx-FPGA-引脚功能详细介绍2016-09-01 1068

-

【悬赏100块】如何实现FPGA可重构计算(Android平台)2015-05-20 2729

-

xilinx_fpga结构及工作原理介绍2012-08-02 6311

-

FPGA可重构设计的结构基础2011-05-27 3992

全部0条评论

快来发表一下你的评论吧 !