一文讲透SPI总线和IIC总线通信2

电子说

描述

66.6 逻辑分析仪测试UART和IIC

在实际开发过程中,大多数情况下程序代码并不是一写出来就可以正常运行,通常需要查找问题,调试功能。在单片机内部运行的变量和寄存器等参数可以通过在线仿真的方法查看,而单片机外部引脚的运行就要使用示波器或逻辑分析仪来查看了。在分析数字信号以及标准协议信号方面,逻辑分析仪的分析功能比示波器更优一些,下面就采用Kingst LA5016逻辑分析仪,针对6.5节的程序,将UART和I2C信号进行抓取分析。

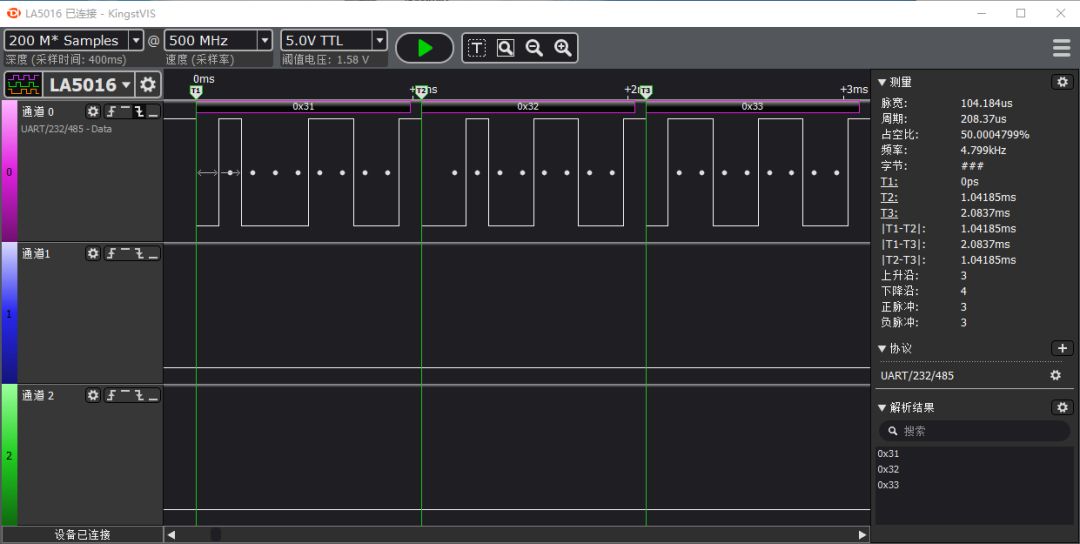

UART数据抓取和解析解码的界面如图6-6所示,从图上可以看出,单个脉冲T1到T2之间的时间差是104us,时间差的倒数就是波特率,也就是9600。当没有信号的时候,通道处于高电平,产生第1个低电平就是起始位,而后是8位数据位,最后是停止位,其中数据位的位置软件都加了白点。最终,软件根据协议设置选项将数据解析出来是0x31,0x32......。

图6-6 Kingst LA5016逻辑分析仪解析UART数据

当串口助手发送读数据指令,读到的数据不正确的时候,首先我们要判断一下是单片机发送错了,还是电脑接收错了,这个时候可以通过分析仪测量一下UART串口通信波形以及解析的数据来判断。如果分析仪抓到的都正确,那就说明发送正确,接收方出现问题。

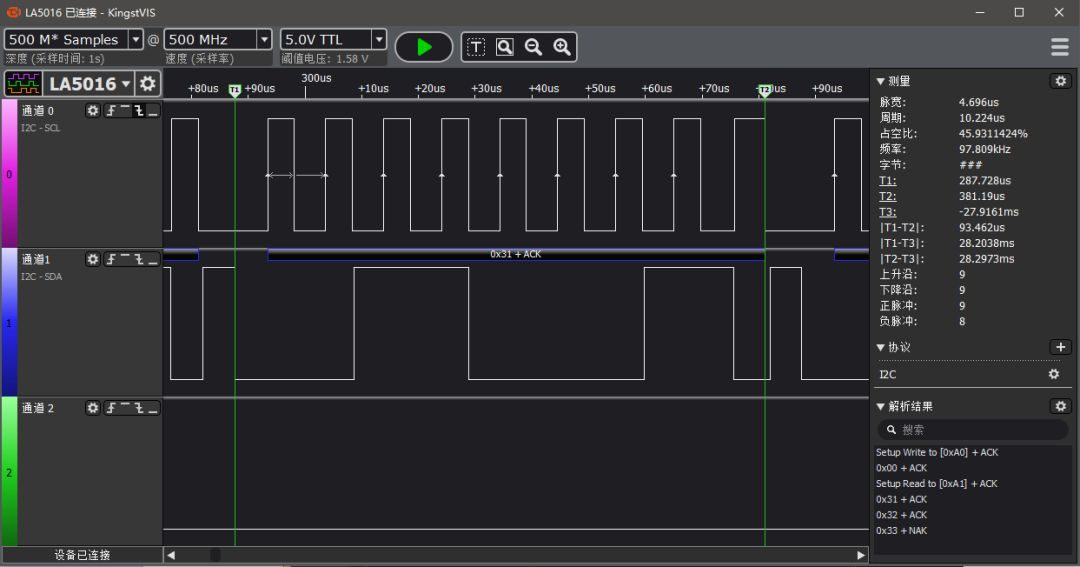

如果分析仪抓取分析的数据,不是单片机想发送的数据,那说明发送错了。既然发送错了,要么是程序问题,要么是从EEPROM读取的数据错了。这个时候需要抓一下从EEPROM读到的数据。采集分析完从EEPROM读到的数据,如果数据正确,那问题可能就出在了读数据后转成UART发送给电脑的程序过程中;如果数据是错误的,那要么是存入EEPROM本来就是错误的,要么是存入正确,读取EEPROM的程序是错误的,如图6-7所示。

图6-7 Kingst LA5016逻辑分析仪解析IIC数据

在图6-7当中,其中通道0是SCL,通道1是SDA。图中可以看出读写时序图,并且可以将读写的数据解析出来,用来判断出从EEPROM读取的数据是否有错。

76.7 初识SPI总线协议

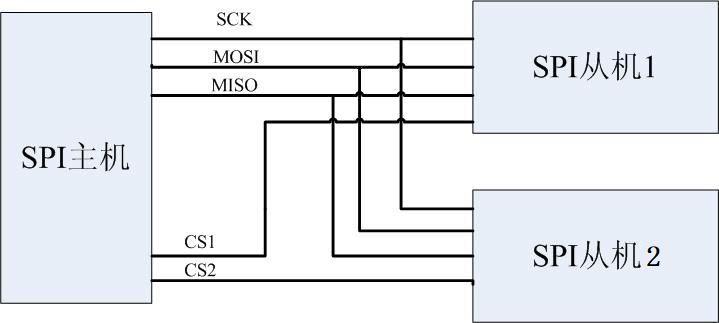

SPI(Serial Peripheral Interface)是一种高速的、全双工、同步通信总线,常用于单片机和EEPROM、FLASH、实时时钟、数字信号处理器等器件的通信。由于其简单实用,数据传输速率较高,被广泛应用于外设控制领域。标准的SPI接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线(MISO)、主机输出/从机输入数据线(MOSI)和从机选择线(CS,也被称作SSEL或NSS)。SPI总线允许一对一或一对多通信,无论哪种方式,通信线路中只允许有一个主机。一对多通信要求从机共用SCK、MISO、MOSI,通过片选CS(NSS)选择使能从机设备。从微观角度上看主机一次只能与一个从机通信,比如主机先与从机1通信,然后再与从机2通信,如此循环,在宏观角度上看就相当于一个主机与两个从机实现通信,如图6-8所示。

图6-8 SPI接口连接示意图

6.7.1 SPI通信原理

SPI总线与前面讲的IIC总线类似,都属于同步通信,即通信双方时必须使用相同的时钟信号;都属于一主多从结构,即总线上只有一个主机,可以挂载多个从机。不同之处在于,IIC属于单工通信,同一时刻只能收或者发,而SPI可以全双工通信,同一时刻既能收又能发,因此SPI的通信速率远远超过IIC,可以达到几十Mbps。此外IIC通信可以由主从设备的任意一方发起,而SPI通信只能由主机发起,从机不能主动与主机通信,因为从机不产生同步时钟信号。

SPI通信本质上是一个串行移位过程。SPI主从设备构成一个环形总线结构,SPI通信的主机一般是单片机,首先主机拉低CS(NSS)信号使能片选,告诉从机开始通信,然后主机开始输出同步时钟信号SCK,主机的移位寄存器通过MOSI移出1位数据,从机的移位寄存器通过该线移入这1位数据;同时从机的移位寄存器又通过MISO线移出1位数据,主机的移位寄存器通过该线移入这1位数据,因此在1个时钟周期内,主从设备的双向移位寄存器通过MOSI和MISO数据线实现了1 bit数据的交换,即双方都发出并接收到1 bit数据。

6.7.2 SPI通信模式

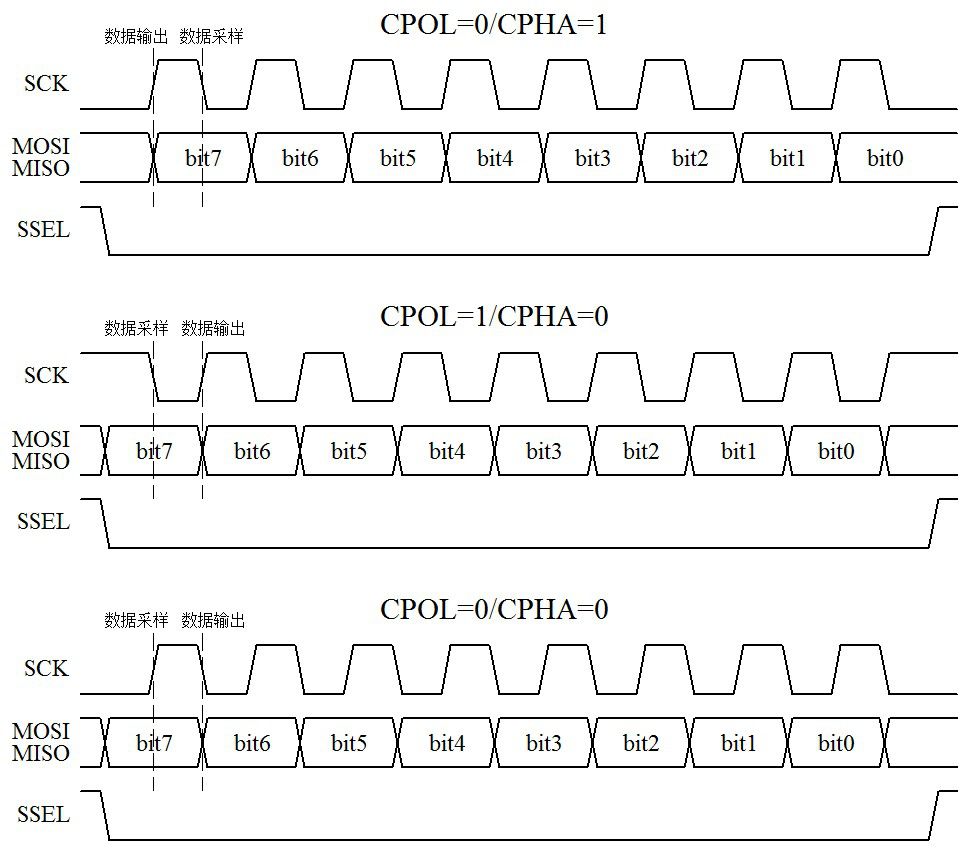

I^2^C总线只有一种通信模式,即当SCL在低电平的时候,向SDA输出数据,当SCL在高电平的时候,对SDA上的数据进行采样。与I^2^C不同的是,SPI总线有四种通信模式,要了解这四种模式,首先我们得学习以下两个名词。

CPOL: Clock Polarity,就是时钟的极性。时钟的极性是什么概念呢?通信的整个过程分为空闲时刻和通信时刻,如果CPOL=1,那么SCLK在数据发送之前和之后的空闲状态是高电平,如果CPOL=0,那么SCK烦人空闲状态就是低电平。

CPHA: Clock Phase,意思是时钟的相位,就是指数据采样发生在第几个时钟边沿, CPHA =0对应着第一个时钟边沿,CPHA =1对应着第二个时钟边沿。

主机和从机要交换数据,就牵涉到一个问题,即主机在什么时刻输出数据到MOSI上而从机在什么时刻采样这个数据,或者从机在什么时刻输出数据到MISO上而主机什么时刻采样这个数据。同步通信的一个特点就是所有数据的变化和采样都是伴随着时钟沿进行的,也就是说数据总是在时钟的边沿附近输出或被采样。而一个时钟周期必定包含了一个上升沿和一个下降沿,这是周期的定义所决定的,只是这两个沿的先后并无规定。又因为数据从产生的时刻到其稳定是需要一定时间的,那么,如果主机在上升沿输出数据到MOSI上,从机就只能在下降沿去采样这个数据了。反之如果一方在下降沿输出数据,那么另一方就必须在上升沿采样这个数据。

CPHA=0,就表示数据的采样是在一个时钟周期的第一个沿上,至于这个沿是上升沿还是下降沿,这要视CPOL的值而定,CPOL=1那就是下降沿,反之就是上升沿。那么数据的采样自然就是在第二个沿上了。

CPHA=1,就表示数据的采样是在一个时钟周期的第二个沿上,同样它是什么沿由CPOL决定。CPOL=1那就是上升沿,反之就是下降沿。

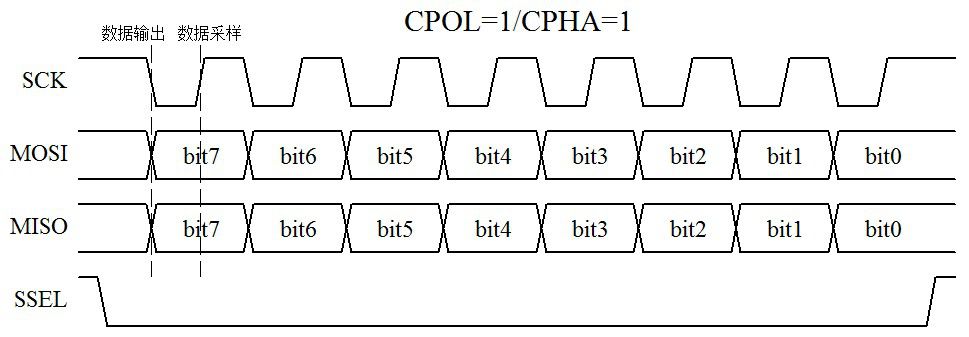

以CPOL=1/CPHA=1,高位在前为例,把时序图画出来给大家看一下,如图6-9所示。

图6-9 SPI通信时序图(一)

如图6-10所示,当数据未发送时以及发送完毕后,由于CPOL=1,因此SCK都是高电平。可以看出,在SCK第一个沿的时候,MOSI和MISO会发生变化,同时SCK第二个沿的时候,数据是稳定的,此刻采样数据是合适的,即一个时钟周期的后沿锁存并读取数据,即CPHA=1。

注意最后最隐蔽的SSEL片选,这个引脚通常用来决定主机是和哪个从机进行通信。剩余的三种模式,直接把图画出来,简化起见把MOSI和MISO合在一起了,可以通过仔细对比加深对SPI通信的理解,SPI剩余三种模式时序如图6-8所示。

需要解释一下CPHA=0时的两种模式时序图,图中数据采样发生在数据输出之前,可能会存在疑问,主机和从机还未输出数据就进行采样?图中所示的数据输出指的是输出第二位数据,即图中所示bit 6 位的数据。那么被采样的数据位是什么时候输出的?其实早在SCK信号由空闲状态转变为有效状态之前,即在SCK的第一个时钟边沿还要早半个时钟周期时,SPI主机就已经开始输出数据了,但是SPI从机却是在片选SSEL置低后开始输出数据,总之SPI设备输出数据要早于SCK,这也是为什么SPI通信时要先使能片选。

图6-10 SPI通信时序图(二)

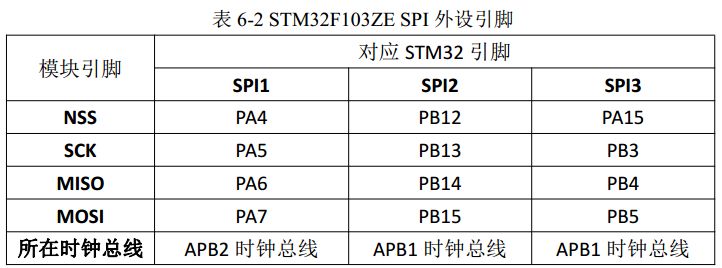

86.8 配置STM32的SPI外设

STM32单片机的SPI接口允许芯片与外部设备以半/全双工、同步、串行方式通信。此接口可以被配置成主模式或从模式,当被配置为主模式时,可以为外部从设备提供通信时钟信号(SCK)。SPI接口拥有8个主模式波特率预分频系数(最大为f PCLK /2,fPCL~~K为挂载SPI外设的APBx的时钟频率)。需要说明的一点,由于APB1的最高频率是36Mhz,APB2的最高频率是72Mhz,SPI波特率预分频系数为2时,位于APB2上的SPI外设理论上最大速率是36MHz,但是实际上由于STM32F103的硬件限制,SPI的最大速率只能达到18Mhz(选型手册也有介绍)。此外,SPI接口还支持硬件的CRC校验,保证通信的可靠性。

6.8.1 SPI引脚

在配置STM32的SPI模块为主机模式时,MOSI引脚是数据输出,而MISO引脚是数据输入。当被配置为从机模式时 MOSI引脚则是数据输入,MISO引脚是数据输出。因此通信时主从设备的MOSI两两相连,MISO两两相连,此外还需要连接SCK和CS(NSS)引脚。

注意:SPI3模块部分引脚与 JTAG引脚共用,这些引脚不受IO控制器控制,它们(复位后)被默认保留为JTAG用途。如果想把引脚配置给SPI3,必须在初始化引脚时关闭JTAG并切换SWD接口,代码为:

GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable, ENABLE);

// JTAG-DP 失能 + SW-DP 使能指令。

NSS:从设备选择。作为“片选引脚”,这是一个可选的引脚,使得主设备可以单独地与特定从设备通讯,避免数据线上的冲突。从设备的NSS引脚可以由主设备的一个标准I/O引脚来驱动,不一定非要SPI外设的NSS引脚,采用普通IO口作为NSS引脚时需要设置NSS引脚模式为软件NSS模式。Kingst-32F1开发板SPI2接口与多路设备通信,其从机的NSS引脚就是STM32的几个普通I/O口,后续用到再详细介绍。

-

IIC总线和SPI总线的比较2023-09-26 3873

-

SPI总线学习笔记2023-09-20 2108

-

一文详解IIC总线2023-06-07 12002

-

浅谈SPI总线通信接口及其协议2023-03-22 3147

-

一文讲透SPI总线和IIC总线通信12023-02-13 3837

-

IIC总线学习笔记2022-01-17 767

-

串行通信中的IIC总线工作原理是什么2021-12-08 1276

-

IIC通信总线寻址2021-12-04 918

-

STC89C52的IIC总线写EEPROM2021-11-25 1008

-

IIC总线和SPI总线通信详解2020-12-23 4833

-

一文解读IIC总线的FPGA实现原理及过程2018-05-31 7328

-

iic总线通信程序2016-03-21 1704

全部0条评论

快来发表一下你的评论吧 !