半导体制造之外延工艺详解

电子说

描述

外延工艺是指在衬底上生长完全排列有序的单晶体层的工艺。一般来讲,外延工艺是在单晶衬底上生长一层与原衬底相同晶格取向的晶体层。外延工艺广泛用于半导体制造,如集成电路工业的外延硅片。MOS 晶体管的嵌入式源漏外延生长,LED衬底上的外延生长等。根据生长源物相狀态的不同,外延生长方式可以分为固相外延、液相外延、气相外延。在集成电路制造中,常用的外延方式是固相外延和气相外延。

固相外延,是指固体源在衬底上生长一层单晶层,如离子注入后的热退火实际上就是一种固相外延过程。离于注入加工时,硅片的硅原子受到高能注入离子的轰击,脱离原有晶格位置,发生非晶化,形成一层表面非晶硅层;再经过高温热退火,非晶原子重新回到晶格位置,并与衬底内部原子晶向保持一致。

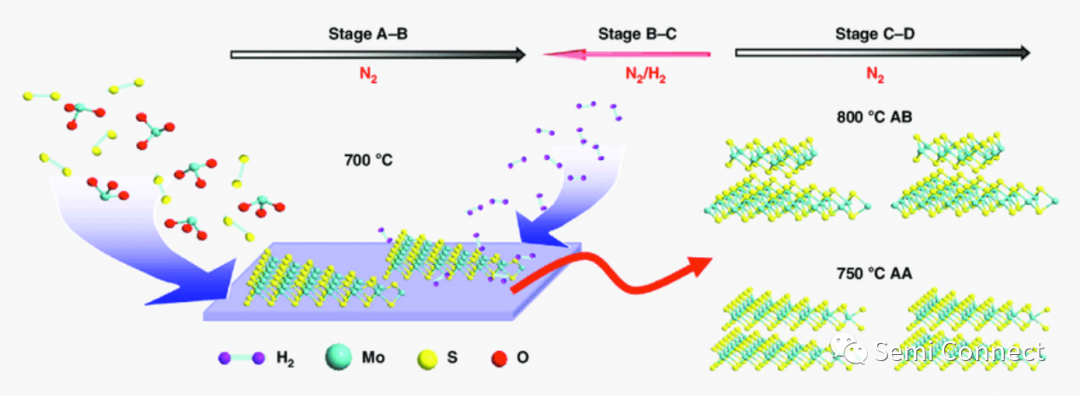

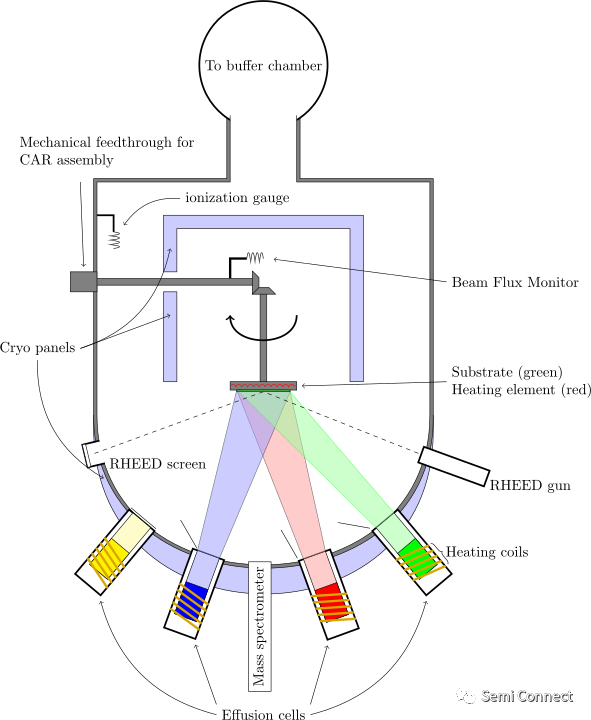

气相外延的生长方法包括化学气相外延生长(CVE)、分子束外延( MBD)、原子层外(ALE)等。在集成电路制造中,最常用的是化学气相外延生长(CVE)。化学气相外延与化学气相沉积(CVD) 原理基本相同,都是利用气体混合后在晶片表面发生化学反应,沉积薄膜的工艺;不同的是,因为化学气相外延生长的是单晶层,所以对设备内的杂质含量和硅片表面的洁净度要求都更高。早期的化学气相外延硅工艺需要在高温条件下(大于 1000°C)进行。随着工艺设备的改进,尤其是真空交换腔体(Load Lock Chamber)技术的采用,设备腔内和硅片表面的洁净度大大改进,硅的外延已经可以在较低温度 (600~700°C)下进行。 在集成电路制造中,CVE 主要用于外延硅片工艺和 MOS 晶体管嵌人式源漏外延工艺。外延硅片工艺是在硅片表面外延一层单晶硅,与原来的硅衬底相比,外延硅层的纯度更高,晶格缺陷更少,从而提高了半导体制造的成品率。另外,硅片上生长的外延硅层的生长厚度和掺杂浓度可以灵活设计,这给器件的设计带来了灵活性,如可以用于减小衬底电阻,增强衬底隔离等。 嵌入式源漏外延工艺是在逻辑先进技术节点广泛采用的技术,是指在 MOS 晶体管的源漏区域外延生长掺杂的锗硅或硅的工艺。引入嵌入式源漏外延工艺的主要优点包括:可以生长因晶格适配而包含应力的赝晶层,提升沟道载流子迁移率;可以原位掺杂源漏,降低源漏结寄生电阻,减少高能离子注入的缺陷。

审核编辑:汤梓红

-

最全最详尽的半导体制造技术资料,涵盖晶圆工艺到后端封测2025-04-15 1784

-

半导体制造工艺之光刻工艺详解2023-08-24 3367

-

#半导体制造工艺 概述电子技术那些事儿 2022-10-15

-

两种标准的半导体制造工艺介绍2022-03-14 8371

-

MEMS工艺——半导体制造技术2021-04-08 4463

-

半导体制造的难点汇总2020-09-02 4926

-

半导体制造教程之工艺晶体的生长资料概述2018-11-19 1531

-

半导体制程2018-11-08 5552

-

半导体制造技术经典教程(英文版)2014-03-06 26541

-

《半导体制造工艺》学习笔记2012-08-20 67978

-

半导体制造2012-07-11 5181

-

想了解半导体制造相关知识2012-02-12 6668

全部0条评论

快来发表一下你的评论吧 !