AIN/AIGaN/GaN MIS异质结构C-V分析

模拟技术

描述

C-V测试是研究绝缘栅HEMT器件性能的重要方法,采用Keithley 4200半导体表征系统的CVU模块测量了肖特基栅和绝缘栅异质结构的C-V特性。

1. C-V曲线及载流子浓度分布

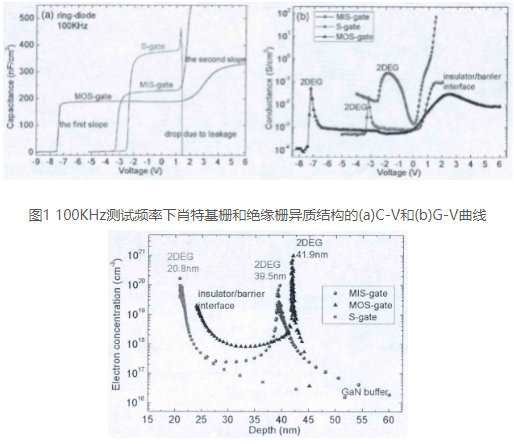

图1给出了肖特基栅、MIS栅、MOS栅异质结构的C-V测试结果,测试频率设定在100KHz,测试中采用电容和电导并联的测试模型。C-V曲线存在两个上升阶段,第一个上升区域对应异质结界面2DEG的积累,对于绝缘栅器件,第一个积累区的电容可以用平板电容近似为势垒层电容和栅绝缘层电容的串联;而第二个上升区域对应载流子在栅绝缘层与势垒层界面的积累,有效积累后电容值应对应于栅绝缘层电容。栅绝缘层的引入使得积累区电容值大幅降低,根据平板电容近似和绝缘层设计厚度值可以推导出PEALD沉积AlN和ALD沉积Al2O3绝缘层的介电常数分别为10和6.7。电压偏置大于1V时,泄漏电流导致肖特基栅结构的C-V曲线急剧下降,这可以从电导曲线中的电导迅速上升看出;采用绝缘栅结构后,电容曲线则没有发生下降,电导曲线在绝缘层势垒层积累区域出现第二个峰值。与直流特性相同,Al2O3栅绝缘层导致了较大的曲线负负向平移,而MIS栅结构的曲线平移量很小。

图2 肖特基栅和绝缘栅异质结的载流子浓度随深度的变化关系

为了提取有源区和绝缘层材料的实际厚度以及材料层中的电子浓度,研究了器件载流子浓度随深度变化的分布曲线,耗尽层宽度(即载流子深度)和载流子浓度分别利用式(49)和(4-10)推导得到,最终得到的三种结构的载流子分布曲线如图2所示。异质结界面2DEG浓度在1020cm-3-1021cm-3量级,非故意掺杂的AlGaN势垒层和GaN缓冲层的背景载流子浓度分别在1018cm-3和1016cm-3量级。对于绝缘栅、MIS栅、MOS栅异质结构,2DEG浓度峰分别出现在20.8nm、39.5nm、41.9nm,说明AIN柵绝缘层和Al2O3栅绝缘层的实际厚度分别为18.7nm和21.1nm,非常接近于设计值20nm。另外可以注意到,AlN栅绝缘层导致2DEG峰值浓度降低,而Al2O3栅绝缘层使2DEG峰值浓度提高。

2. C-V回滞特性

阈值电压不稳定是一直制约氮化物绝缘栅HEMT器件性能提升和实际应用的关键问题,阈值电压不稳定主要表现为I-V或C-V扫描过程的曲线回滞和频散。本文研究了MIS栅和MOS栅异质结构的C-V曲线回滞特性,在100KHz和1MHz两个测试频率下展开研究。图3给出了AIN/AIGaN/GaN MIS异质结构的C-V回滞曲线,测试电压从-6V扫描至绝缘层势垒层积累区域,然后再回扫至-6V,步长为0.1V。正反向扫描的MIS异质结构C-V曲线阈值电压漂移均非常小,100KHz和1MHz下阈值电压回滞分别为45mV和30mV,根据式(4-8)估算的AlN栅绝缘层与Ⅲ-N势垒层界面态密度在1011cm-2量级,与2DEG面密度相比完全可以忽略,所以可以认为采用KOH溶液清洗、原位低损伤等离子体处理、以及PEALD沉积AlN栅绝缘层已经解决了绝缘栅HEMT器件的界面态问题。

图4 (a)100KHz和(b)1MHz测试频率下Al2O3/AlGaN/GaN MOS异质结构的C-V回滞曲线

同时对比研究了MOS栅异质结构的C-V回滞曲线,如图4所示,测试中偏置电压从-8.5V开始向正向扫描,达到正向积累后再回扫至-8.5V。与MIS栅异质结构不同,MOS栅异质结构的C-V曲线回滞表现出较大的测试频率相关性,100KHz频率下阈值电压回滞约0.17V,而1MHz频率下曲线回滞则高达0.89V,估算得到Al2O3栅绝缘层与Ⅲ-N势垒层界面态密度在1011cm-2-1012cm-2量级。

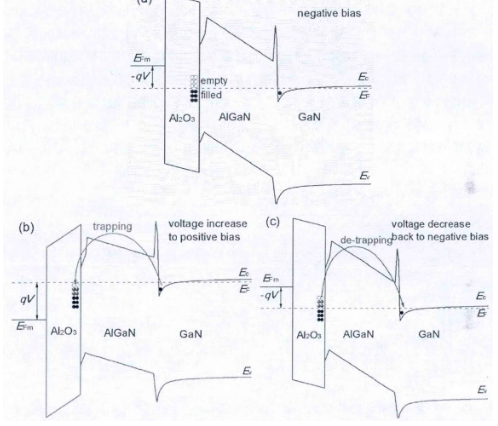

图5 考虑界面态的绝缘栅异质结能带结构示意图:(a)负压稳态偏置下的界面态被电子占据情况:(b)电压增大时界面态充电过程:(c)电压减小时界面态放电过程

绝缘栅异质结构的界面态对阈值电压的影响可结合如图5所示的能带示意图来解释。器件处于图5(a)所示稳态偏置时,费米能级以下的界面态全部被电子填充,而费米能级以上的界面态没有被电子填充:当栅偏置电压增大时,界面态能级相对费米能级降低,低于费米能级的界面陷阱迅速被电子填充,即界面态充电过程,如图5(b)所示;当栅偏置电压减小时,界面态能级相对费米能级提升,充电过程被界面态俘获的电子发射进入导带,即放电过程,如图5(c)所示。但是宽禁带氮化物材料中电子从界面态发射所需的时间随着能级变深可以从几十μs量级增大到小时甚至几天或一个月以上的更长时间,也即偏置电压和能带结构随着电压偏置恢复至图5(a)所示原始状态时,被深能级界面态俘获的电子来不及发射进入导带,导致沟道载流子耗尽和电流/电容值降低,表现为回扫时曲线发生正向平移。与发射时间常数相比,界面态俘获时间常数很短,可以忽略界面态的填充时间,所以C-V曲线回滞电压的大小应该取决于最大正向偏置以及回扫至取样点(本文设为Vth)所需的时间。

对比MOS异质结构在两个频率下的测试曲线,1MHz频率下最大正向偏置在8V,相比于100KHz频率下界面态被填充的程度增大,会导致回扫曲线正向平移更大;而且在电压扫描不长不变的情况下,1MHz测试频率下曲线扫描速度更快,即可供界面态释放电子的时间更短,也会导致曲线漂移量更大。所以,测试频率从100KHz提高到1MHz时曲线回滞电压从0.17V增大到了0.89V。分析1MHz测试频率下电导曲线发现,电压达到7V时电导在绝缘层/势垒层界面积累后再次出现了上升的趋势,I-V测试表明此时器件发生了正向栅击穿,绝缘层中缺陷密度增大,绝缘层体陷阱一般都是深能级陷阱,俘获大量电子,而且曲线回扫过程电子无法从深能级陷阱逃逸,最终导致了高达0.89V的曲线漂移。

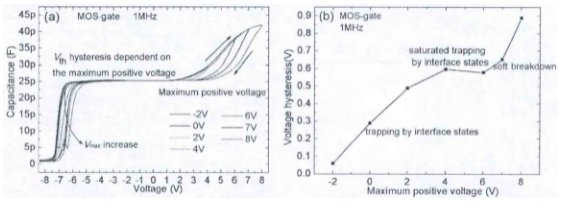

图6 1MHz测试频率下MOS异质结构的(a)C-V回滞曲线和(b)回滞电压随最大栅偏置的变化

为了证明上述分析,进一步研究了最大正偏电压Vmax对MOS异质结构C-V回滞曲线的影响,如图6所示。1MHz测试频率下,MOS结构的C-V曲线回滞量随Vmax增大而变大,这是因为随着Vmax增大,更多的沟道电子被界面态俘获,导致更大的电压漂移;然而对于100KHz测试频率下的C-V回滞曲线,以及MIS异质结构情况,曲线回滞量与Vmax相关性不大,这说明Al2O3绝缘层与氮化物势垒层界面存在较多的深能级界面态,而AlN绝缘层与势垒层界面陷阱密度特别低。图6(b)所示随着Vmax从-2V增大到4V,界面态充电效应使C-V曲线漂移从0.06V增大到0.6V,然后趋于饱和,得出AlO3绝缘层与氮化物势垒层界面深能级陷阱(1MHz C-V测试所能探测的能级范围,仅为界面态总量的一部分)密度约为1.43×1012cm-2。当Vmax大于7V时,绝缘层发生软击穿,击穿激发的体陷阱参与充放电过程,曲线漂移量进一步增大。

3. 变频C-V测试

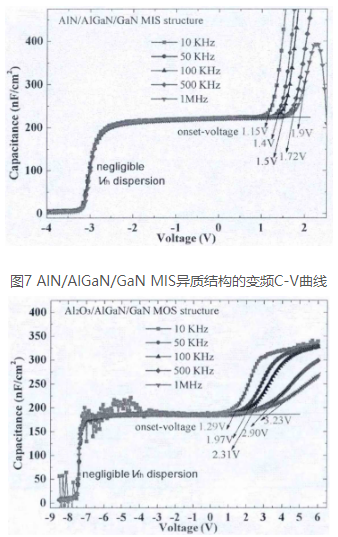

C-V回滞曲线是研究绝缘栅器件界面特性的非常有效的方法,但是如图5(c)所描述的,当器件从正向偏置回扫恢复至负压偏置时,部分被填充的界面态释放电子恢复至本征态,而另一部分深能级陷阱来不及释放电子导致曲线正向漂移,如此利用此曲线回滞量估算的界面态密度没有考虑到回扫过程已经放电的部分,与实际值相比产生了低估误差。本小节利用变频C-V测试对绝缘栅器件界面态进行了更精确的表征,测试频率从10KHz变化至10MHz,MIS栅和MOS栅异质结构的变频C-V测试结果分别如图7和图8所示。栅绝缘层沉积前的KOH溶液清洗和原位低损伤等离子体预处理使绝缘栅异质结构的阈值电压没有明显的频散现象。

图8 Al2O3/AlGaN/GaN MOS异质结构的变频C-V曲线

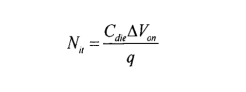

为了估算绝缘栅与势垒层界面态密度,定义了C-V曲线的正向导通电压Von,定义为C-V曲线的第二个上升区域线性拟合与积累区电容线的交点,如图7和图8所示 onset-voltage。在C-V曲线中,随着电压增大异质结界面2DEG从三角形势阱中溢出进入势垒层,耗尽区宽度逐渐减小,当耗尽区边界推进到绝缘层与势垒层界面时,出现载流子的第二次积累。如果绝缘层与势垒层界面存在界面态或固定电荷,会对载流子产生补偿效应,延迟载流子在界面的积累,也即C-V曲线与理论值相比发生正漂;随着测试频率增大,更浅能级的界面态来不及响应交流信号的变化,俘获界面载流子使Von增大,所以利用两个测试频率下C-V曲线的Von变化量可以推导出一定时常数范围内的界面态密度。界面态发射时常数可以表示为1/2πf,其中f指测试频率,当测试频率从f1增大到f2时,可表征的界面态时常数范围为1/2πf2《τc/1/2πf1,界面态密度为,

表1给出了计算得到的MIS栅和MOS栅结构的界面态密度,AlN绝缘层与势垒层界面总界面态密度约为2.78×1012cm-2,而Al2O3绝缘层与势垒层界面态更多,总界面态密度约为4.61×1012cm-2。

表1 变频C-V测得的栅绝缘层与势垒层界面态密度

审核编辑:郭婷

-

如何用半导体参数分析仪进行斜坡法准静态C-V测量?2024-02-22 3005

-

绝缘栅GaN基平面功率开关器件技术2023-04-29 2720

-

Al2O3/AIN/AIGaN/GaN MIS-HEMT器件结构与特性2023-02-14 4517

-

半导体器件C-V特性测试说明2022-05-31 957

-

半导体器件C-V特性测试方案2019-09-27 4194

-

为什么GaN会在射频应用中脱颖而出?2019-08-01 2769

-

松下研发出新型MIS结构的Si基GaN功率晶体管2018-03-15 7671

-

4200A-SCS参数分析仪采用升温速率法实现准静态的C-V测量2017-11-15 1520

-

基于C-V模型的医学图像分割方法2012-05-25 855

-

半导体C-V测量基础(吉时利)2010-03-13 994

-

半导体电容-电压(C-V)测试的方法、技巧与注意事项2010-03-02 847

-

半导体C-V测量基础2009-08-27 5894

全部0条评论

快来发表一下你的评论吧 !