AIN/AIGaN/GaN MIS-HEMT器件直流特性

模拟技术

描述

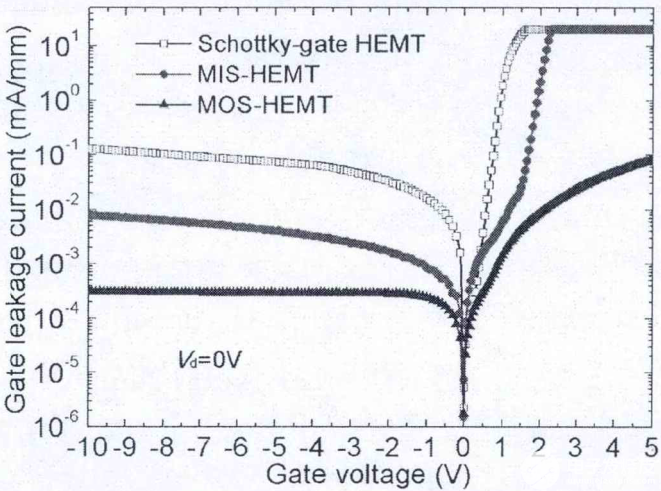

1. 栅漏电分析

关态漏电是制约HEMT器件性能提升的重要因素之一,采用绝缘栅HEMT器件结构可以有效减小器件关态漏电。图1给出了S-HEMT、MIS-HEMT、MOS-HEMT三种器件结构的关态栅漏电曲线,漏极电压Vd设定在0V,反向栅极电压从0V扫描至-10V,正向栅电压扫描至5V。采用AlN和A12O3绝缘层使器件正、反向关态漏电都显著降低,正向导通电压提高,说明栅绝缘层质量良好。AlN栅绝缘层使器件漏电降低1个数量级,而同样厚度的Al2O3绝缘层使器件漏电降低近3个数量级,且栅压偏置在5V时仍然没有发生正向导通,这是因为无定形态的Al2O3薄膜比AlN绝缘性能更好,理想AlN薄膜的电阻率约为1011-1013Ωcm量级,而Al2O3薄膜的电阻率可以高达3×1017cm。另外,Al2O3绝缘层与栅金属之间电子势垒更高,以及Al2O3材料生长工艺更加成熟,都会导致MOS棚结构抑制漏电效果更好。

图1 肖特基栅和绝缘栅HEMT器件的关态栅泄漏电流

2. 转移与输出特性

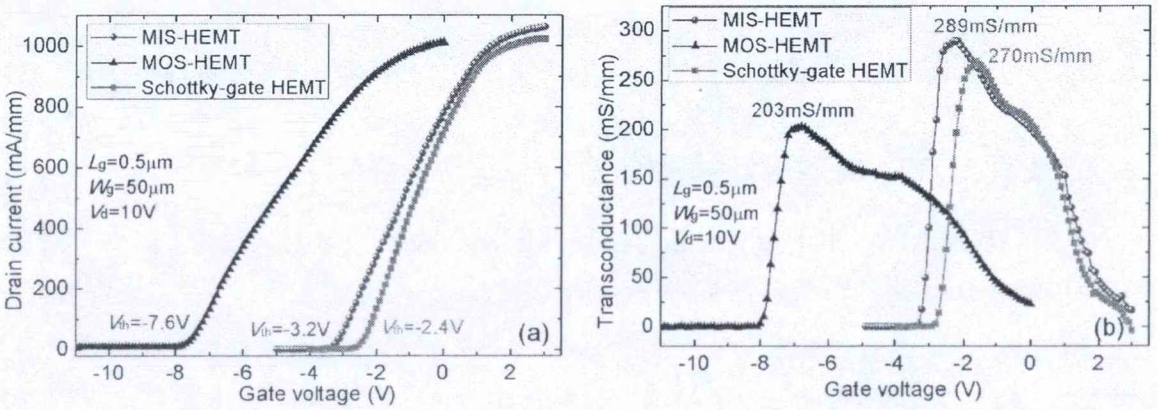

利用Keithley 4200半导体表征系统对器件的输出和转移特性进行了测试分析,三种器件结构的转移和跨导曲线如图2所示,测试中漏压偏置为10V。肖特基栅HEMT、MIS-HEMT、及MOS-HEMT的阈值电压分别为-2.4V、-3.2V、-7.6V,20mm厚的Al2O3栅绝缘层使器件阈值电压负向漂移了4.4V,这一阈值漂移量与文献报道结果类似;然而,对于MIS-HEMT器件,同样厚度的AlN栅绝缘层导致的阙值电压负漂量仅为0.8V。考虑到Al2O3和AlN材料的介电常数相近,即MIS-HEMT和MOS HEMT中栅电容对栅偏置的分压效果是相当的,所以高达3.6V的阈值电压差应归因于两种栅绝缘层材料与氮化物势垒层之间界面特性存在明显差异,在后面文章中我们将对栅绝缘层与氮化物势垒层之间的界面性能进行分析。栅绝缘层沉积前的KOH溶液清洗和原位低损伤等离子体表面预处理有效减少了绝缘层与势垒层界面的陷阱密度,MIS-HEMT和MOS-HEMT器件的阈值电压回滞量仅为54mV和93mV。

场效应晶体管跨导表示栅对沟道的控制能力,本征跨导与栅电容和沟道载流子迁移率相关,非本征跨导还与器件源、漏串联电阻相关。HEMT器件处于关态时,沟道无载流子流动,载流子迁移率和跨导为零;栅电压一旦大于阈值电压,器件开启并迅速在异质结界面积累高密度的2DEG,2DEG不受缓冲层和势垒层材料电离杂质散射的影响,具有极高的迁移率值,器件跨导达到峰值;当器件栅压继续增大,沟道载流子速度达到饱和并溢出三角形势垒进入势垒层,此时载流子迁移率包含2D和3D两个分量,势垒层的电离杂质散射作用使载流子迁移率和跨导降低,如图2(b)所示。

釆用绝缘栅结构后,栅到沟道距离增大,栅控能力减弱,栅电容和跨导值会相应减小,肖特基栅HEMT器件的峰值跨导为270mS/mm,而MOS-HEMT器件的跨导值则大幅降低到203mS/mm,这与大量文献报道结果相符。AlN栅绝缘层的引入不但没有减小器件跨导,反而使MIS-HEMT器件峰值跨导提高到了289mS/mm,这只能解释为PEALD沉积的AlN栅绝缘层使栅下区域沟道载流子迁移率和电子速度显著提高。PEALD沉积的AIN绝缘层使异质结沟道载流子迁移率提高了一倍多,这完全可以补偿栅电容减小导致的跨导降低量;而ALD沉积的Al2O3绝缘层使载流子迁移率提高量有限,最终栅电容减小导致MOS-HEMT器件跨导值降低。

图2 肖特栅和绝缘栅HEMT器件的(a)转移和(b)跨导特性曲线

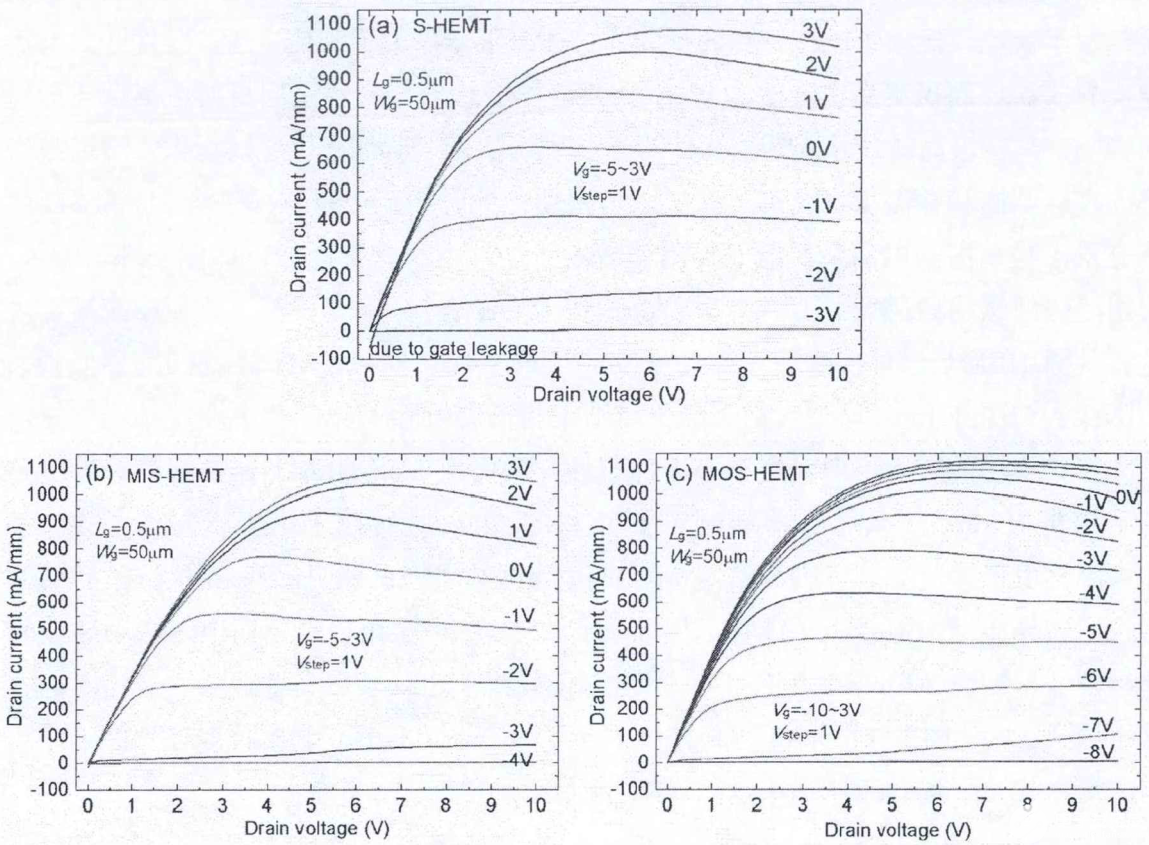

图3给出了三种器件结构的输出曲线,漏压从0V扫描至10V,栅压从关态偏置步进至3V,步长为1V。制作在蓝宝石衬底上的AIGaN/GaN HEMT器件饱和输出电流高于1A/mm,栅压为3V时S-HEMT、MIS-HEMT、MOS-HEMT的饱和输出电流分别为1078mA/mm、1085mA/mm、1123mA/mm。如此高的饱和输出电流可以与SiC衬底上器件或高铝组分势垒层器件性能相比拟,但是蓝宝石衬底上器件自热效应使大漏压偏置时输出曲线下降。另外,对于肖特基栅HEMT器件,栅压偏置为3V时,较大的栅极泄漏电流导致0V漏压偏置时输出负电流,而绝缘栅HEMT器件则没有出现这一现象,也即对于绝缘栅HEMT器件栅压可以偏置在更大值。

图3 AIGaN/GaN HEMT器件输出特性曲线:(a) S-HEMT、(b) MIS-HEMT、(c) MOS-HEMT

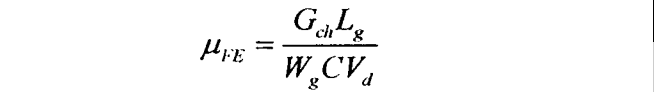

3. 2DEG场效应迁移率分析

为了解释PEALD沉积AlN栅绝缘层导致的器件跨导异常增大现象,本文对比研究了三种器件结构的场效应迁移率μFE随沟道载流子密度的变化关系。器件的场效应迁移率可以通过跨导测试推导得到,当场效应晶体管器件工作在线性区时(漏电压偏置Vd非常小),沟道载流子迁移率μFE与沟道电导Gch之间存在下述关系,

其中电容C用环形二极管结构测量得到。本文采用大栅长的Fat-FET结构推导沟道电导,因为相比于常规HEMT器件结构,fat-FET结构可以减小源、漏串联电阻的影响,沟道电导近似等于器件跨导值。Fat-FET的栅长设计为30μm,栅宽为100μm,漏压偏置在0.1V时的器件跨导曲线如图4所示。绝缘栅、MIS栅、MOS栅器件的峰值沟道电导分别为2. 1mS/mm、2.5mS/mm、1.6mSmm,Al2O3栅绝缘层使沟道电导大幅降低,而AlN栅绝缘层却使其有所提高。另外,MIS栅和绝缘栅结构的线性度比MOS栅器件更好,其跨导曲线半高宽高达2.7V,而MOS栅器件的沟道电导在达到峰值后急剧减小,曲线半高宽仅为0.9V。

图5 肖特基栅和绝缘栅异质结沟道2DEG面密度随栅压的变化关系

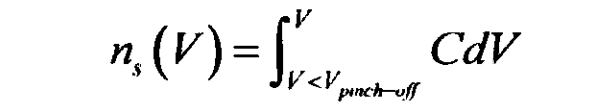

肖特基栅和绝缘栅异质结构器件的沟道2DEG面密度通过对C-V曲线积分得到,

其中Vpinch-off指沟道关断电压。对环形二极管结构的C-V积分结果如图5所示,沟道2DEG面密度在1012cm-2-1013cm-2量级,符合实际情况。ALD沉积的Al2O3栅绝缘层使沟道载流子密度有所提高,而PEALD沉积的AlN栅绝缘层导致载流子密度降低。

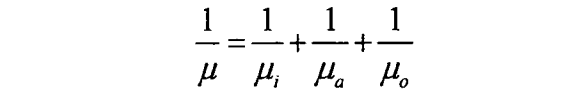

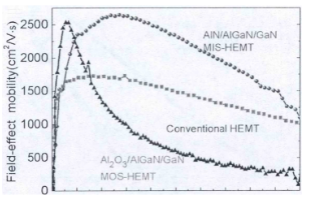

图6给出了根据式(5-1)得到的器件场效应迁移率随2DEG面密度的变化关系。PEALD沉积AIN栅绝缘层使沟道迁移率大幅提高,而且随着2DEG密度提高载流子迁移率缓慢下降,这导致MIS-HEMT器件具有较高的峰值跨导和很好的跨导线性度。对于MOS-HEMT器件,虽然其载流子迁移率峰值高达2533cm2/V·s,但是随着载流子面密度的增加迁移率急剧减小,这可能是因为在大栅压偏置下3D输运受电离杂质散射影响较大导致总迁移率减小。对于氮化物等极性半导体,载流子迁移率主要受远程电离杂质散射μi、声学声子散射μa、光学声子散射μo的影响,利用玛西森定律( Matthiessen rule)可以将沟道总迁移率表示为,

当薄层载流子密度低于5×1012cm-2时,绝缘栅异质结构的沟道迁移率由栅绝缘层与氮化物界面电荷的远程杂质散射主导,所以我们可以推断MOS-HEMT结构的沟道迁移率下降和跨导降低来源于Al2O3与势垒层界面电荷的远程电离杂质散射作用。

图6 肖特基栅和绝缘栅HEMT器件场效应迁移率随2DEG面密度的变化关系

审核编辑:郭婷

-

增强AlN/GaN HEMT2025-06-12 1136

-

改善GaN HEMT功率器件的短路耐受时间2024-05-09 2448

-

GaN HEMT为什么不能做成低压器件2023-12-07 2284

-

基于GaN HEMT的半桥LLC优化设计和损耗分析2023-09-18 1763

-

实测干货分享!1200V GaN HEMT功率器件动态特性测试2023-07-17 2551

-

GaN单晶衬底显著改善HEMT器件电流崩塌效应2023-06-14 4478

-

绝缘栅GaN基平面功率开关器件技术2023-04-29 2712

-

Al2O3/AIN/AIGaN/GaN MIS-HEMT器件结构与特性2023-02-14 4508

-

绝缘栅HEMT器件界面固定电荷分析2023-02-13 3491

-

分析毫米波GaN器件热电效应2022-09-08 3209

-

GaN HEMT增强型器件技术路线及关键科学问题2020-10-09 12397

-

GaN HEMT可靠性测试:为什么业界无法就一种测试标准达成共识2020-09-23 4544

-

GaN HEMT在电机设计中有以下优点2019-07-16 3324

全部0条评论

快来发表一下你的评论吧 !