AlN/AIGaN/GaN MIS-HEMT器件制作

模拟技术

描述

1.器件结构与工艺

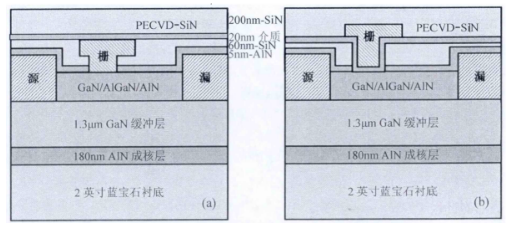

绝缘栅和肖特基栅HEMT器件结构如图1所示, AlGaN/GaN异质结采用MOCVD技术在2英寸c面蓝宝石衬底上外延得到,由下往上依次为180nm高温AlN成核层、13μm非掺杂GaN缓冲层、1nm AlN界面插入层、22nm AlGaN势垒层、及2nm GaN帽层,势垒层铝组分设定为30%。室温Hall效应测试显示,异质结材料沟道2DEG面密度和迁移率分别为7.2×1012cm-2和2105cm2/V·s,方阻约为410Ω/sq,整个圆片上材料方阻非均匀性在5%以内。

图1 (a) AlGaN/ GaN肖特基栅和(b)绝缘栅HEMT器件横截面结构及尺寸示意图

器件工艺中首先制作Ti/Al/Ni/Au源、漏欧姆接触,然后采用RIE刻蚀台面实现有源区隔离,TLM测试得到欧姆接触电阻Rc=0.33Ω·mm,方阻Rsq=455Ω/sq。器件表面钝化层采用双层材料,首先利用PEALD沉积5nm的AlN界面插入层( 1st layer),然后利用PECVD沉积60nm的SiN介质( 2nd layer)加厚表面钝化层。在栅电极制作和第三层绝缘材料(3rd layer)沉积之前,利用RIE刻蚀移除栅接触下方的SIN/AIN材料,定义出栅长Lg=0.5μm的栅电极区域,栅-源间距Lgs和栅-漏间距Lgd分别为0.9μm和2.6μm。对于绝缘栅器件,釆用原子层沉积技术实现栅绝缘层沉积,然后完成Ni/Au/Ni栅电极接触,采用T型栅结构;对于肖特基栅器件,则首先完成栅电极制作,然后沉积第三层绝缘材料。为了改善栅绝缘层和电极接触性能,减少绝缘材料中的缺陷,在450℃的N2气氛中对所有器件进行了5min的快速热退火处理。最后,采用PECVD沉积第四层绝缘材料200nm SiN(4th layer),并完成源场板的制作。

为了进行对比研究,共制作了三种栅结构的器件:肖特基栅HEMT器件,记为S-HEMT;采用PEALD沉积AlN栅绝缘层的绝缘栅HEMT器件,记为MIS-HEMT;采用ALD沉积Al2O3栅绝缘层的绝缘栅HEMT器件,记为MOS-HEMT。三种结构除了栅电极制作步骤和表面绝缘层材料的差异,其余器件结构和工艺参数是相同的。三种器件的表面钝化层材料都是SIN/AIN双层结构,第四层场板介质则是200nm的SiN;对于S-HEMT,栅电极在第三层绝缘材料沉积前制作,而对于MIS-HEMT和MOS-HEMT,栅电极则在栅绝缘层材料沉积后制作;对于MIS-HEMT器件,栅绝缘层材料为20nm的PEALD沉积AlN,而对于S-HEMT和MOS-HEMT,第三层绝缘材料或栅绝缘层材料是20nm的ALD沉积Al2O3。

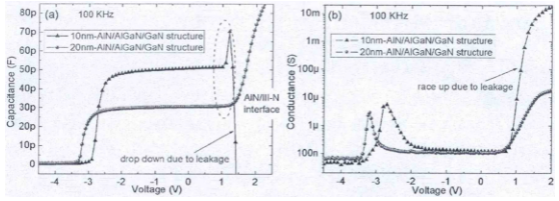

有一点需要说明的是,绝缘栅器件中一般栅绝缘层厚度达到10nm即可足够在应用中抑制棚漏电,但是本文却设计栅绝缘层厚度为20nm。这是因为C-V测试和后面文章界面态分析中,需要使栅偏置在绝缘层/势垒层界面积累区域,如果栅绝缘层厚度较小,在如此大栅压偏置下电容曲线会出现如图5.2(a)所示的电容急剧降低,而栅绝缘层厚度在20nm时则可实现良好的载流子界面积累。在大栅压时电容下降是因为高频下绝缘层薄膜导通能力增强,产生漏电通道,绝缘层两端电荷量流失,这从图5.2(b)电导随着电压的变化曲线中可以看出来,栅绝缘层厚度为10nm时,大栅压下绝缘层漏电表现为在绝缘层/势垒层积累区域电导值急剧上升,而采用20nm厚的栅绝缘层则可有效抑制此时的漏电。由于本文采用C-V和电导法进行界面态分析,大栅压偏置时的漏电会对实验电容、电导值产生影响,导致定量分析误差。文献报道中涉及界面分析和大栅压下C-V测试时,绝缘栅HFMT器件的栅绝缘层厚度一般都设计在20mm以上,甚至有些文献中采用厚度达40nm的栅绝缘层保证漏电抑制效果。结合文献报道和图2结果分析,采用栅绝缘层厚度为20nm进行界面分析。

图2 栅绝缘层厚度对MIS异质结构(a)C-V和(b)G-V曲线的影响

2. 栅绝缘层沉积

界面处理和栅绝缘层沉积是绝缘栅HEMT器件的关键工艺,本文利用优化工艺实现了高界面质量和高性能的栅绝缘层沉积。表面钝化层和栅绝缘层沉积之前,需要对AlGaN/GaN表面进行处理,依次采用非原位的化学清洗和原位的低损伤等离子体表面预处理工艺。化学清洗过程中,利用丙酮、乙醇清洗表面有机杂质,然后利用KOH溶液处理表面无机杂质;原位预处理则采用NH3/N2混合气氛等离子体技术,RF功率设定为200W,处理时间为5min。

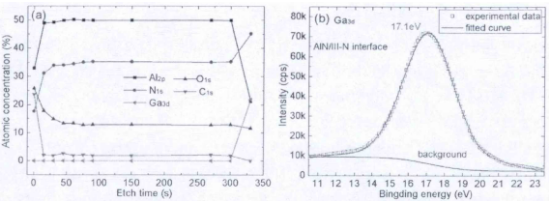

MOS-HEMT器件中的Al2O3栅绝缘层利用热型ALD技术制备,前驱体源采用TMA和H2O,沉积温度为300C。器件表面AlN钝化层和MIS-HEMT中的AlN栅绝缘层利用PEALD技术制备,前驱体源采用TMA和NH3,RF功率设定为150W,沉积温度为300℃。图3给出了异质结衬底上沉积的20nm AlN薄膜的XPS分析结果,薄膜表面受空气氧化和碳吸附影响,体内氧杂质含量约为13%,碳杂质含量极低,Al/N原子比约为1.4。绝缘层/势垒层界面处Ga3d高分辨率扫描拟合结果对应于Ga-N建核心峰,说明介质沉积前的表面等离子体处理减少了界面氧含量,有效移除了低质量的界面氧化层。

图3 (a)AlN/AlGaN/GaN薄膜的XPS组分随深度的变化及(b)界面处Ga3d高分辨XPS分析

审核编辑:郭婷

-

GaN HEMT器件的结构和工作模式2025-09-02 4954

-

增强AlN/GaN HEMT2025-06-12 1136

-

GaN HEMT有哪些优缺点2024-08-15 4645

-

改善GaN HEMT功率器件的短路耐受时间2024-05-09 2448

-

GaN HEMT为什么不能做成低压器件2023-12-07 2284

-

基于GaN HEMT的半桥LLC优化设计和损耗分析2023-09-18 1763

-

GaN单晶衬底显著改善HEMT器件电流崩塌效应2023-06-14 4480

-

绝缘栅GaN基平面功率开关器件技术2023-04-29 2712

-

Al2O3/AIN/AIGaN/GaN MIS-HEMT器件结构与特性2023-02-14 4508

-

绝缘栅HEMT器件界面固定电荷分析2023-02-13 3491

-

GaN HEMT增强型器件技术路线及关键科学问题2020-10-09 12397

-

GaN HEMT可靠性测试:为什么业界无法就一种测试标准达成共识2020-09-23 4544

-

GaN HEMT在电机设计中有以下优点2019-07-16 3325

-

MIS器件,MIS器件是什么意思2010-03-04 1690

全部0条评论

快来发表一下你的评论吧 !