排序电路提供伪电压跟踪器

描述

本应用笔记介绍了三种跟踪电源轨之间电压的方法。特色电路也是最简单的方法,采用MAX6819电源排序器,执行开环电压跟踪。

现代微控制器、DSP 和 ASIC 需要多个电源电压才能正常工作。凭借更高的速度和更好的处理能力,这些器件的电压和制造几何尺寸已缩小,以最大限度地降低功耗和芯片空间。因此,如果电源轨之间的差分电压的绝对值在上电或断电期间超过规定的容差,则许多数字IC容易受到内部击穿的影响。由此产生的应力会立即损坏 IC,或者会一直潜伏到以后,从而引入可靠性问题。

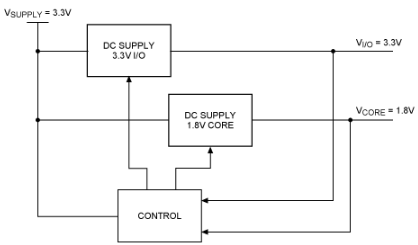

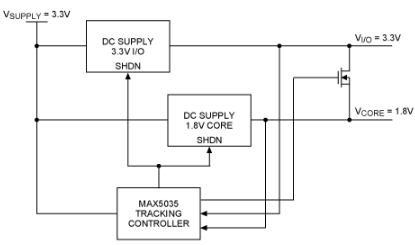

各种电压跟踪技术可以消除这个问题。例如,系统可以通过测量和主动匹配每个电源轨的电压与时间曲线来控制电源的跟踪(图 1a)。在另一种闭环方法中,并联架构(图1b)在上电和断电期间暂时将电源轨短路在一起。分流方法可减少正常工作期间 MOSFET 两端的功率损耗,当 MOSFET 处于关断状态时。

图 1a.这种电压跟踪架构控制独立 DC-DC 稳压器的反馈。注意: 这些端子的名称以及控制块调整输出电压的方式取决于电源内部的电路。

图 1b.这种用于电压跟踪的闭环分流架构可降低功率损耗。MAX5035 DC-DC转换器用作跟踪控制器。

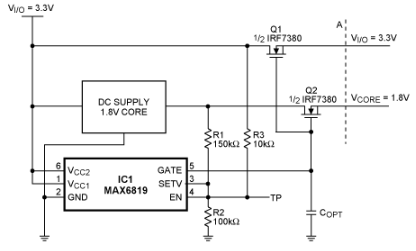

在某些情况下,更简单的开环跟踪器可能就足够了。电源排序器电路(IC1,图6819中的MAX2)可以配置为执行电压跟踪功能。与闭环方法不同,这种方法不会使电源轨短路,也不需要控制DC-DC稳压器的反馈环路。

图2.电压排序器(MAX6819)通过同时控制n沟道MOSFET来强制跟踪内核和I/O电压。

当 MOSFET 关断时,内核和 I/O 电源电压关断(图 2)。然后,当SETV监控的电压超过其阈值时,内部电荷泵产生一个电压(GATE输出),同时增强n沟道MOSFET的栅极。如果这两个开关的漏极电压相距在几伏以内,并且漏极电流不太相差,则 VI/O和 V核心随着公共栅极电压的升高,电压一起上升(图 3)。电源轨之间的差值约为200mV,这是由所用FET的栅极导通电压略有差异引起的。为了增加斜坡时间,可以在GATE输出端增加一个小电容(C选择) 以降低压摆率。

图3.这张示波器照片说明了V的跟踪I/O(上迹线)和 V核心在图2的电路中,其中VI/O= 3.3V, V核心= 1.8V,两个负载均调节至1A。

图2电路还可以监视电源电压。如果 3.3V 电源轨降至约 2V 以下,或者 1.8V 电源轨低于 R1/R2 分压器设定的门限,则 GATE 输出变为低电平并关断两个 MOSFET。电阻R1和R2确定实际关断电平。(显示的值监视1.8V电源轨。您可以通过使能输入(EN)拉低来关闭电路。

作为奖励,电路在响应短路负载后自动“重试”。如果短路出现在虚线的右侧(图2中的“A”),则其中一个或两个电源的崩溃会打开开关,并将两个负载与电源电压断开。先前短路的电源轨返回,MAX200内置6819ms延迟再次闭合开关,在延迟后测试负载。此负载测试以 200ms 的间隔持续进行,直到短路消失或电源关闭。

审核编辑:郭婷

-

在 VisionFive 2 上使用线跟踪器2026-03-05 110

-

LTC2926:MOSFET控制的电源跟踪器的全面解析2026-02-28 315

-

低电压三重热插拔控制器/电源排序器/电压跟踪器:MAX5930的应用与设计2026-02-10 560

-

高抗噪性 电压跟踪器jf_30741036 2024-09-29

-

什么是电压跟踪器?2023-12-07 2023

-

光子时间跟踪器开源分享2022-12-28 741

-

迈向Arduino驱动的卫星跟踪器2022-12-01 837

-

移动水位跟踪器开源分享2022-11-21 827

-

使用Raspberry Pi的温度跟踪器2022-11-11 700

-

使用Arduino的光跟踪器2022-11-01 898

-

FBI秘密跟踪器是什么2020-04-23 2408

-

2/3通道电源跟踪器/排序器/监控器2010-04-09 929

-

峰值跟踪器电路图2009-07-02 1119

-

基于双DSP的电视跟踪器2009-05-08 821

全部0条评论

快来发表一下你的评论吧 !