显示半导体将从2nm节点继续缩放,2036年将达到更高的密度

光电显示

描述

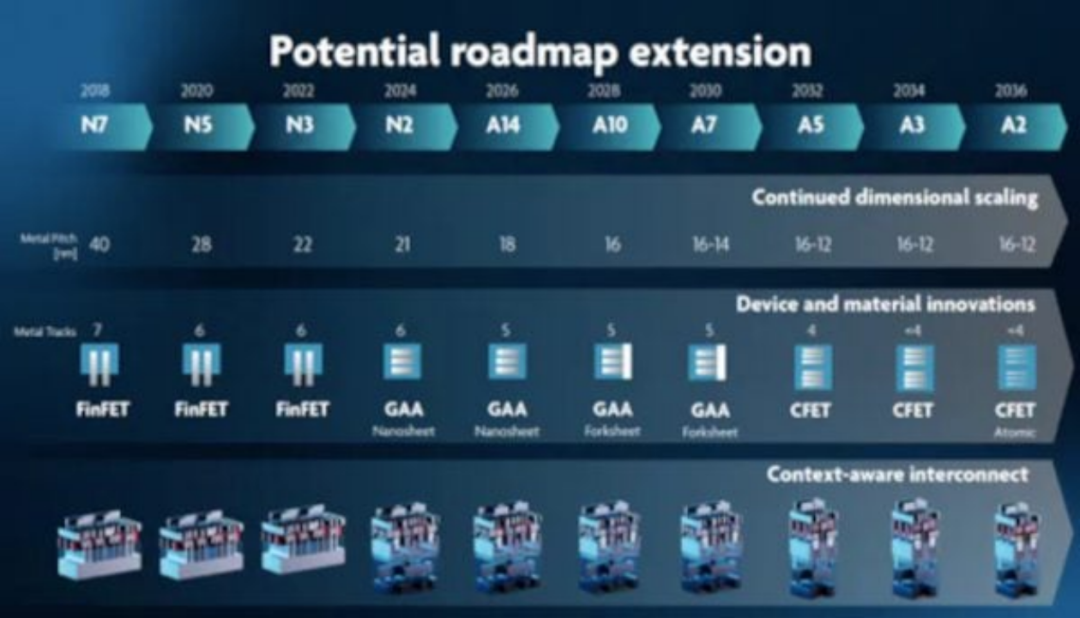

IMEC 表示今后金属间距缩放成功的关键将是采用新颖的晶体管结构、电路架构和材料。 IMEC研究所发布了一张路线图,显示半导体将从2nm节点继续缩放,到2036年将达到更高的密度。虽然路线图上显示晶体管和材料创新将在埃米时代继续,但其实到 2030 年,金属间距缩放将在 16 纳米至 12 纳米左右结束。

IMEC 是世界领先的半导体制造独立研究机构,它指出半导体技术的扩展将变得更加复杂。就电路密度而言,摩尔定律可以继续下去。

该路线图包含 IMEC 已经发布的许多想法,又讨论了将“整体感知互连”作为改进未来电路架构的一种方式的想法。IMEC 观察到,这样做的必要性很大,因为社会预计会产生大量且不断增加的数据。这项任务也很困难,许多与缩放相关的参数都达到了极限。

IMEC 将这五道困难“墙”称为必须同时克服的。与多变量问题的情况一样,一个轴上的进展通常是以另一个轴上的进展为代价的。

五道困难“墙”是:

支持光刻的缩放

内存带宽

电力输送和冷却

芯片制造的可持续性

成本

IMEC 表示成功的关键将是采用新颖的晶体管结构、电路架构和材料。

IMEC 半导体路线图。来源:IMEC

转向高数值孔径极紫外光刻技术也是关键,预计 ASML 将在 2023 年推出第一个原型,并在 2025 年或 2026 年投入大批量生产。

IMEC 已经对晶体管结构方面的 FinFET 之后的内容进行了大量思考。英特尔、三星和台积电正在 3nm 和 2nm 采用其一些想法,例如纳米片环栅晶体管。

forksheet 晶体管是 imec 的发明,甚至比 nanosheet 晶体管更密集,将 gate-all-around 概念扩展到 1 nm 一代。forksheet 架构在负通道和正通道之间引入了屏障,使通道更加靠近。该架构有望使单元尺寸缩小 20%。

Forksheet 然后 CFET

在 Forksheet 晶体管之后是互补 FET (CFET),它在 GAA 的结构上体现了 CMOS 架构的一些优点。这提高了电路密度,但以工艺复杂性为代价。随着 CFET 的引入,工业界可能已准备好部署二维单层材料,例如二硫化钨或二硫化钼。这些应该会带来改进的性能和降低的功耗。

与此同时,IMEC 之前已经提出了使用埋入式电源轨在 IC 周围分配电源的想法,而不是与 IC 顶部的信号线竞争空间。电源轨将沉入晶圆,并使用更宽、电阻更小的材料中的纳米硅通孔连接到背面。

将内存与处理单元分开的经典冯诺依曼架构在扩展方面显然变得效率低下。“我们需要向特定领域和应用程序相关的架构发展,大规模并行化可与我们人脑的工作方式相媲美。这意味着 CPU 将扮演更小的角色,有利于为特定工作负载定制电路,”IMEC 说。但他们也描述了部署在数据中心和边缘的人工智能和机器学习电路。

此外,IMEC还发现电阻率更低的新材料。IMEC曾展示了基于铝的二元化合物的实验研究,重点是它们的电阻率,理想配比状态的AlCu和Al2Cu薄膜,电阻率低至9.5μΩcm。这些结果在实验上支持了将AlCu和Al2Cu在先进的半镶嵌互连集成方案中用作新导体的可能性,在这些方案中它们可以与气隙结合以提高性能。然而,在这种组合中,焦耳热效应变得越来越重要。将逻辑技术线路图缩小到1nm及以下需要在后端最关键的层中引入新的导体材料。铝和钌(Ru)的电阻率低于铜、钴或钼等传统元素金属,这可能会对1nm工艺下的芯片性能有所影响。IMEC研究了包括AlNi、Al3Sc、AlCu和Al2Cu在内的铝化物薄膜的电阻率,在20nm及以上厚度时,所有PVD沉积薄膜都显示出与钼相当或低于钼的电阻率。28nm的AlCu和Al2Cu薄膜实现了9.5μΩcm的最低电阻率——该值低于Cu的值。实验还表明控制薄膜理想状态防止表面氧化是研究铝化物需要面临的挑战。

编辑:黄飞

-

2nm芯片是什么意思 2nm芯片什么时候量产2023-10-19 8115

-

日本半导体复兴 最快2025年搞定2nm工艺2022-11-08 2202

-

2nm芯片有什么用 2nm芯片里面有什么2022-06-27 2834

-

2nm芯片有多强 2nm芯片带来的突破2022-06-24 4358

-

ibm的2nm芯片究竟有多强 2nm芯片对续航的影响2022-06-23 3217

-

2nm芯片优势是什么 2nm芯片手机有哪些2022-06-22 4877

-

IMEC在大会中表示:2036年将迎来0.2nm工艺2022-05-23 2224

-

IBM宣布造出全球首颗2nm EUV芯片 精选资料分享2021-07-20 6183

-

牙膏踩爆!Intel 5nm工艺曝光:直逼IBM 2nm2021-07-15 2719

全部0条评论

快来发表一下你的评论吧 !