eSPI通讯总线的应用优势

电子说

描述

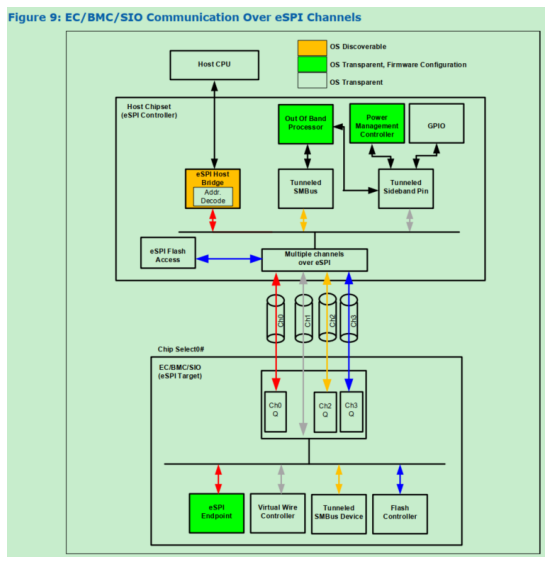

eSPI总线是Intel在2016年推出的一种通讯总线,用于x86 CPU平台和外设之间的通讯。支持eSPI接口的从设备,包括但不仅限于:

Embedded Controller(EC)

Baseboard Management Controller(BMC)

SuperI/O(SIO)

Port-80 Debug Card

eSPI总线的推出是为了替代LPC总线。《EC芯片专用总线》中对比了LPC总线和eSPI总线之间的差异。相较于LPC总线,eSPI总线节省物理引脚、功耗低、速度快、协议可扩展、支持一主多从,全面碾压 LPC 总线。

eSPI逻辑上设计了 Peripheral、Virtual Wire、OOB、Flash等4个数据通道。

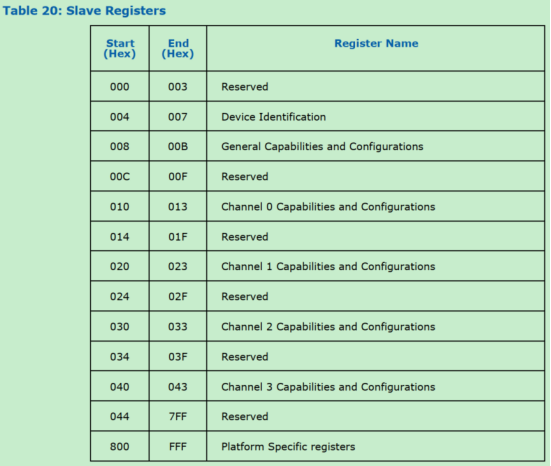

eSPI协议规定Slave端有5组寄存器,以描述eSPI SLave的通用配置和4个逻辑通道的配置。

01

Peripheral Channel

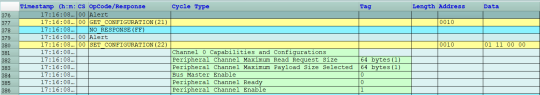

Peripheral Channel(逻辑外设通道)是为了兼容LPC总线通讯而设计,支持I/O、Memory访问。

为 KBC、ECI、UART、ShareMemory等Super-I/O 逻辑外设提供了访问基础。

Offset 10h: Channel 0 Capabilities and Configurations Register 通道 0 功能描述和配置寄存器。

写 offset 10h 寄存器,使能Peripheral Channel。

02

VirtualWire Channel

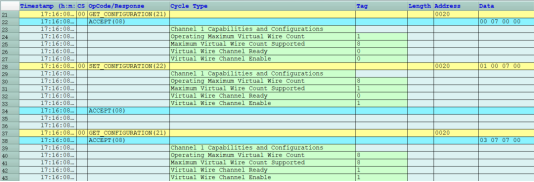

VirtualWire Channel(逻辑虚拟线通道)是为了取消x86平台的一些功能引脚,采用数据包的方式在Master和Slave直接传递引脚状态。

例如,SCI、SLP_S3/S4、PLTRST#、SERIRQ 等信号。

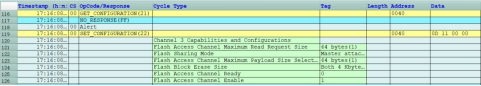

Offset 20h: Channel 1 Capabilities and Configurations Register 通道 1 功能描述和配置寄存器。

写 offset 20h 寄存器,使能Virtual Wire Channel。

03

OOB Channell

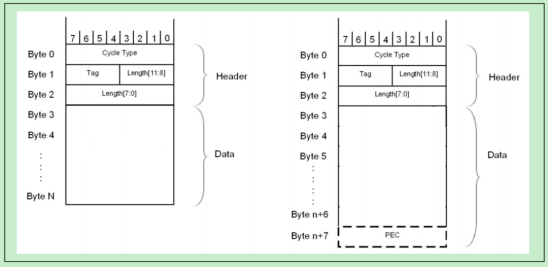

OOB Channel(逻辑带外通道)定义了一个通用的数据包格式。用于Master和Slave之间传递大宗数据。

在上述 Data 区域,按需设计不同编码的数据包,即可完成所需的功能。

SMBus over eSPI,将SMBus数据包在eSPI总线上传输。

MCTP over eSPI,将 MCTP 数据包在eSPI总线上传输。

PECI over eSPI,将 PECI 数据包在eSPI总线上传输。

Intel CrashLog over eSPI,利用eSPI总线抓取CPU、PCH异常log OOB 通道是eSPI 总线上最灵活的数据传输通道,未来还可以根据实际需要,开发出不同的功能。

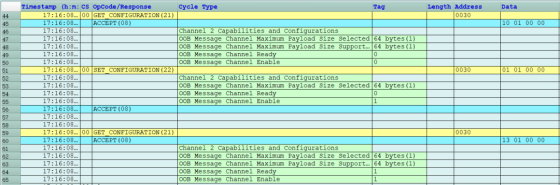

Offset 30h: Channel 2 Capabilities and Configurations Register 通道 2 功能描述和配置寄存器。

写 offset 30h 寄存器,使能OOB Message Channel。

04

Flash Channel

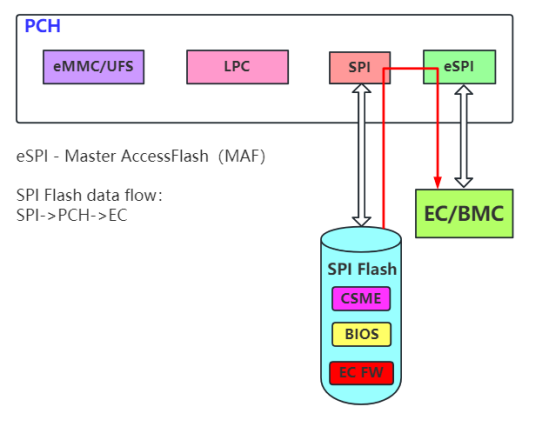

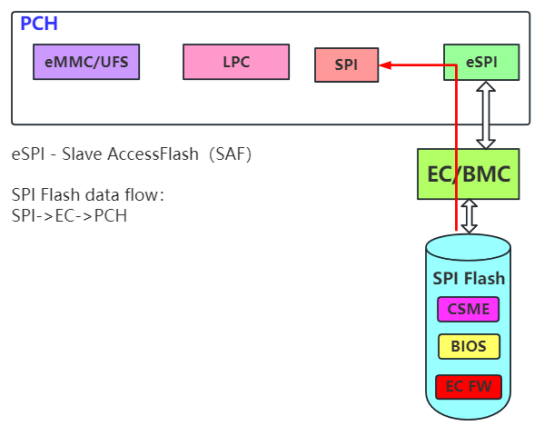

Flash Channel(逻辑存储通道)解决的是 eSPI-Master 和 eSPI-Slave 之间 SPI Flash 共享的问题,以减少设计 BOM。

以往,EC、BMC 等设备都需要一个 SPI Flash 存储固件,CPU 也需要一个 SPI Flash 存储 BIOS。

如果 EC 和 CPU 可以共享一个 SPI Flash,即可节省资源。

Master Attached Flash(MAF),SPI Flash 接 PCH,EC启动时透过 eSPI总线的 Flash通道,读取固件执行。

Slave Attached Flash(SAF),SPI Flash 接 EC,PCH 启动时透过 eSPI总线的 Flash通道,读取ME、BIOS 等固件。

Offset 40h: Channel 3 Capabilities and Configurations Register 通道 3 功能描述和配置寄存器。

写 offset 40h 寄存器,使能Flash Access Channel。

芯海EC的发展

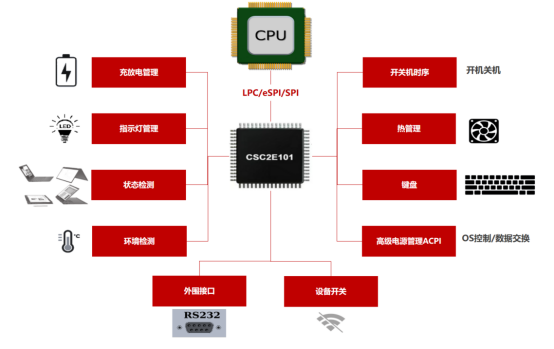

芯海科技CSC2E101支持LPC/eSPI双总线,是一款高集成、高安全、低功耗、易开发的嵌入式控制器(Embedded Controller),产品性能指标达到国际领先水平。

CSC2E101的APROM最大448KBye,为 EC应用设计提供了广阔的空间。应用设计上,CSC2E101完成了OOB 通道的SMBus、MCTP、PECI、CrashLog等数据包通讯验证,为客户二次开发提供了简便的接口。

审核编辑:刘清

-

智多晶eSPI_Slave IP介绍2025-05-08 1695

-

eSPI总线:Intel引领的通讯革新,赋能嵌入式控制器EC新发展2024-08-20 1971

-

最高效的通讯-CAN总线!一期带你彻底搞懂 #CAN总线 #汽车总线 #总线通讯 #通讯总线 #电路知识安泰小课堂 2024-07-02

-

eSPI协议抓包分析2023-11-18 6843

-

浅谈发展中的eSPI总线应用优势2023-02-22 3332

-

主流的通讯总线LPC 和 eSPI介绍2022-12-20 20957

-

R&S|二手ESPI3测试接收机回收、二手ESPI32022-01-07 479

-

tft_espi和nodemcu连接2021-10-25 834

-

SPI与eSPI分别是什么意思2021-09-23 3704

-

ESPI3 回收ESPI3 EMI测试接收机2021-08-28 1071

-

Microchip推出业界首款商用eSPI至LPC桥接器2019-05-30 5420

-

回收罗德施瓦茨ESPI3进口接收机ESPI32018-09-29 947

全部0条评论

快来发表一下你的评论吧 !