浅谈DDR内存技术原理1

电子说

描述

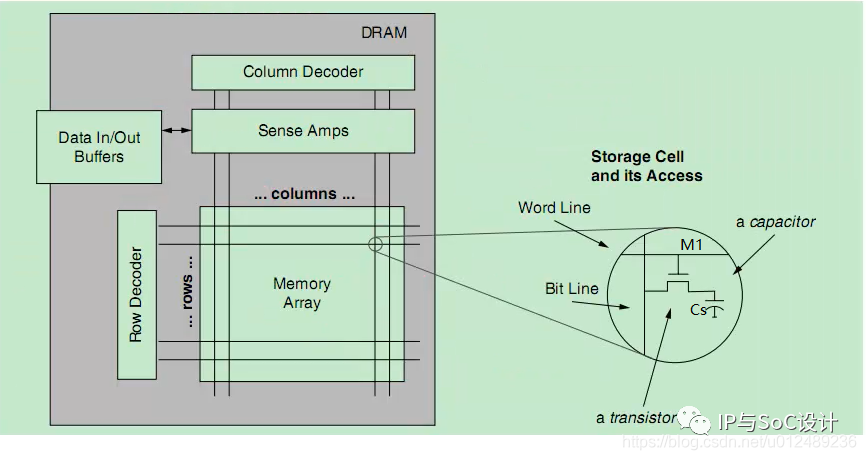

DRAM基本组成

对于DRAM,其主要由行和列组成,每一个bit中都是由类似右下图的类晶体管的结构组成,对于sdram的数据,可以通过控制column和row就可以访问sdram的随机地址的内容。

·读取某一个bit的状态,就是选中word line,那么图示中的晶体管M1就会导通,通过bit line的sense就可以感知到这个时候电容Cs上的状态,例如,现在如果这个bit的状态为1,那么导通之后就会从bit line上得到1,反之也是同样的道理。

·向某一bit写入1,首先通过row decoder选中word line,将会导致m1导通,那么bit line为1,会导致电容Cs充电,导致其电平为1,如果要写入,那么bit line的电平 为0,将会导致电容Cs放电,致使此时的电平为0。

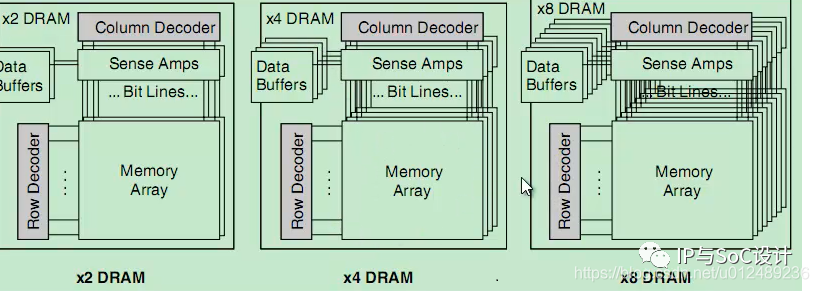

由上面可以看出一个位只能表示一个bit,那么我们想读取多个位的时候,该怎么办呢?那就出现了ddr中的bank的概念,由多个memory array就组成了一个bank,如下图,一次可以读取2bit/4bit/8bit的数据:

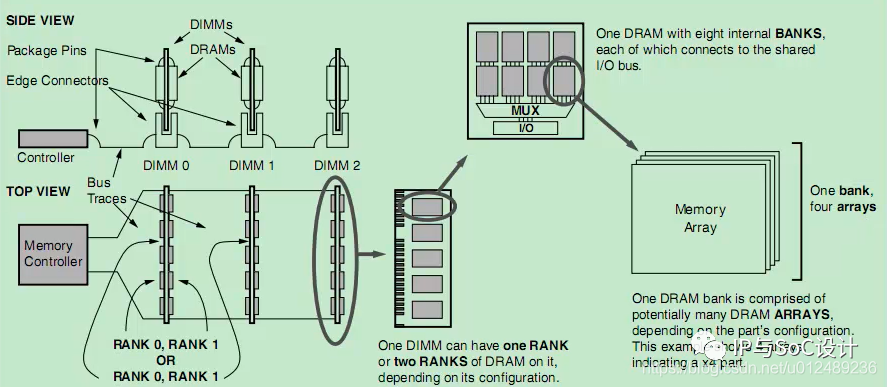

由多个bank就可以组成一个memory device,如下图,一个dram的芯片,由8个banks组成,而每个bank由4个memory array构成,而此时每个bank输出4个bit的I/O bus,那么为什么会出现bank的概念呢?动态内存区别于静态内存要定时刷新,每读取一个状态的时候,都需要重新充电。如果没有采用bank,假设我们现在要读取01-08地址的数据,当读取01的地址后,要等这个bank自刷新后才能读取02地址的值,而采用8个bank之后,没有这类问题,例如我们读取完01地址之后,那么读取02,因为02与01的控制方式不同,所以对于这段时间01可以后台的完成自刷新,依次类推,那么就可以很好的解决动态内存需要刷新的问题。

上图中,对于RANK、DIMM等在深入浅出DDR系列(1)——DDR原理篇中已经详细介绍了。

2

DDR工作原理

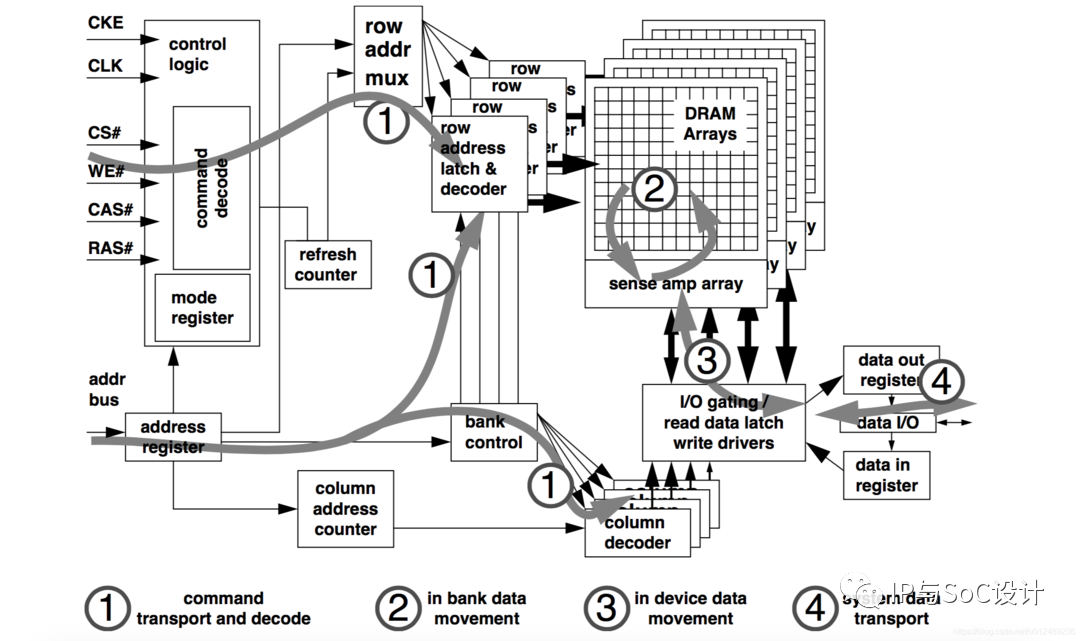

了解了DDR的基本组成后,我们来看看DDR如何来完成一次的读写过程。如下图所示,DRAM 的相关操作在内部大概可以分为以下的四个阶段:

·command transport and decode: 在这个阶段,Host 端会通过 Command Bus 和 Address Bus 将具体的 Command 以及相应参数传递给 DRAM。DRAM 接收并解析 Command,接着驱动内部模块进行相应的操作。其中会根据将addr bus上的数据解码成对应的row address和通过bank control解码后得到对应的bank,其次对应的column也会解码得到对应的地址

**·in bank data movement: **在这个阶段,第一阶段发送需要读取的 Column 的地址给 DRAM。然后 DRAM 再将 Active Command 所选中的 Row 中,DRAM 就将 Memory Array 中的数据从 DRAM Cells 中读出到 Sense Amplifiers,或者将数据从 Sense Amplifiers 写入到 DRAM Cells。

·in device data movement: 这个阶段中,数据将通过 IO 电路缓存到 Read Latchs 或者通过 IO 电路和 Write Drivers 更新到 Sense Amplifiers。

**·system data transport: **在这个阶段,进行读数据操作时,SDRAM 会将数据输出到数据总线上,进行写数据操作时,则是 Host 端的 Controller 将数据输出到总线上。

在上述的四个阶段中,每个阶段都会有一定的耗时,例如数据从 DRAM Cells 搬运到 Read Latchs 的操作需要一定的时间,因此在一个具体的操作需要按照一定时序进行。同时,由于内部的一些部件可能会被多个操作使用,例如读数据和写数据都需要用到部分 IO 电路,因此多个不同的操作通常不能同时进行,也需要遵守一定的时序。此外,某些操作会消耗很大的电流,为了满足 SDRAM 设计上的功耗指标,可能会限制某一些操作的执行频率。

3

DRAM基本命令

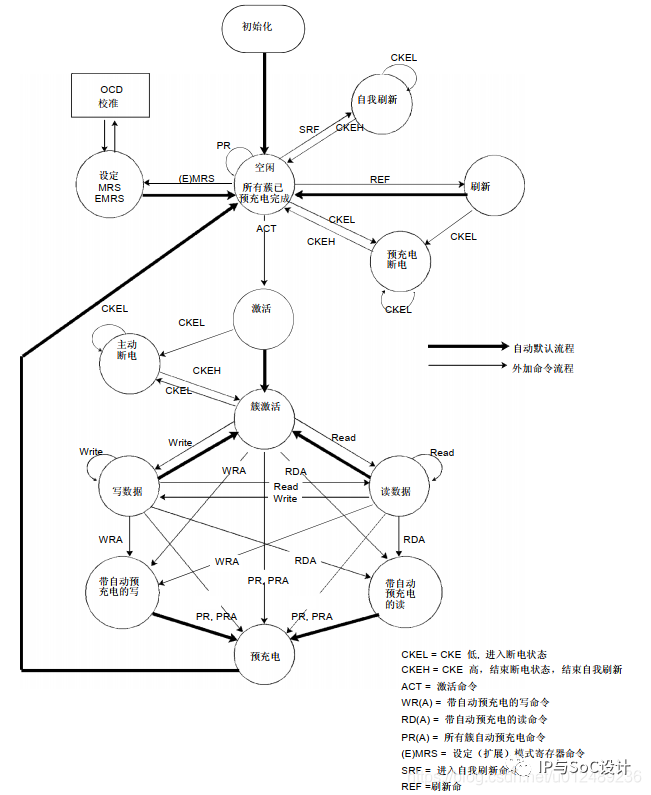

对于一款ddr,我们需要知道通过什么样的方式来控制完成我们需要,我们来看看ddr的状态,ddr的工作就是在这几个状态之间切换:

在芯片上电后,完成初始化后,dram处于idle阶段,上图是需要进入各个阶段的时候,应该需要进行那些基本的操作,对于ddr使用比较频繁的几个基本命令访问方式如下

·刷新模式: 储体中电容的数据有效是有时间限制的,所以为了保证数据的不丢失,所以要对ddr进行定时的刷新,SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行。该模式是由Host主动控制DRAM完成刷新,存储体中电容的数据有效保存期上限是64ms(毫秒,1/1000秒),也就是说每一行刷新的循环周期是64ms。

·自我刷新模式: 当系统进入低功耗模式,只需要发送一条 SRF指令,主要用于休眠模式低功耗状态下的数据保存,比较常见的应用是STR(Suspend to RAM,休眠挂起于内存)。就进入了该模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

·MRS模式(mode register set): 模式寄存器中的数据控制着 DDR2 SDRAM的操作模式.它控制着 CAS 延迟, 突发长度, 突发顺序, 测试模式, DLL复位, WR等各种选项,支持着 DDR2 SDRAM 的各种应用. 模式寄存器的默认值没有被定义, 所以上电之后必须按规定的时序规范来设定模式寄存器的值。

·EMRS 扩展模式寄存器: 存储着激活或禁止DLL的控制信息, 输出驱动强度, ODT 值的选择 和附加延迟等信息。

·预充电: 对一行读写操作后,关闭现有工作行,准备打开新行的操作就是预充电。

·读过程: 访问操作开始ACT一个激活命令,主要是激活bank和rol,就等于选通了某一Bank的某一行,接着发送一个read指令,就可以通过数据总线将数据送出去了,然后就进行预充电,恢复到读写的状态,预充电完成后,就恢复到idle状态。

·写过程: 与读过程基本类似。

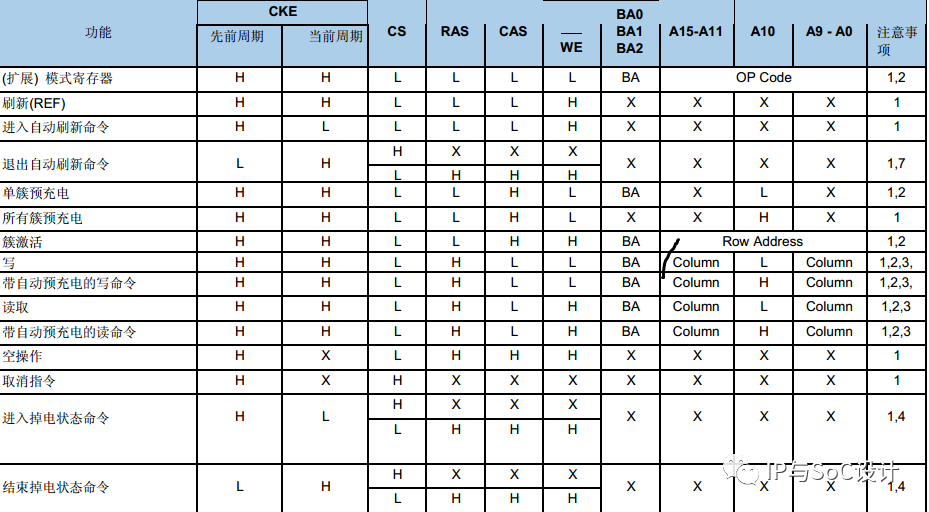

DRAM的基本命令是通过操作各种控制信号/地址信号的组合来完成,下表是DRAM的命令表:

-

DDR内存控制器的架构解析2025-03-05 4482

-

DDR内存与SDRAM的区别 DDR4内存与DDR3内存哪个好2024-11-29 5977

-

DDR5内存的工作原理详解 DDR5和DDR4的主要区别2024-11-22 9622

-

如何选择DDR内存条 DDR3与DDR4内存区别2024-11-20 13377

-

0706线下活动 I DDR4/DDR5内存技术高速信号专题设计技术交流活动2024-07-06 1259

-

DDR6和DDR5内存的区别有多大?怎么选择更好?2024-01-12 14648

-

DDR4和DDR3内存都有哪些区别?2023-10-30 15065

-

什么是DDR?DDR内存的演进之路2022-10-26 3917

-

三种主流内存技术(DDR、GDDR、LPDDR)的速度对比与应用和DDR5芯片的设计2017-11-15 48771

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32688

-

DDR内存条对比分析2011-12-29 4848

-

什么是DDR SDRAM内存2009-12-17 2243

全部0条评论

快来发表一下你的评论吧 !