如何解决高频信号传输领域存在的阻抗失配现象

描述

信号反射和衰减的程度取决于阻抗不连续的程度。 当失配阻抗幅度增加时,更大部分的信号会被反射,接收端观察到的信号衰减或劣化也就更多。

阻抗失配现象在交流耦合(又称隔直)电容的SMT焊盘、板到板连接器以及电缆到板连接器(如SMA)处经常会遇到。

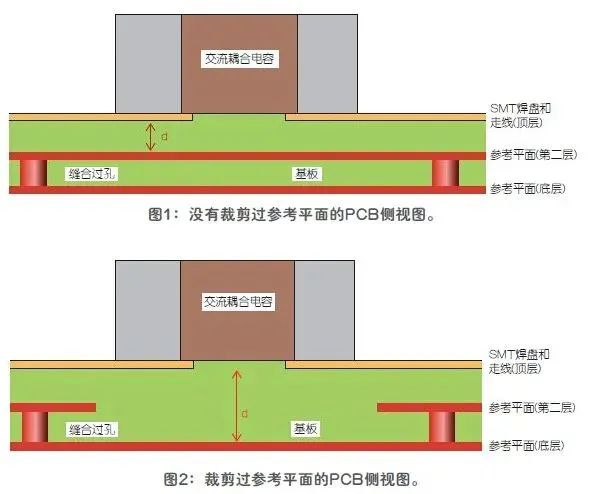

在如图1所示的交流耦合电容SMT焊盘的案例中,沿着具有100Ω差分阻抗和5mil铜箔宽度的PCB走线传播的信号,在到达具有更宽铜箔(如0603封装的30mil宽)的SMT焊盘时将遇到阻抗不连续性。 这种现象可以用式(1)和式(2)解释。

铜箔的横截面积或宽度的增加将增大条状电容,进而给传输通道的特征阻抗带来电容不连续性,即负的浪涌。

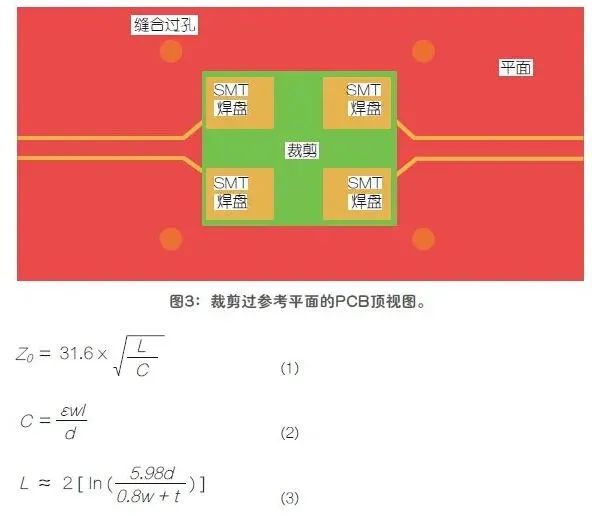

为了尽量减小电容的不连续性,需要裁剪掉位于SMT焊盘正下方的参考平面区域,并在内层创建铜填充,分别如图2和图3所示。

这样可以增加SMT焊盘与其参考平面或返回路径之间的距离,从而减小电容的不连续性。 同时应插入微型缝合过孔,用于在原始参考平面和内层新参考铜箔之间提供电气和物理连接,以建立正确的信号返回路径,避免EMI辐射问题。

但是,距离“d ”不应增加得太大,否则将使条状电感超过条状电容并引起电感不连续性。 式中:

条状电容(单位:pF);

条状电感(单位:nH);

特征阻抗(单位:Ω);

ε=介电常数;

焊盘宽度;

焊盘长度;

焊盘和下方参考平面之间的距离;

焊盘的厚度。

相同概念也可以应用于板到板(B2B)和电缆到板(C2B)连接器的SMT焊盘。

下面将通过TDR和插损分析完成上述概念的验证。 分析是通过在EMPro软件中建立SMT 焊盘3D 模型, 然后导入Keysight ADS中进行TDR和插损仿真完成的。

1、分析交流耦合电容的SMT焊盘效应

在EMPro中建立一个具有中等损耗基板的SMT的3D模型,其中一对微带差分走线长2英寸、宽5mil,采用单端模式,与其参考平面距离3.5mil,这对走线从30mil宽SMT焊盘的一端进入,并从另一端引出。

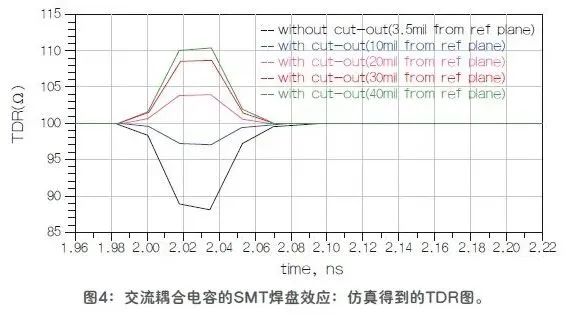

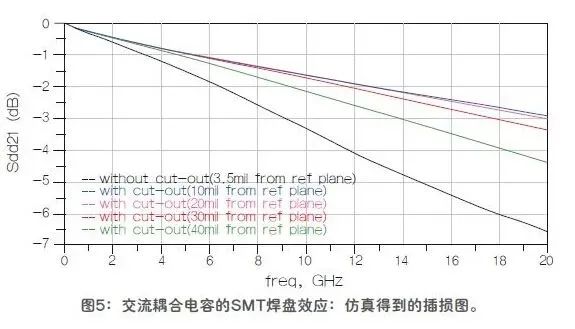

图4和图5分别显示了仿真得到的TDR和插损图。

参考平面没有裁剪的SMT设计造成的阻抗失配是12Ω,插损在20GHz时为-6.5dB。 一旦对SMT焊盘下方的参考平面区域进行了裁剪(其中“d ”设为10mil),失配阻抗就可以减小到2Ω,20GHz时的插损减小到-3dB。

进一步增加“d ”会导致条状电感超过电容,从而引起电感不连续性,转而使插损变差(即-4.5dB)。

2、分析B2B连接器的SMT焊盘效应

在EMPro中建立一个B2B连接器的SMT焊盘的3D模型,其中连接器引脚间距是20mil,引脚宽度是6mil,焊盘连接到一对长5英寸、宽5mil,采用单端模式的微带差分走线,走线距其参考平面3.5mil。

SMT焊盘的厚度是40mil,包括连接器引脚和焊锡在内的这个厚度几乎是微带PCB走线厚度的40倍。

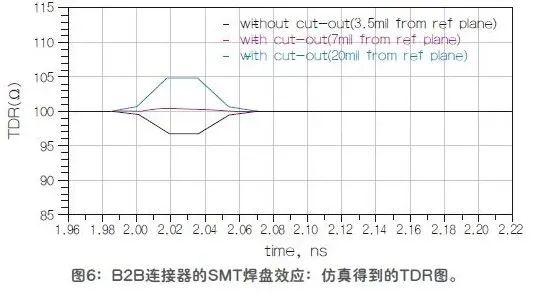

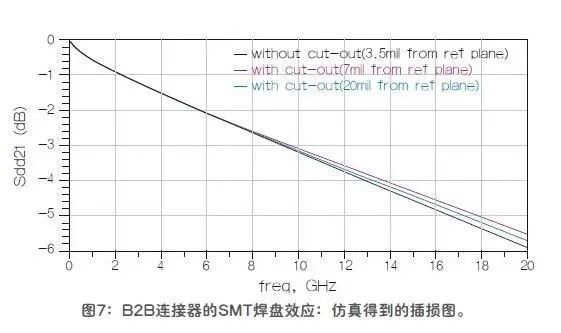

铜厚度的增加将导致电容的不连续性和更高的信号衰减。 这种现象可以分别由图6和图7所示的TDR和插损仿真图中看出来。

通过裁剪掉SMT焊盘正下方适当间距“d ”(即7mil)的铜区域,可以最大限度地减小阻抗失配。

3、小结

本文的分析证明,裁剪掉SMT焊盘正下方的参考平面区域可以减小阻抗失配,增加传输线的带宽。

SMT焊盘与内部参考铜箔之间的距离取决于SMT焊盘的宽度,以及包括连接器引脚和焊锡在内的SMT焊盘有效厚度。 在条件允许的情况下,PCB投产之前应先进行3D建模和仿真,确保构建的传输通道具有良好的信号完整性。

审核编辑:汤梓红

-

减小阻抗失配的SMT焊盘设计2018-09-17 2869

-

高频信号传输线传输高频的使用方式2019-05-24 3398

-

改进高频信号传输中的SMT焊盘设计解析2017-11-28 975

-

改进高频信号传输中的SMT焊盘阻抗失配的方法验证2018-01-05 7809

-

高频信号传输PCB板的SMT焊盘设计2019-09-17 1577

-

无线通信为什么要用高频信号 为什么高频信号容易传输2023-07-12 19018

-

噪声是高频信号还是低频信号?2023-09-19 5824

-

如何解决高频信号传输领域存在的阻抗失配现象?2023-10-20 2604

-

如何处理同轴阻抗失配?如何避免阻抗失配这种风险呢?2023-11-28 2213

-

既有高频信号又有低频信号如何解决阻抗问题?2023-12-07 1820

-

突破信号传输极限:高频阻抗PCB板2024-08-20 1386

-

高频信号中的阻抗特性 三相电系统中的阻抗分析2024-12-10 2807

-

SMA 插座:高频信号传输的 “高效桥梁”2025-03-26 982

-

三环电容ESL对高频信号完整性影响?2025-11-03 616

-

厚声电阻ESL对高频信号完整性影响?2026-04-15 44

全部0条评论

快来发表一下你的评论吧 !