分立式差动放大器与集成解决方案

模拟技术

描述

Jordyn Rombola and Chau Tran

经典的分立式差动放大器设计非常简单。运算放大器和四电阻网络有什么复杂之处?

但是,该电路的性能可能没有设计人员希望的那么好。本文基于实际生产设计,展示了分立电阻遇到的一些缺点,包括增益精度、增益漂移、交流共模抑制(CMR)和失调漂移。

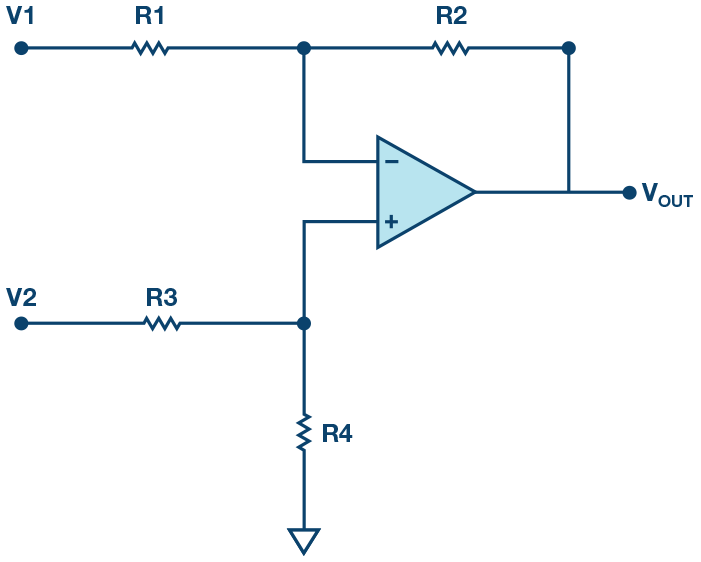

经典的四电阻差动放大器,如图1所示。

图1.经典的分立差动放大器。

该放大器的传递函数为:

当R1 = R3且R2 = R4时,公式1简化为

这种简化可以快速接近预期信号,但这些电阻永远不会完全相等。此外,电阻通常具有低精度和高温度系数,从而给电路带来重大误差。

例如,使用一个好的运算放大器和标准的1%100 ppm/°C增益设置电阻,初始增益误差可能高达2%,变化可能高达200 ppm/°C。 这个问题的一个解决方案是使用单片电阻网络进行精确的增益设置,但这些网络体积庞大且昂贵。除了精度低和温度漂移大之外,大多数分立式差分运算放大器电路的CMR较差,输入电压范围小于电源电压。此外,单芯片仪表放大器(仪表放大器)将具有增益漂移,因为前置放大器的内部电阻网络与进入RG引脚的外部增益设置电阻不匹配。

所有这些问题的最佳解决方案是使用带有内部增益设置电阻的差动放大器,例如AD8271。通常,这些产品由一个高精度、低失真运算放大器和几个经过调整的电阻组成。这些电阻可以连接以创建各种放大器配置,包括差分、同相和反相配置。芯片上的电阻可以并联连接,以获得更广泛的选择。与分立式设计相比,使用片内电阻器为设计人员提供了几个优势。

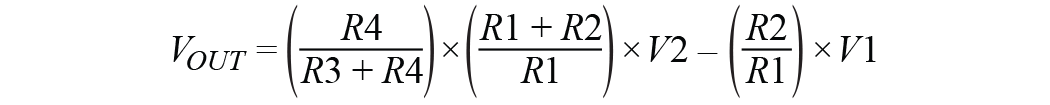

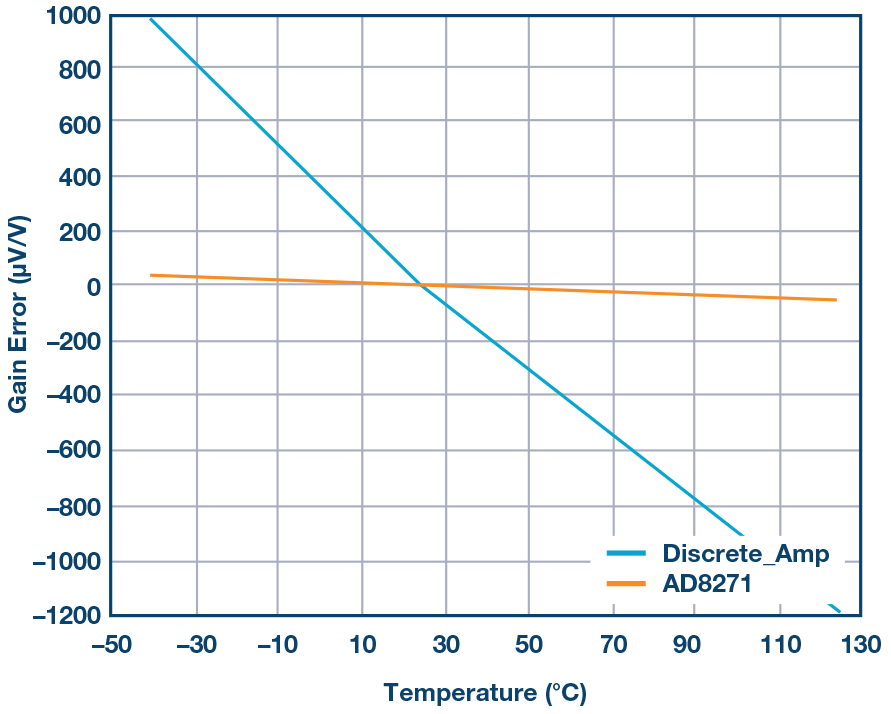

运算放大器电路的直流性能在很大程度上取决于周围电阻的精度。这些内部电阻的布局是紧密匹配的,并经过激光调整和匹配精度测试。因此,可以保证增益漂移、共模抑制和增益误差等规格的高精度。图1中的电路集成后,可提供0.1%的增益精度,增益漂移小于10 ppm/°C,如图2所示。

图2.增益误差与温度比较—AD8271与分立解决方案的关系

交流性能

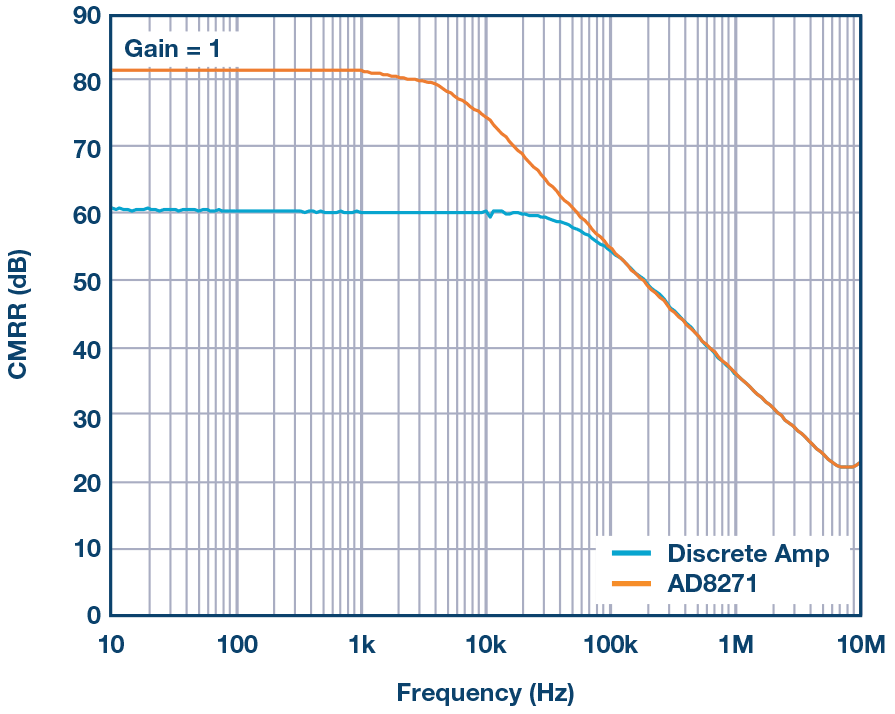

集成电路中的电路尺寸比印刷电路板(PCB)小得多,因此相应的寄生效应因子也较小,因此有助于交流性能。例如,运算放大器AD8271的正负输入端不是故意引脚排列的。由于不将这些节点连接到PCB上的走线,电容保持较低,从而提高了环路稳定性,并在整个频率范围内实现了共模抑制。有关性能比较,请参见图 3。

图3.CMRR与频率比较—AD8271与分立式解决方案CMRR的比较。

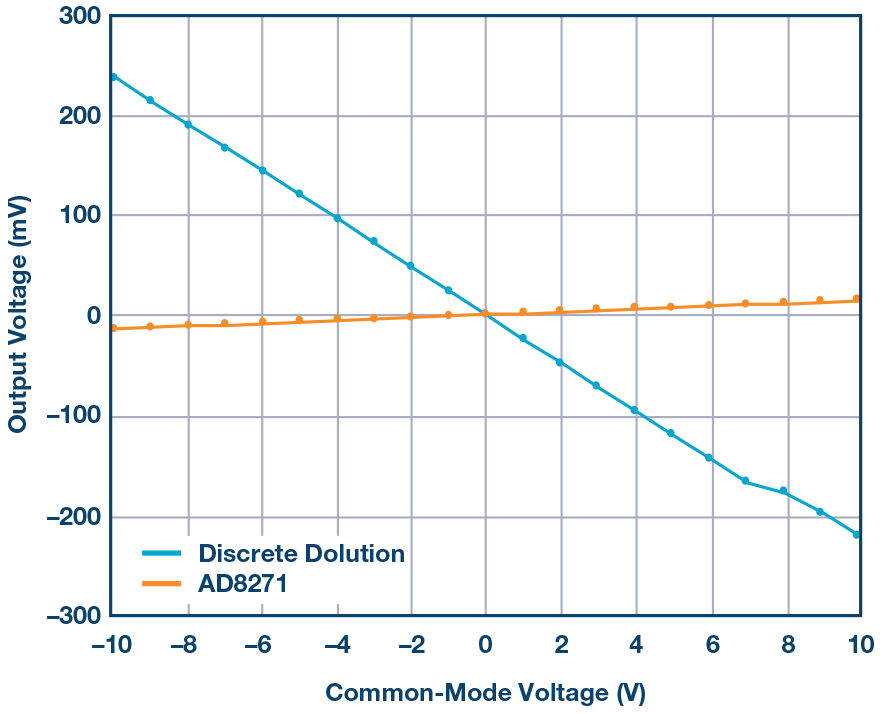

差动放大器的一个重要功能是抑制两个输入共有的信号。参考图1,如果电阻R1至R4不完全匹配(或者当增益大于1时R2、R3和R4、R1不匹配),部分共模电压将被差动放大器放大,出现在V处外作为 V1 和 V2 之间的有效差异,无法与真实信号区分开来。如果电阻不完美,部分共模电压将被差动放大器放大,并出现在V处外作为 V1 和 V2 之间的有效差异,无法与真实信号区分开来。差动放大器抑制这种能力称为共模抑制。这可以表示为共模抑制比(CMRR)或转换为分贝(dB)。采用分立解决方案时,电阻的匹配程度不如集成解决方案中的激光调整电阻,如图4中的输出电压与CMV的关系图所示。

图4.输出电压与共模电压的关系—AD8271与分立解决方案的关系

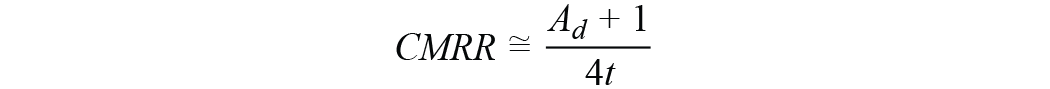

假设运算放大器为完美,CMRR为:

其中 Ad是差动放大器的增益,T是电阻容差。因此,在单位增益和1%电阻下,CMRR为50 V/V,或约34 dB;使用0.1%电阻时,CMRR增加到54 dB。即使给定具有无限共模抑制的完美运算放大器,整体CMRR也受到电阻匹配的限制。一些低成本运算放大器的最小CMRR在60 dB至70 dB范围内,使误差更加严重。

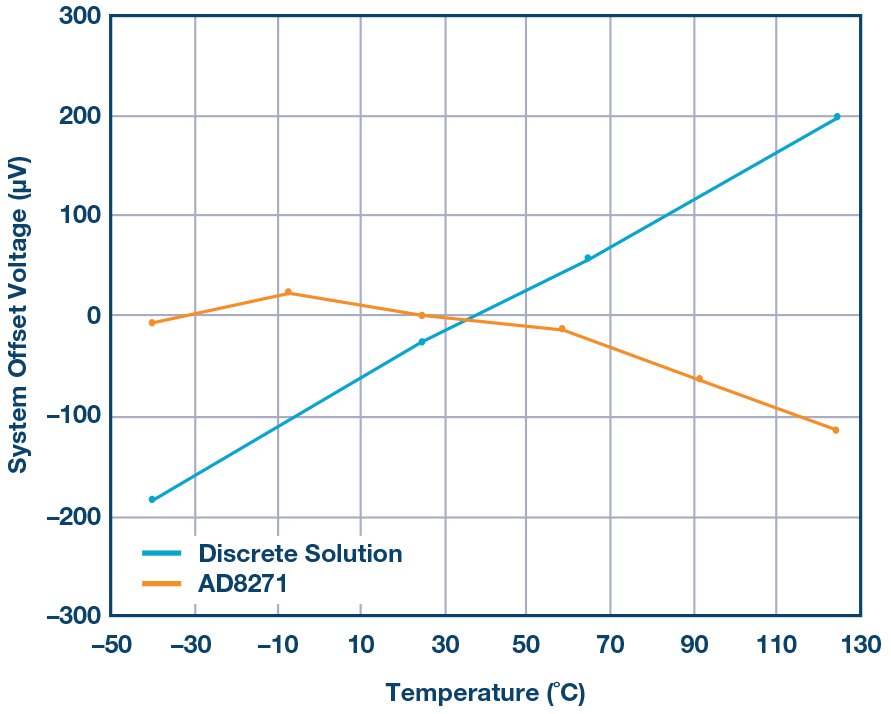

低容差电阻器

虽然放大器通常在规定的工作温度范围内表现良好,但必须考虑外部分立电阻的温度系数。对于带有集成电阻的放大器,可以对电阻进行漂移调整和匹配。布局通常使电阻靠近在一起,以便它们一起漂移,从而降低其失调温度系数。在分立情况下,电阻进一步分布在PCB周围,并且匹配得不如集成外壳,从而产生较差的失调温度系数,如图5所示。

图5.系统失调与温度的关系—AD8271与分立解决方案的关系

四电阻差动放大器(无论是分立式还是单片式)被广泛使用。只需将一个部件(而不是多个分立元件)放置在PCB上,就可以更快、更高效地构建电路板,并节省大量面积。

为了实现可靠、值得生产的设计,请仔细考虑噪声增益、输入电压范围和 80 dB 或更高的 CMR。这些电阻器也由相同的低漂移薄膜材料制成,因此它们在整个温度范围内的比率匹配非常出色。

结论

很容易看出具有内部增益设置电阻的放大器和分立式差动放大器之间的差异。

审核编辑:郭婷

-

分立式与集成式差分放大器的性能对比2026-01-26 8638

-

低成本LCD偏置电源分立式解决方案2018-11-19 3699

-

集成与分立式低电压电机驱动解决方案的主要差异2018-12-07 2741

-

想知道分立式3运算放大器仪表放大器是否需要任何补偿电容?2019-03-09 2148

-

利用分立式IC对功率放大器进行监测与控制的讨论2019-07-04 2538

-

基于双路差动放大器实现精密ADC驱动器设计2019-07-05 2567

-

深入了解差动放大器2019-10-27 2772

-

见招拆招,教你识破差动放大器缺点及优化措施2020-03-30 3326

-

内置增益设置电阻的放大器与分立差动放大器的区别2021-01-08 2027

-

基于多功能双路差动放大器AD8270的ADC驱动器2010-10-29 2052

-

建立FETching分立式放大器的一些提示2016-01-07 776

-

差动放大器应用2017-09-15 1314

-

分立差动放大器与集成解决方案2019-09-17 4768

-

建立FETching分立式放大器的提示2023-11-23 431

-

突破分立式电流感应放大器的最大共模范围2024-09-02 421

全部0条评论

快来发表一下你的评论吧 !