EDA探索之新型垂直互补场效应晶体管(CFET)结构设计

EDA/IC设计

描述

·EDA探索频道,今天迎来了特别内容——新型垂直互补场效应晶体管(CFET)结构设计与仿真研究,该论文已经发表在国际知名期刊上,获得了相关行业人员的极大关注,下面就跟着小编一起来开启今天的探索之旅吧~

集成电路密度的提升是一个业界持续追求的方向,也是“集成”的含义所在。提升集成电路器件密度有多种方式,其中降低器件的单位面积是最根本也是最有效的途径。自集成电路诞生以来,经历了平面器件(包括SOI器件),FinFET多栅器件到时下最先进的GAA(Gate All Around)纳米线器件(Intel称其为RibbonFET,三星称为Nanosheet)。单个器件的结构形式优化已经几乎推至极限。由于CMOS电路中,NOMS与PMOS往往是成对出现的,所以如何将一对CMOS的总体面积进行优化成为一个新的方向。可以有平面上的优化,如Forksheet,也可以将其垂直堆叠起来,称为CFET(Complementary Field Effect Transistor,CFET)。将NMOS与PMOS的GAA器件在垂直方向进行高密度三维单片集成,相较于现有主流FinFET与水平GAAFET,突破了CMOS在平面布局间距的尺寸限制,可以将减少SRAM单元面积40%以上,在代工厂等效3nm以下技术高密度、高性能集成电路制造中将成为有力的候选者。

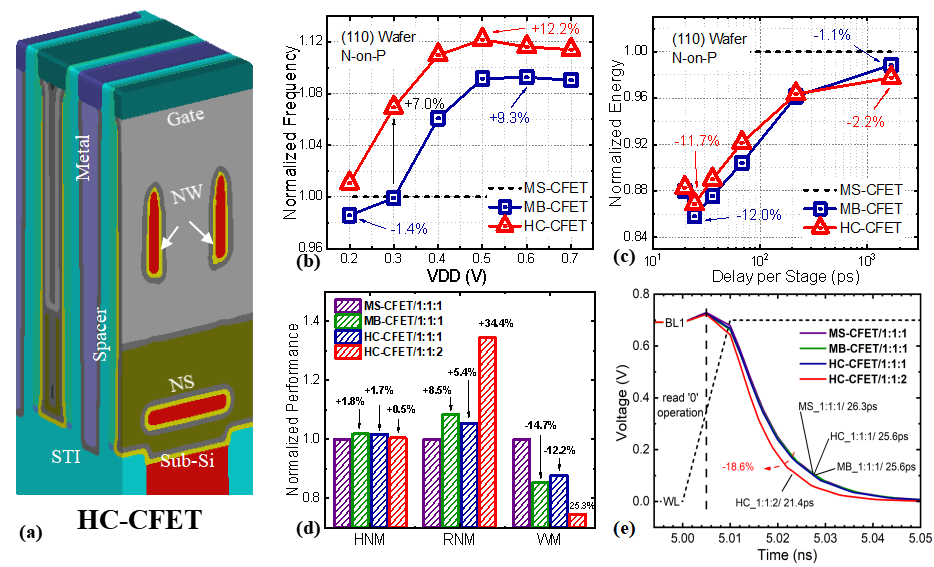

中国科学院微电子研究所殷华湘、吴振华研究团队利用DTCO(Design-Technology Co-optimization)方法系统性地研究了CFET的优势,提出了新型混合沟道CFET(Hybrid Channel Complementary FET,HC-CFET)结构设计和集成方案。该结构能够在单一衬底上,通过分步沟道形貌刻蚀,实现对NMOS和PMOS电子与空穴迁移率导电沟道的共同优化,即使NMOS具有(100)沟道表面晶向,PMOS具有(110)沟道表面晶向,从而在获得最佳的器件与电路性能的同时,可以在原来一个器件的面积使用下堆叠两个器件。器件结构设计与集成方案的可行性已通过EDA工具进行模拟仿真验证。通过系统性抽取全部寄生参数,对比了不同CFET架构下的RO(环振)和SRAM单元性能。结果表明,相较于常规垂直集成Fin和垂直集成纳米片的CFET结构(MS-CFET和MB-CFET),新型HC-CFET具有沟道晶向与空间布局优势,可以得到更高的工作频率以及更大的噪声容限窗口,展现出在超高度集成的CMOS集成电路应用上的巨大潜力。

该成果以“Investigation of Novel Hybrid Channel Complementary FET Scaling Beyond 3-nm Node From Device to Circuit”为题发表在国际知名期刊IEEE Transactions on Electron Devices上。中国科学院微电子研究所博士生罗彦娜为该文章第一作者;殷华湘研究员、吴振华研究员为该文共同通讯作者。鸿之微科技(上海)股份有限公司曹宇博士作为作者之一参与了此项工作。

原文链接:https://ieeexplore.ieee.org/document/9789149

(a) HC-CFET结构示意图,以及仿真对比的17级环形振荡器(b)归一化频率特性和(c)归一化能耗特性与6T-SRAM单元(d)归一化噪声容限特性和(e)读操作瞬态特性

编辑:黄飞

-

无结场效应晶体管详解2025-05-16 1630

-

互补场效应晶体管的结构和作用2025-01-24 5042

-

互补场效应晶体管点火和只用一个场效应晶体管点火与PWM的区别?2024-05-21 524

-

场效应晶体管的作用2023-05-16 3563

-

MOSFET和鳍式场效应晶体管的不同器件配置及其演变2023-02-24 13729

-

场效应晶体管的选用经验分享2021-05-13 1945

-

场效应晶体管的分类说明2020-09-18 10505

-

如何进行场效应晶体管的分类和使用2020-07-02 2093

-

场效应晶体管的分类及作用2019-05-08 4253

-

场效应晶体管在电路中的特别应用,你未必全都清楚2019-04-16 3502

-

MOS管与场效应晶体管背后的联系,看完后就全明白了2019-04-15 3305

-

结型场效应晶体管是什么?2010-03-04 4094

-

场效应晶体管的分类及使用2010-01-13 975

-

什么是场效应晶体管2009-05-24 7683

全部0条评论

快来发表一下你的评论吧 !