ADC的奇怪FFT结果

模拟技术

描述

David Buchanan

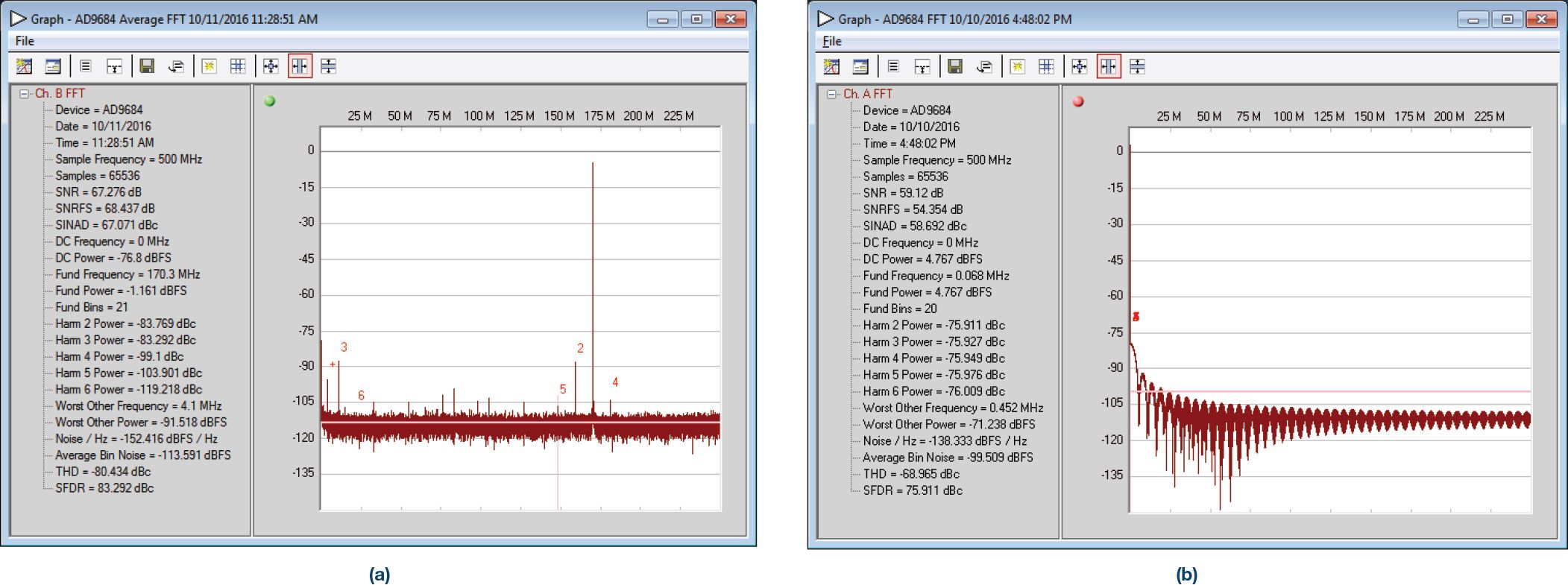

我最近收到了这个询问,我能够很快解决它。下面的FFT结果说明了设计人员的问题:

图1.AD9684 ADC采样电流(500 MSPS、170.3 MHz A)的良好和不良FFT结果在在 –1 分贝时。

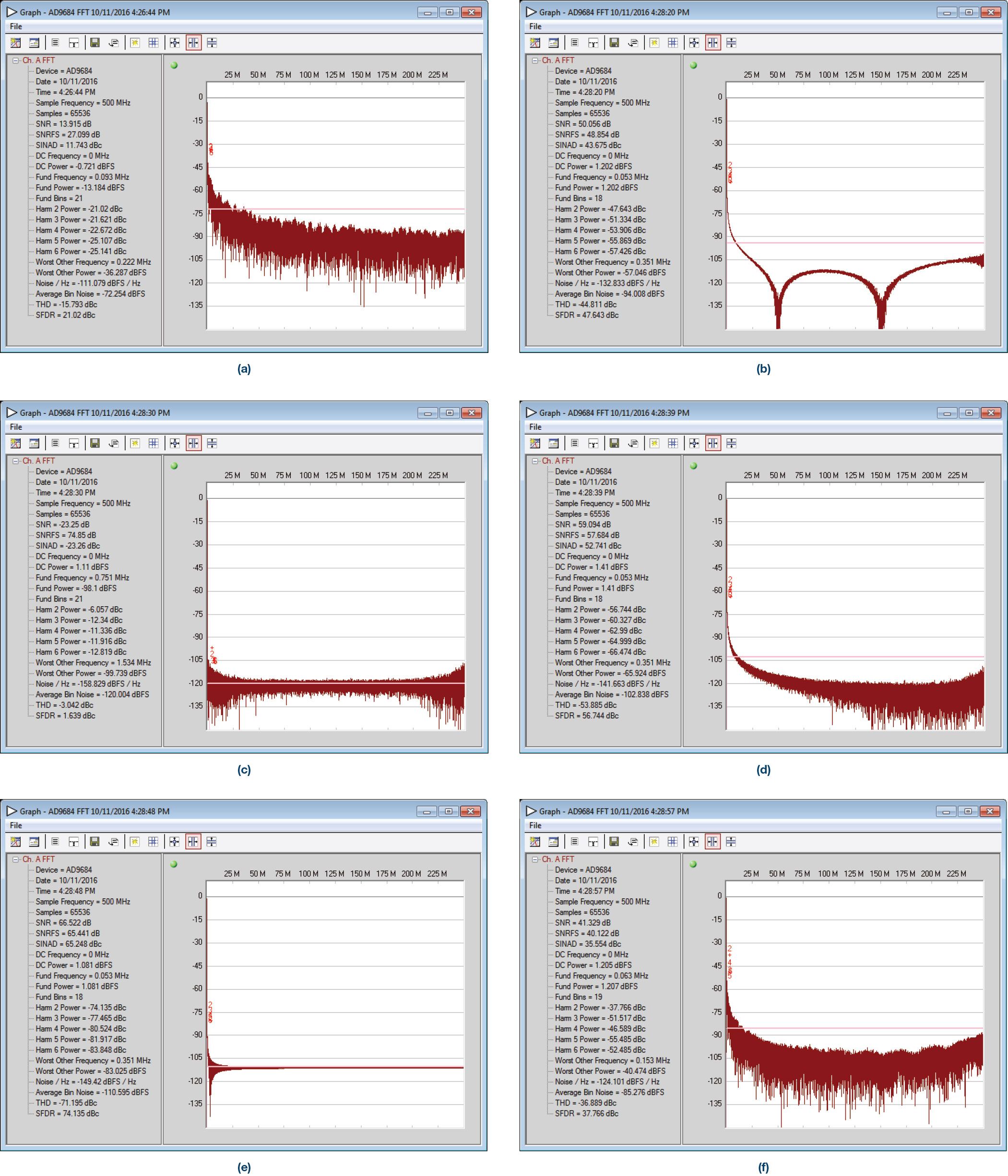

客户报告说,FFT结果不仅看起来很疯狂,而且不一致。这种行为也与我最初对正在发生的事情的猜测一致:时钟源关闭或未连接,转换器的输入采样时钟接收器自行振荡。如果连接时钟的电缆是间歇性的或信号路径中的某个组件是片状的,也会发生这种情况。正如我所说,这个问题并没有花太长时间来解决,因为我已经多次看到类似的结果。图 2 显示了在此操作条件下您可能会看到的其他一些 FFT:

图2.不稳定时钟振荡的FFT结果示例。

在几乎所有应用中,您都希望采样时钟输入为单个频率。当您查看频域时,由于相位或热噪声、频率不稳定或不需要的频率成分而导致的任何变化都会导致采样时钟和模拟输入信号之间的预期关系中断。参见应用笔记AN-756,了解时钟上的细微相位噪声或调制如何在采样时使输入信号失真。

在这种情况下,罪魁祸首是什么?高速ADC的采样时钟输入通常是共享相同共模偏置的差分输入,接收器具有非常高的增益。因此,在没有施加差分信号的情况下,输入在相同的电压下偏置,任何非共模噪声都可能导致采样时钟接收器振荡。在这种情况下,振荡将不是一个纯频率(如果是,它可能是一个很好的功能)。相反,频率将随机变化。由于采样时钟频率随机变化,模拟输入的能量将分布在频域的奈奎斯特带宽上。

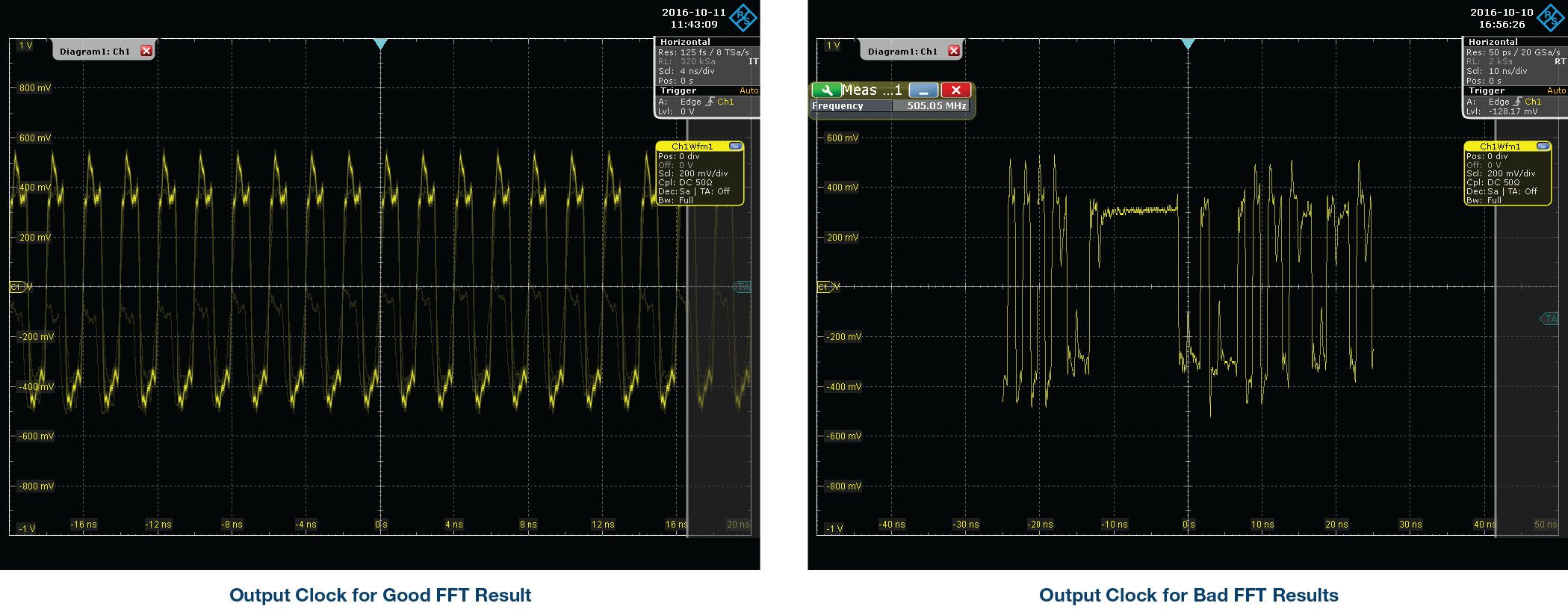

在大多数情况下,您只需要识别这一点并恢复预期的时钟参考以继续测试。但是,如果要验证这是问题所在,请观察ADC的数据时钟输出(DCO)(注意,这不适用于JESD204B输出)。这通常是ADC采样时钟的延迟副本,或者采样时钟的分频版本(如果您采用任何会降低数据速率的数字特性)。对于图1中的好和坏FFT,数据时钟输出如图3所示:

图3.用于图1所示两种FFT情况的ADC数据时钟输出。

如您所见,该周期与我们预期的一样变化。我当然理解为什么你在第一次遇到(甚至第一次)时不会意识到这一点。从表面上看,测试台似乎在运行,但结果突然令人困惑。ADC 是否损坏?数据捕获是否混乱?软件是否已损坏?不,只是缺少信号源。

-

使用ADC FFT数据进行输入阻抗测量2024-10-18 662

-

当输入振幅较大时,SPU FFT结果似乎无效,为什么?2024-05-28 384

-

为什么adc结果出现断层现象2023-08-08 2070

-

Raspberry Pi Pico上的ADC采样和FFT2023-06-16 2773

-

FFT变换结果的物理意义是什么?2021-11-19 2118

-

FFT变换结果的物理意义2021-08-17 1465

-

ADC测试出现奇怪的FFT结果2019-12-06 7002

-

快速傅里叶变换(FFT)结果的物理意义分析2017-11-09 3305

-

第25章 FFT变换结果的物理意义2016-09-27 3470

-

为什么LabVIEW的fft.vi和MATLAB的fft函数计算出来的结果不同?2014-10-31 6105

-

快速傅里叶变换FFT结果的物理意义2012-10-24 2864

-

ADC输出转换采样生成FFT图详解2010-12-11 8725

-

存储深度对FFT结果的影响2009-08-25 1192

-

利用FFT IP Core实现FFT算法2008-01-16 8497

全部0条评论

快来发表一下你的评论吧 !