浅谈STM32 模数转换器 (ADC)(上)

模拟技术

描述

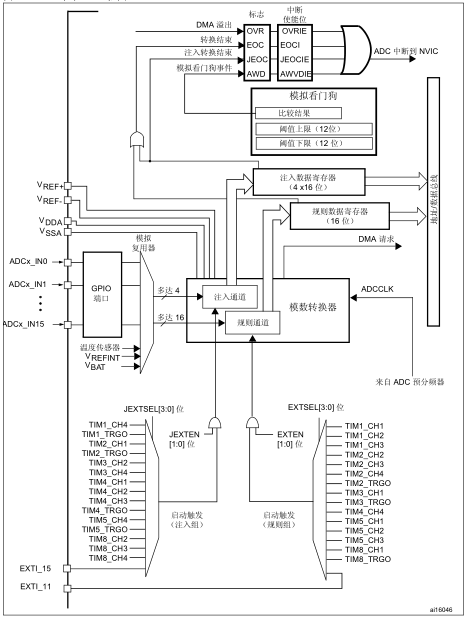

STM32F4xx系列提供的12位ADC是逐次逼近型模数转换器。它具有多达 19 个复用通道,可测量来自 16 个外部源、两个内部源和 V BAT 通道的信号。这些通道的 A/D 转换可在单次、连续、扫描或不连续采样模式下进行。ADC 的结果存储在一个左对齐或右对齐的 16 位数据寄存器中。

ADC 具有模拟看门狗特性,允许应用检测输入电压是否超过了用户自定义的阈值上限或下限。

单个ADC框图

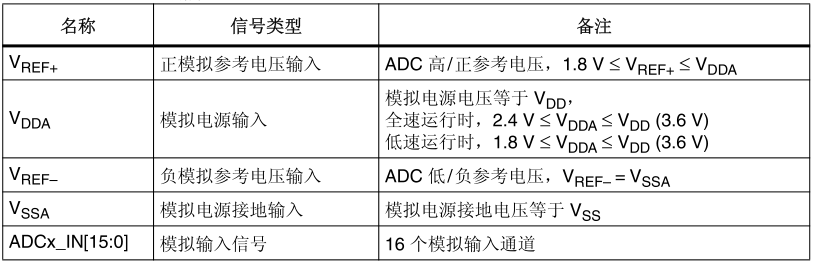

ADC 引脚

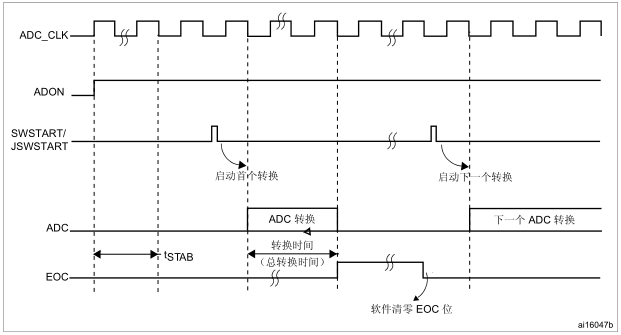

ADC开关控制

可通过将ADC_CR2寄存器中的 ADON 位置1来为 ADC 供电。首次将 ADON 位置1时,会将ADC从掉电模式中唤醒。

SWSTART 或 JSWSTART 位置 1 时,启动 AD 转换。

可通过将 ADON 位清零来停止转换并使 ADC 进入掉电模式。在此模式式下,ADC 几乎不耗电(只有几 μA)。

ADC时钟

ADC 具有两个时钟方案:

● 用于模拟电路的时钟:ADCCLK,所有 ADC 共用

此时钟来自于经可编程预分频器分频的 APB2 时钟,该预分频器允许 ADC 在 f PCLK2 /2、/4、/6 或 /8 下工作。有关 ADCCLK 的最大值,请参见数据手册。

● 用于数字接口的时钟(用于寄存器读/写访问)

此时钟等效于 APB2 时钟。可以通过 RCC APB2 外设时钟使能寄存器 (RCC_APB2ENR)分别为每个 ADC 使能/禁止数字接口时钟。

通道选择

有 16 条复用通道。可以将转换分为两组:规则转换和注入转换。每个组包含一个转换序列,该序列可按任意顺序在任意通道上完成。例如,可按以下顺序对序列进行转换:ADC_IN3、ADC_IN8、ADC_IN2、ADC_IN2、ADC_IN0、ADC_IN2、ADC_IN2、ADC_IN15。

● 一个规则转换组最多由 16 个转换构成。必须在 ADC_SQRx 寄存器中选择转换序列的规则通道及其顺序。规则转换组中的转换总数必须写入 ADC_SQR1 寄存器中的 L[3:0] 位。

● 一个注入转换组最多由 4 个转换构成。必须在 ADC_JSQR 寄存器中选择转换序列的注入通道及其顺序。注入转换组中的转换总数必须写入 ADC_JSQR 寄存器中的 L[1:0] 位。

如果在转换期间修改 ADC_SQRx 或 ADC_JSQR 寄存器,将复位当前转换并向 ADC 发送一个新的启动脉冲,以转换新选择的组。

温度传感器、V REFINT 和 V BAT 内部通道

● 对于 STM32F40x 和 STM32F41x 器件,温度传感器内部连接到通道 ADC1_IN16。

内部参考电压 VREFINT 连接到 ADC1_IN17。

● 对于 STM23F42x 和 STM32F43x 器件,温度传感器内部连接到与 VBAT 共用的通道

ADC1_IN18。一次只能选择一个转换(温度传感器或 VBAT)。同时设置了温度传感器和 VBAT 转换时,将只进行 VBAT 转换。

内部参考电压 VREFINT 连接到 ADC1_IN17。

VBAT通道连接到通道ADC1_IN18。该通道也可转换为注入通道或规则通道。

单次转换模式

在单次转换模式下, ADC 执行一次转换 。CONT 位为 0 时,可通过以下方式启动此模式:

● 将 ADC_CR2 寄存器中的 SWSTART 位置 1(仅适用于规则通道)

● 将 JSWSTART 位置 1(适用于注入通道)

● 外部触发(适用于规则通道或注入通道)

完成所选通道的转换之后:

● 如果转换了规则通道:

— 转换数据存储在 16 位 ADC_DR 寄存器中

— EOC(转换结束)标志置 1

— EOCIE 位置 1 时将产生中断

● 如果转换了注入通道:

— 转换数据存储在 16 位 ADC_JDR1 寄存器中

— JEOC(注入转换结束)标志置 1

— JEOCIE 位置 1 时将产生中断

然后,ADC 停止。

连续转换模式

在连续转换模式下, ADC 结束一个转换后立即启动一个新的转换 。CONT 位为 1 时,可通过外部触发或将 ADC_CR2 寄存器中的 SWSTRT 位置 1 来启动此模式(仅适用于规则通道)。

每次转换之后:

● 如果转换了规则通道组:

— 上次转换的数据存储在 16 位 ADC_DR 寄存器中

— EOC(转换结束)标志置 1

— EOCIE 位置 1 时将产生中断

时序图

ADC 在开始精确转换之前需要一段稳定时间 t STAB 。ADC 开始转换并经过 15 个时钟周期后,EOC 标志置 1,转换结果存放在 16 位 ADC 数据寄存器中。

扫描模式

此模式用于扫描一组模拟通道。

通过将 ADC_CR1 寄存器中的 SCAN 位置 1 来选择扫描模式。将此位置 1 后,ADC 会扫描在 ADC_SQRx 寄存器(对于规则通道)或 ADC_JSQR 寄存器(对于注入通道)中选择的所有通道。为组中的每个通道都执行一次转换。每次转换结束后,会自动转换该组中的下一个通道。如果将 CONT 位置 1,规则通道转换不会在组中最后一个所选通道处停止,而是再次从第一个所选通道继续转换。

如果将 DMA 位置 1,则在每次规则通道转换之后,均使用直接存储器访问 (DMA) 控制器将转换自规则通道组的数据(存储在 ADC_DR 寄存器中)传输到 SRAM。在以下情况下,ADC_SR 寄存器中的 EOC 位置 1:

● 如果 EOCS 位清零,在每个规则组序列转换结束时

● 如果 EOCS 位置 1,在每个规则通道转换结束时

从注入通道转换的数据始终存储在 ADC_JDRx 寄存器中。

数据对齐

由于STM32的ADC是12位的,结果存储在16位的数据寄存器中,有4位用不到,所以ADC存在左对齐或右对齐的方式。为方便读数,一般都选择右对齐。

可独立设置各通道采样时间

ADC 会在数个 ADCCLK 周期内对输入电压进行采样,可使用 ADC_SMPR1 和 ADC_SMPR2寄存器中的 SMP[2:0] 位修改周期数。每个通道均可以使用不同的采样时间进行采样。

总转换时间的计算公式如下:

T conv = 采样时间 + 12 个周期

快速转换模式

可通过降低 ADC 分辨率来执行快速转换。RES 位用于选择数据寄存器中可用的位数。每种分辨率的最小转换时间如下:

● 12 位:3 + 12 = 15 ADCCLK 周期

● 10 位:3 + 10 = 13 ADCCLK 周期

● 8 位:3 + 8 = 11 ADCCLK 周期

● 6 位:3 + 6 = 9 ADCCLK 周期

-

浅谈CW32系列模数转换器(ADC)2023-10-25 2886

-

STM32模数转换器 (ADC)介绍2023-07-22 5381

-

浅谈STM32 模数转换器 (ADC)(下)2023-02-17 1210

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1817

-

模数转换器ADC简介2022-02-17 1800

-

STM32的ADC模数转换器有哪几种工作模式及应用呢2021-11-15 5856

-

STM32之ADC模数转换器介绍2021-11-08 3287

-

如何正确的使用STM32H7上的ADC模数转换器2021-09-27 9757

-

介绍STM32的模数转换器(ADC)2021-08-24 1292

-

ADC模数转换器2021-08-06 2074

-

模数转换器(ADC)的配置有哪些流程?2021-07-14 3147

-

5962-9581501HXA高端AD模数转换器2020-07-15 2199

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3657

-

数模和模数转换器2009-09-16 7942

全部0条评论

快来发表一下你的评论吧 !