场效应管电路设计基础知识

模拟技术

描述

FET广泛用于分立式和IC电路,提供电压增益和高输入阻抗。

场效应晶体管用于电路设计,因为它们能够提供非常高的输入阻抗水平以及显着的电压增益水平。

与作为电流控制器件的双极晶体管不同,场效应晶体管是电压控制的。这使得FET电路的设计方式与双极晶体管电路的设计方式大不相同。

但是,仍然可以设计具有电流和电压增益的电路,并采用类似的电路格式。

场效应管电路基础知识

在考虑使用FET电路时,有必要考虑FET技术,场效应晶体管的类型将是最适用的。

关于场效应晶体管技术的说明:

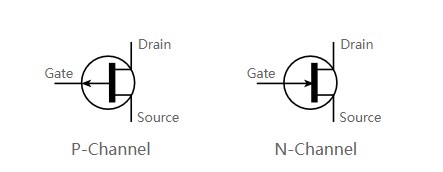

场效应晶体管FET是一种提供电压增益的三端器件。具有高输入阻抗的输入端子附近的电场称为栅极,可改变在称为源极和漏极的端子之间的通道中流动的电流。

场效应管有三个电极:

源:源极是FET上的电极,多数载流子通过该电极进入通道,即充当器件载流子的源。通过源进入通道的电流由IS指定。

排水:漏极是多数载流子离开通道的FET电极,即它们从通道中排出。通过漏极进入通道的常规电流由字母ID表示。此外,漏源电压通常由字母VDS表示

门:栅极是控制通道电导率的端子,因此栅极上的电压水平控制着在设备输出中流动的电流。

结 FET 电路符号

场效应管电路设计参数

在开始设计FET电路时,有必要确定电路的基本要求。这些将管理有关要使用的电路拓扑类型以及要使用的FET类型的许多决策。

晶体管电路设计的要求中可能需要许多参数:

电压增益:电压增益通常是一个关键要求。它是输出信号电压除以输入信号电压。

电流增益:这是FET电路的电流增益。可能需要向负载驱动高电流。

输入阻抗:这是前一级在向相关FET电路提供信号时将看到的阻抗。FET固有地具有高栅极输入阻抗,因此FET通常用于这一点至关重要的地方。

输出阻抗:输出阻抗也很重要。如果FET电路驱动低阻抗电路,则其输出必须具有低阻抗,否则晶体管输出级将出现较大的压降。

频率响应:频率响应是影响FET电路设计的另一个重要因素。低频或音频晶体管电路设计可能与RF应用中使用的电路设计不同。此外,电路设计中FET和电容值的选择也会受到所需频率响应的极大影响。

电源电压和电流: 在许多电路中,电源电压由可用的电压决定。此外,电流可能会受到限制,特别是如果完成的FET电路设计由电池供电。

用于电路设计的 FET 类型

由于可以使用几种不同类型的场效应晶体管,因此有必要至少定义一些可以在电路设计过程中使用的FET。

下表定义了可能遇到的一些不同类型和特征。

| 用于电路设计的场效应晶体管 | |

|---|---|

| 特征 | 详 |

| N 通道 | N 沟道 FET 具有由 N 型半导体制成的通道,其中大多数载流子是电子。 |

| P 通道 | P 沟道 FET 具有由 P 型半导体制成的通道,其中大多数载流子是空穴。 |

| J-场效应管 | J-FET 或结 FET 是 FET 的一种形式,其中栅极通过使用二极管结到通道上形成。通过确保二极管结在电路内工作时保持反向偏置来保持隔离。FET电路设计的一个关键要求是确保结保持反向偏置,以实现令人满意的操作。 |

| 场效应管 | 这种类型的场效应晶体管依赖于栅极和沟道之间的金属氧化物。它提供非常高的输入电阻。 |

| 双栅极场效应管 | 顾名思义,这种形式的MOSFET有两个栅极。在FET电路设计中,这提供了额外的选择。 |

| 增强模式 | 增强模式FET在零栅源电压下关断。它们通过沿漏极电压方向(即朝向电源轨)拉动栅极电压来导通,N沟道器件为正,P沟道器件为负。换句话说,通过将栅极电压拉近漏极电压,通道有源层中的载流子数量得到增强。 |

| 耗尽模式 | 在耗尽模式 MOSFET 中,该器件通常在零栅极-源极电压下导通。漏极电压方向上的任何栅极电压都会消耗载波通道的有效面积并减少电流流动。 |

在设计FET电路时,首先需要选择所需的FET类型。在进行电路设计之前,需要确定包括FET的基本类型在内的FET的基本类型(包括结FET还是MOSFET)或其他类型以及模式类型和其他因素。

-

MOS场效应管的基础知识2023-08-17 2514

-

场效应管的基础知识2022-09-20 8020

-

51单片机场效应管的基础知识详细说明2019-08-23 1431

-

场效应管知识点总结!2019-08-12 3370

-

场效应管必须知道的基础知识!2016-06-08 1162

-

场效应管2016-05-13 1096

-

场效应管放大电路2015-12-31 2005

-

场效应管电子基础教程2010-04-14 1601

-

VMOS场效应管,VMOS场效应管是什么意思2010-03-04 1796

-

场效应管的基础知识22009-11-09 1769

-

场效应管基础知识2008-08-12 952

-

场效应管知识 什么叫场效应管 场效应管工作原理2008-01-15 17460

全部0条评论

快来发表一下你的评论吧 !