串行器和解串器对的性能测试:MAX9247和MAX9218

描述

高速串行数据连接已广泛应用于网络、服务器和3G基站的视频显示、数码相机传感和背板数据传输。Maxim开发了用于串行链路发射器和接收器的产品。本应用笔记演示了典型串行器和解串器(SerDes)对(MAX9247和解串器)在各种电缆类型、电缆长度和数据速率条件下的性能。生成的信息对于需要高速序列化数据连接的应用程序非常有用。

介绍

Maxim的高速串行器和解串器(SerDes)产品已用于汽车、网络、服务器和3G基站的视频、图像和数据传输。MAX9247串行器和MAX9218解串器构成一对典型的单LVDS链路,内置时钟。该对可以达到的最高串行链路数据速率高达800Mbps。

本应用笔记演示了该数据收发器链路的性能,基于不同的电缆类型、电缆长度和数据速率。本文还展示了Maxim专有的预加重功能和线路均衡器带来的性能改进。为了满足汽车应用中的恶劣环境,该SerDes对还在-40°C至+105°C的温度范围内进行了测试。

测试设置

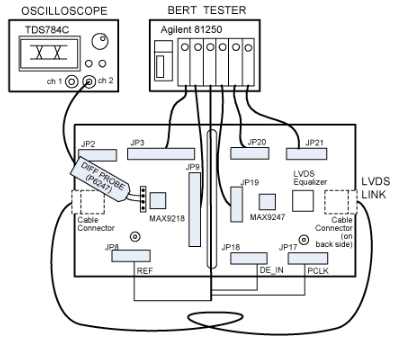

测试装置包括安捷伦ParBERT 81250测试仪、TDS784C 1GHz数字示波器、TEK P6247差分探头和MAX9217/MAX9218评估板。安捷伦 81250 是一款并行误码率测试 (BERT)。组件的连接如下图所示(图1)。

图1.MAX9247和MAX9218的性能测试设置

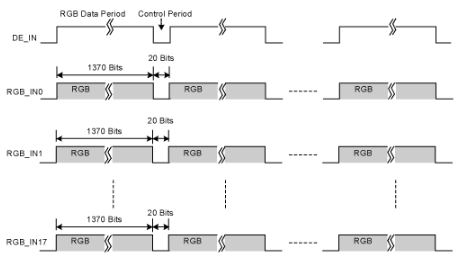

MAX9247具有27位并行数据输入,其中18位用于RGB视频数据输入,9位用于控制数据输入。LVDS串行链路的数据速率是并行数据速率的20倍,包括2个开销位。安捷伦 9 的前 81250 个输出通道连接到前 9 个 RGB 输入(RGB_IN0 至 RGB_IN8)。前 9 个通道的反相输出连接到其余 9 个 RGB 输入(RGB_IN9 至 RGB_IN17)。BERT仅在RGB数据上实现。每个ParBERT输出通道上的数据序列是独立生成的伪随机比特流,非重复长度为21492.RGB 数据序列的长度为 1370 位。在 1370 位之后,为控制周期添加 20 位间隔。所有控制位(CNTL_IN0 到 CNTL_8)始终设置为零。图 2 显示了数据结构。在测试期间重复 1390 位并行数据模式。信号DE_IN交替使用RGB数据周期和控制周期。

图2.测试数据的序列结构。

测试条件和测量结果

我们测试了三根双绞线电缆,如下表所示。

| 制造者 | 部件号 | 长度(M) | 评论 |

| 日精 | SIODIC F-2WME, AWG26 | 10, 20, 30 | 屏蔽 |

| SIODIC F-2WME, AWG28 | 10, 20, 30 | ||

| 通用电缆 | 5E、AWG24 类 | 10, 20, 30 | 非屏蔽 |

| 载 | MX38 | 20 | 屏蔽 |

为了测试SerDes对的性能与电缆长度和数据速率的关系,我们观察每个电缆长度的误码率(BER),并记录最高并行数据速率,在该速率下,十分钟内没有位错误。数据速率增量为 1Mbps。我们使用这种方法来测量性能,因为关于LVDS SerDes收发器有两个观察结果:首先,如果十分钟内没有错误,几个小时内可能不会有错误;其次,即使在非常低的速率下,在十分钟内观察到错误位时,数据速率(<0.5Mbps)的轻微增加将导致解串器上DE_OUT信号的丢失锁定。因此,我们的方法是在测试时间和测量可靠性之间进行合理的权衡。因此,我们的假设是链路 BER 小于 10-10或 10-11在一定的数据速率下,十分钟内没有发生比特错误。从统计学上讲,我们可以使用公式 1 计算该假设的置信水平:

其中N是在观察周期(例如,十分钟)内通过串行链路传输的位数,p是假设的BER。表2提供了不同数据速率的CL。

| 并行数据速率(兆字节) |

串行链路在 十分钟内传输的 位数 n |

置信水平 p | |

| 误码率 < 10-10 | 误码率 < 10-11 | ||

| 10 | 约12 x 1010 | > 99.999% | 69.88% |

| 20 | 约24 x 1010 | > 99.999% | 90.92% |

| 30 | 约36 x 1010 | > 99.999% | 97.27% |

| 40 | 约48 x 1010 | > 99.999% | 99.18% |

测试结果

表3显示了在各种电缆类型、电缆长度和数据速率下,以及在预加重功能和LVDS均衡器打开或关闭时获得的性能结果。预加重功能集成在MAX9247中,可通过将评估板上的跳线JP15设置为“高电平”来使能。专有的LVDS均衡器安装在MAX9247的LVDS输出端,如图1所示。有关均衡器实现的详细信息,请联系Maxim应用支持。表3中的所有数据都是在室温下生成的。30m 日精AWG26电缆在扩展温度范围内的测试结果如表4所示。

| 电缆类型 | 预加重 | LVDS链路均衡器 | 最大可靠串行数据速率 (SDR) | |||||

| 电缆长度 | ||||||||

| 10米 | 20米 | 30米 | ||||||

| PCLK (MHz) | 特别提款权 (Mbps) | PCLK (MHz) | 特别提款权 (Mbps) | PCLK (MHz) | 特别提款权 (Mbps) | |||

| 日精AWG26 | 关闭 | 关闭 | 34 | 612 | 25 | 450 | 15 | 270 |

| 上 | 关闭 | 40 | 720 | 27 | 486 | 17 | 306 | |

| 关闭 | 上 | 38 | 684 | 34 | 612 | 30 | 540 | |

| 上 | 上 | 43 | 774 | 39 | 702 | 35 | 630 | |

| 日精AWG28 | 关闭 | 关闭 | 33 | 594 | 16 | 288 | 8 | 144 |

| 上 | 关闭 | 36 | 648 | 23 | 414 | 10 | 180 | |

| 关闭 | 上 | 35 | 630 | 33 | 594 | 23 | 414 | |

| 上 | 上 | 41 | 738 | 37 | 666 | 28 | 504 | |

| 通用电缆 CAT5e | 关闭 | 关闭 | 38 | 684 | 26 | 468 | 16 | 288 |

| 上 | 关闭 | 42 | 756 | 28 | 504 | 18 | 324 | |

| 关闭 | 上 | 38 | 684 | 35 | 630 | 32 | 576 | |

| 上 | 上 | 44 | 792 | 42 | 756 | 36 | 648 | |

| 杰MX38 | 关闭 | 关闭 | 16 | 288 | ||||

| 上 | 关闭 | 24 | 432 | |||||

| 关闭 | 上 | 35 | 630 | |||||

| 上 | 上 | 40 | 720 | |||||

| 电缆类型 | 最大可靠串行数据速率 (SDR) | |||||

| 温度 | ||||||

| -40°C | 25°C | 105°C | ||||

| PCLK (MHz) | 特别提款权 (Mbps) | PCLK (MHz) | 特别提款权 (Mbps) | PCLK (MHz) | 特别提款权 (Mbps) | |

| 日精AGW26, 30m | 36 | 648 | 35 | 630 | 31 | 558 |

*请注意,在此测试中,预加重和LVDS均衡器均打开。

在解串器的LVDS输入端口记录了以下眼图。这些图显示了解串器在失真位符号下的数据恢复能力。我们还可以在眼图上看到LVDS链路均衡器的显着改进。

图3.日精AWG26,20m,702Mbps,带预加重和均衡器。

图4.日精AWG26,30m,630Mbps,带预加重和均衡器。

图5.日精AWG26,30米,306Mbps,带预加重。

图6.日精AWG26,30m,306Mbps,带预加重和均衡器。

总结

根据表3和表4所示的结果,我们可以进行以下观察。

虽然CAT5E非屏蔽电缆的性能优于其他两种类型的电缆,但它在应用中可能存在EMI问题。

预加重和LVDS均衡有助于提高链路性能。预加重为短电缆提供更大的提升,后者为较长的电缆提供更有效的改进。对于30m电缆,均衡器可以使数据速率加倍。

扩展温度范围内的性能变化相对较小。

电缆线规可能会限制性能。建议使用大于 AWG28 的线规。

审核编辑:郭婷

-

配合MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板工作2023-06-16 4221

-

关于MAX9247/MAX9218串行器/解串器芯片组的性能测试分析2021-04-12 2416

-

MAX9217/MAX9218中文资料2009-10-01 1100

-

配合MAX9217/MAX9218/MAX9247/MAX92009-04-25 922

-

MAX9247的测试模式-Enabling Test Mod2009-04-22 1713

-

MAX9217/MAX9218 视频链路中的音频数据传输2008-10-22 1410

全部0条评论

快来发表一下你的评论吧 !