时序逻辑程序中推断组合逻辑?

描述

使用always_ff和在灵敏度列表中指定一个时钟边沿并不意味着过程中的所有逻辑都是时序逻辑。综合编译器将推断出每个被非阻塞赋值的变量的触发器。阻塞赋值也可能推断出触发器,这取决于赋值语句相对于程序中其他赋值和操作的顺序和上下文。

然而,在有些情况下,组合逻辑数据流行为将从时序逻辑程序中推断出来。

时序赋值右侧的操作符将综合为组合逻辑,其输出成为触发器的D输入。

如果时序分配的右侧调用一个函数,该函数将综合为组合逻辑,其输出成为触发器的D输入。

围绕着赋值语句的决策语句可能会综合为组合式多路复用逻辑,选择那个表达式作为触发器的D输入。

在begin-end语句组中对临时变量的阻塞赋值,将综合为组合逻辑,其中临时变量成为在begin-end中后续非阻塞赋值推断出的触发器的输入。

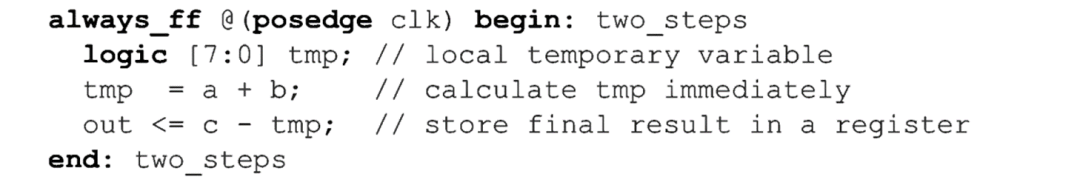

下面非例子说明了在begin-end语句组中对临时变量的阻塞赋值,将综合为组合逻辑。

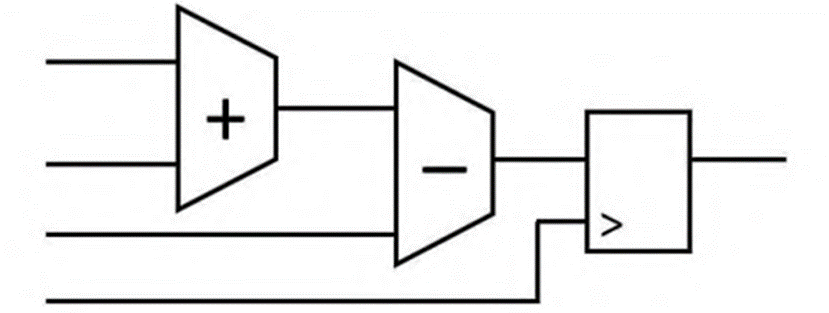

下面就是上面的例子中推断的示意图。

对中间临时变量的阻塞赋值

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA之组合逻辑与时序逻辑、同步逻辑与异步逻辑的概念2022-12-01 1561

-

如何避免组合逻辑程序中的意外锁存2022-12-15 2720

-

RTL时序逻辑的综合要求2023-01-13 3301

-

FPGA中何时用组合逻辑或时序逻辑2023-03-21 1560

-

soc中的组合逻辑和时序逻辑应用说明2023-08-30 2046

-

勇敢的芯伴你玩转Altera FPGA连载25:组合逻辑与时序逻辑2017-11-17 3738

-

【技巧分享】时序逻辑和组合逻辑的区别和使用2020-03-01 2742

-

在FPGA中何时用组合逻辑或时序逻辑2023-03-06 896

-

基于位串编码的遗传归纳逻辑程序设计2009-03-31 488

-

FPGA项目应用之逻辑程序和sdram程序2016-01-21 488

-

FPGA中组合逻辑和时序逻辑的区别2017-11-20 9299

-

组合逻辑电路和时序逻辑电路比较_组合逻辑电路和时序逻辑电路有什么区别2018-01-30 95127

-

组合逻辑电路和时序逻辑电路的区别和联系2023-03-14 9244

-

时序逻辑电路有哪些 时序逻辑电路和组合逻辑电路区别2024-02-06 14396

-

什么是组合逻辑电路和时序逻辑电路?它们之间的区别是什么2024-03-26 7079

全部0条评论

快来发表一下你的评论吧 !