基于载流子复合抑制及传输增强的Sb₂Se₃光电探测器

描述

摘 要

深圳大学梁广兴研究员团队提出一种Sb2Se3光吸收层和异质结界面协同调控策略,实现了Mo/Sb2Se3/CdS/ITO/Ag平面异质结自驱动光电探测器。

文章简介

光电探测器利用半导体对光的吸收将光信号转变为电信号,在国民经济生活和军事上扮演重要作用。为了进一步降低光电探测器成本,实现环境友好、高效稳定且无源自驱动的应用需求,光伏型薄膜光电探测器逐渐成为研究热点。其中,V-VI族二元半导体硒化锑(Sb2Se3)在新型薄膜光电探测器研究领域引起关注,主要由于以下优势:

①Sb2Se3原材料绿色低毒、储量丰富且价格低廉;

②Sb2Se3具有独特的一维晶体结构(c方向为共价键,a和b方向为弱范德华力),强各向异性促使载流子沿着[Sb4Sb6]n链有效输运,在链间则以hopping形式传输,利于消除探测器横向串扰;

③Sb2Se3存在VSb、VSe等点缺陷,对应的缺陷深度为0.4~0.7 eV,有望利用缺陷吸光进行非本征探测,拓宽探测波段;④Sb2Se3二元单相组成易于制备,同时具有较低的结晶温度(133°C),相应探测器与CMOS工艺高度兼容。针对目前Sb2Se3自驱动薄膜探测器由于缺陷复合严重、界面能带错配等原因造成响应度和响应速度不足的关键科学问题,深圳大学物理与光电工程学院梁广兴和陈烁等提出一种Sb2Se3光吸收层和异质结界面协同调控策略。

采用与产业兼容性高的溅射硒化法制备[hk1]择优取向生长的Sb2Se3薄膜,构建Sb2Se3/CdS平面异质结光电探测器。为了进一步提升器件性能,设计Al3+掺杂CdS缓冲层,降低界面及体缺陷浓度、优化p-n结界面能带排列且增加耗尽层宽度,从而有效抑制载流子复合,强化载流子输运。

基于此,该薄膜光电探测器能够实现无外加偏压自驱动工作,响应度提升至0.9 A/W (at 11 nW/cm2)、真实探测度高达4.78×1012 Jones、线性动态范围达到120 dB、开关比为106、响应速度达到ns量级(响应时间24 ns和恢复时间75 ns)。

【主要内容】

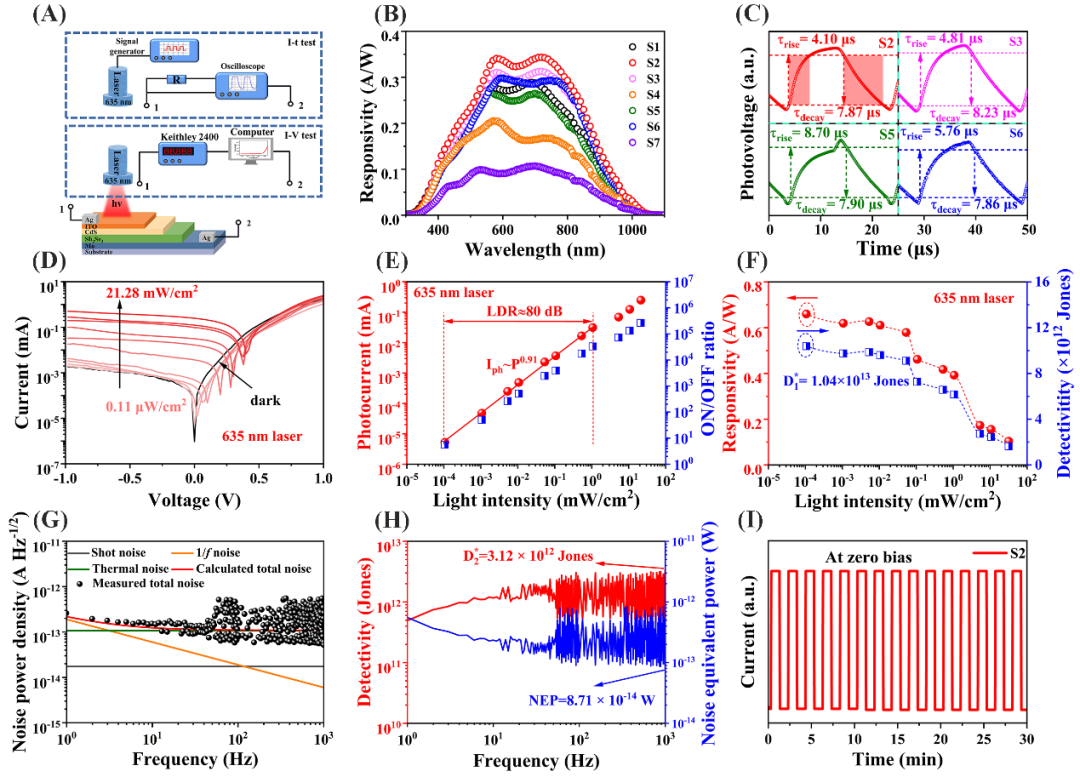

本文通过系统调控溅射硒化工艺参数制备出高质量的Sb2Se3薄膜,据此构建 Mo/Sb2Se3/CdS/ITO/Ag平面结光伏型薄膜光电探测器。图1展示不同工艺参数下器件的光谱响应度和响应速度,以及最优S2器件的关键探测性能,如:在635 nm激光照射下,器件具有明显的整流特性,线性动态范围约为80 dB,响应度最高达0.65 A/W(at 0.11 μW/cm2),综合考虑散粒噪声、1/f噪声和热噪声的总噪声下器件的真实探测度达到3.12×1012 Jones,噪声等效功率低至87 fW,表现出较强的弱光探测能力,同时具有长时间工作稳定性。

图1 (A) Mo/Sb2Se3/CdS/ITO/Ag薄膜光电探测器的结构示意图,以及电流-电压(I-V)和电流-时间(I-T)测试原理图。(B) 薄膜光电探测器的光谱响应度曲线。(C) 代表性S2、S3、S5和S6器件在635 nm激光照射下的时间响应曲线。(D) 最优S2器件在暗态和635 nm激光照射下的I−V曲线。(E) 器件的光电流和开关比与入射光强度的关系。(F) 器件的响应度和比探测度随入射光强度的变化关系。(G) 器件的测试噪声、计算出的散粒噪声、闪烁1/f噪声、热噪声和总噪声随频率的变化关系。(H) 测试总噪声决定的噪声等效功率和实际探测度。(I) 器件在激光照射下的长时间光响应曲线。

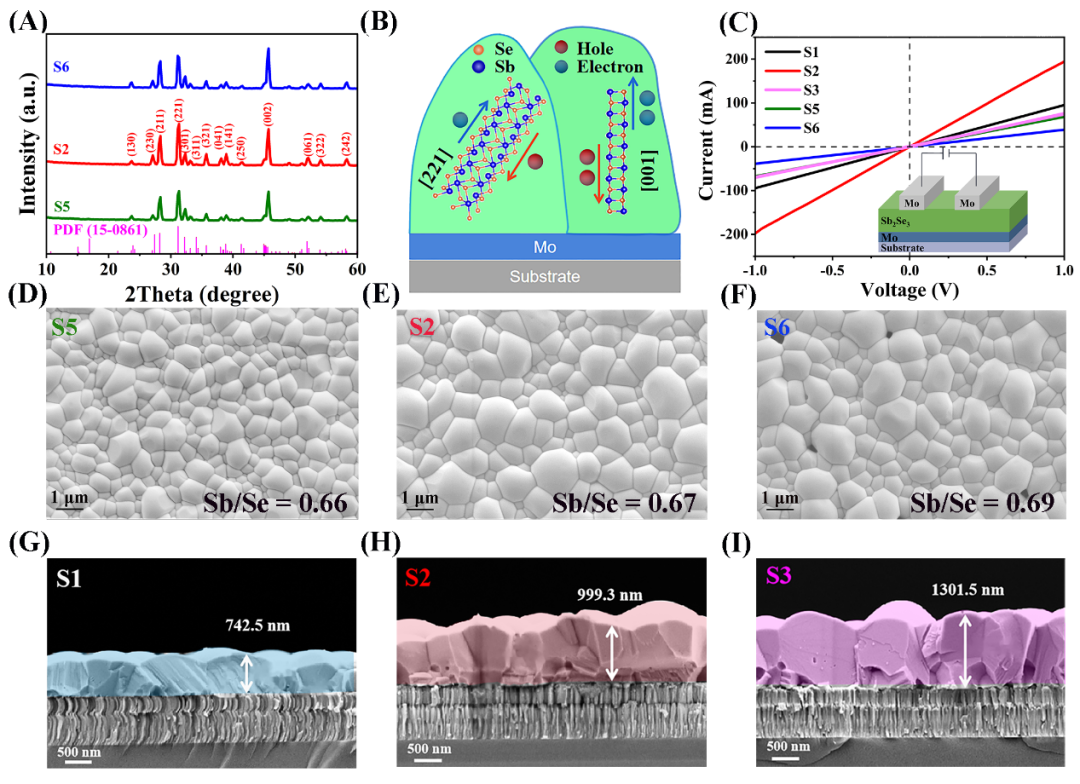

系统表征Sb2Se3光吸收层薄膜的微结构,图2显示了不同工艺参数下的Sb2Se3薄膜的XRD图谱、表面和截面SEM图以及背界面处电阻曲线。分析薄膜的结晶度、生长取向、晶粒大小、厚度、电阻等对器件性能的影响。结果表明Sb2Se3薄膜微米级晶粒紧密堆积,[hk1]良性晶界且高载流子迁移率方向择优生长以及合适的背接触势垒是高性能薄膜光电探测器的基本保障。

图2 (A) 代表性Sb2Se3薄膜的XRD图谱。(B) Sb2Se3晶体生长示意图。(C) 基于Mo/Sb2Se3/Mo结构的Sb2Se3薄膜的暗电流-电压(I−V)曲线。(D-F) Sb2Se3薄膜的表面SEM图,反映表面形貌随硒化反应温度的变化。(G-H) Sb2Se3薄膜的截面SEM图,反映薄膜厚度的变化。

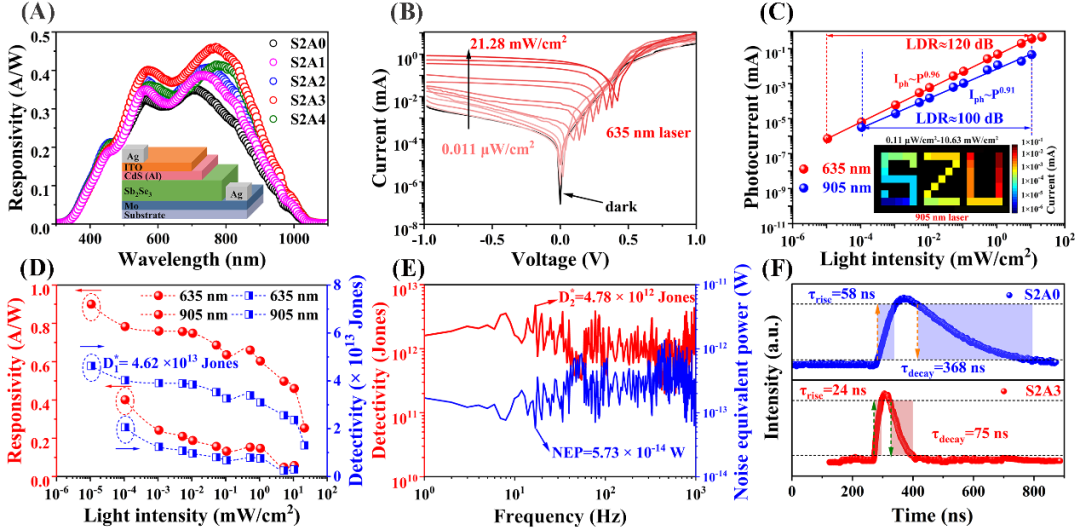

为了进一步提升器件性能,设计引入Al3+掺杂CdS缓冲层,通过Sb2Se3/CdS (Al)异质结界面性能调控以优化薄膜光电探测器性能。图3为不同掺杂浓度对器件光谱响应度的影响以及最优掺杂浓度下器件的关键性能表征。实验结果表明,该离子掺杂可明显提升器件性能。

在635 nm激光照射下,最优器件的响应度提升至0.9 A/W,是Sb2Se3自驱动光电探测器的代表性响应度值;线性动态范围达到120 dB,与商用Si光电探测器相当,同时905 nm激光照射下仍有100 dB,展现近红外光电探测能力;Ilight/Idark开关比高达4.13×106;考虑总噪声条件下创造了4.78×1012 Jones的Sb2Se3真实探测度最高记录;在脉冲激光下,器件的响应/恢复时间分别为24/75 ns,Sb2Se3光电探测器的响应速度到达ns级别。

图3 (A) 原始S2A0及掺杂的S2A1、S2A2、S2A3和S2A4薄膜光电探测器光谱响应度曲线。(B) 最优S2A3光电探测器在暗态和635 nm激光照射下的I−V曲线。(C) 635 nm和905 nm激光照射下,器件的光电流与入射光强度之间的关系,以及“SZU”的成像图(插图)。(D) 器件的响应度和比探测度随入射光强度的变化。(E) S2A3光电探测器的真实探测度和噪声等效功率与频率的关系曲线。(F) S2A0和S2A3光电探测器在脉冲激光照射下的瞬态光响应曲线。

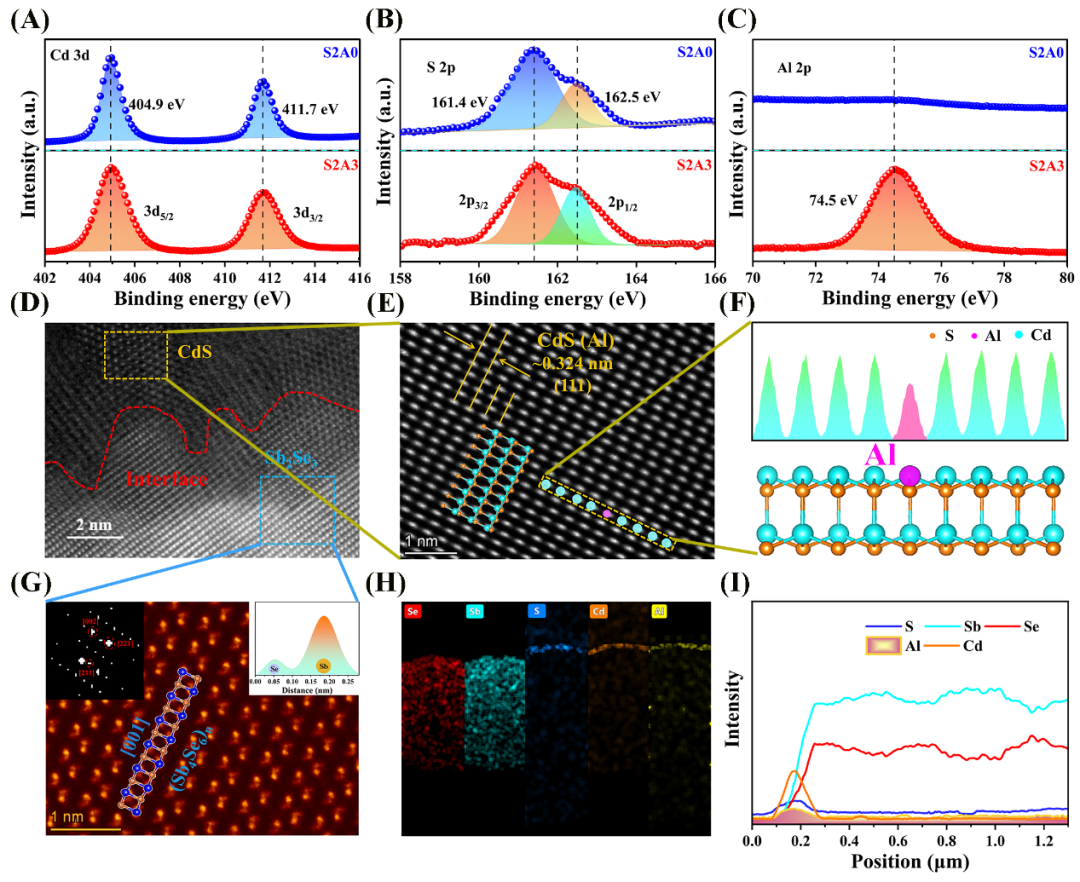

为了阐明Al离子掺杂的作用机制,进行了系统的表征和分析。图4对CdS (Al)和Sb2Se3薄膜进行了微结构表征,首先从XPS图谱中可以明显看到掺杂前后Al 2p特征峰的变化;TEM-HAADF信号强度分布图进一步证实Al离子的成功掺杂,结合EDS元素分布可知Al离子在CdS缓冲层中均匀分布。此外,光吸收层的HAADF-STEM表征也再度证实Sb2Se3薄膜的高结晶性及[hk1]择优取向生长。

图4 (A-C) Al3+掺杂前后CdS缓冲层中各元素的XPS信号变化。(D) Sb2Se3/CdS (Al)异质结界面的HRTEM图。(E) CdS (Al)缓冲层区域的HAADF-STEM图像。(F)从(e)中黄色矩形框获取的HAADF信号强度分布图,以及匹配的原子结构示意图。(G) Sb2Se3光吸收层区域的HAADF-STEM图像。(H) EDS元素面分布图。(I) EDS元素线扫描强度轮廓图。

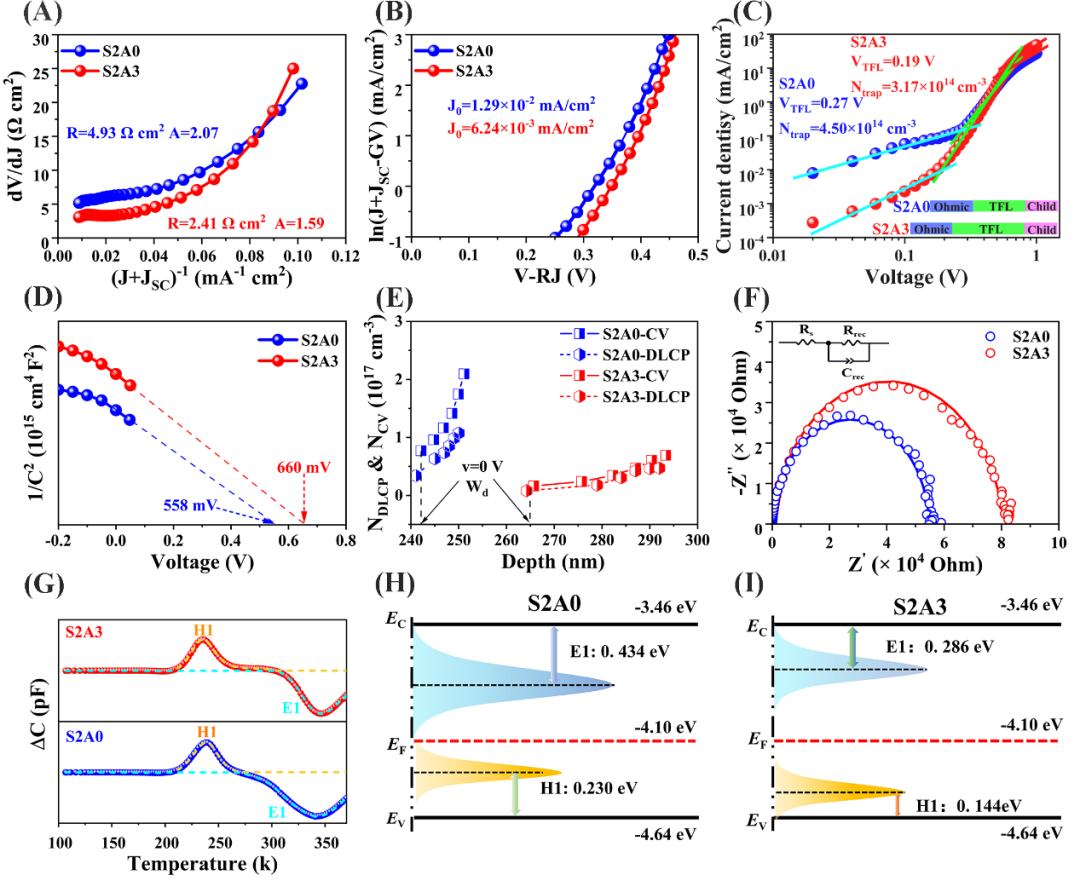

图5对器件的电学性能、界面缺陷以及体缺陷进行了系统表征。结果表明,Al离子掺杂后,器件的二极管品质因子从2.07改善为1.59、串联电阻从4.93 Ω cm2降低至2.41 Ω cm2、反向饱和电流密度从1.29×10-2mA/cm2降低至6.24×10-3 mA/cm2、而内建电势从558 mV提升至660 mV,表明掺杂后与异质结相关的关键电学性能得到明显改善。

同时,器件界面缺陷浓度从4.50×1014 cm-3降低至3.17×1014 cm-3、体内空穴和电子缺陷浓度均表现为缺陷能级变浅且缺陷浓度降低,表明Al离子掺杂同时改善了异质结界面和光吸收层性能,抑制有害缺陷且降低缺陷诱导的载流子复合。

图5 S2A0和S2A3器件的电学性能和缺陷动力学分析:(A) 串联电阻R和二极管理想因子A分析;(B) 反向饱和电流密度J0分析;(C) 暗态J−V曲线分析;(D) 1/C2−V曲线;(E) C−V和DLCP曲线;(F) Nyquist图。(G) DLTS信号曲线;(H) S2A0和 (I) S2A3器件对应Sb2Se3的能带位置和缺陷能级。

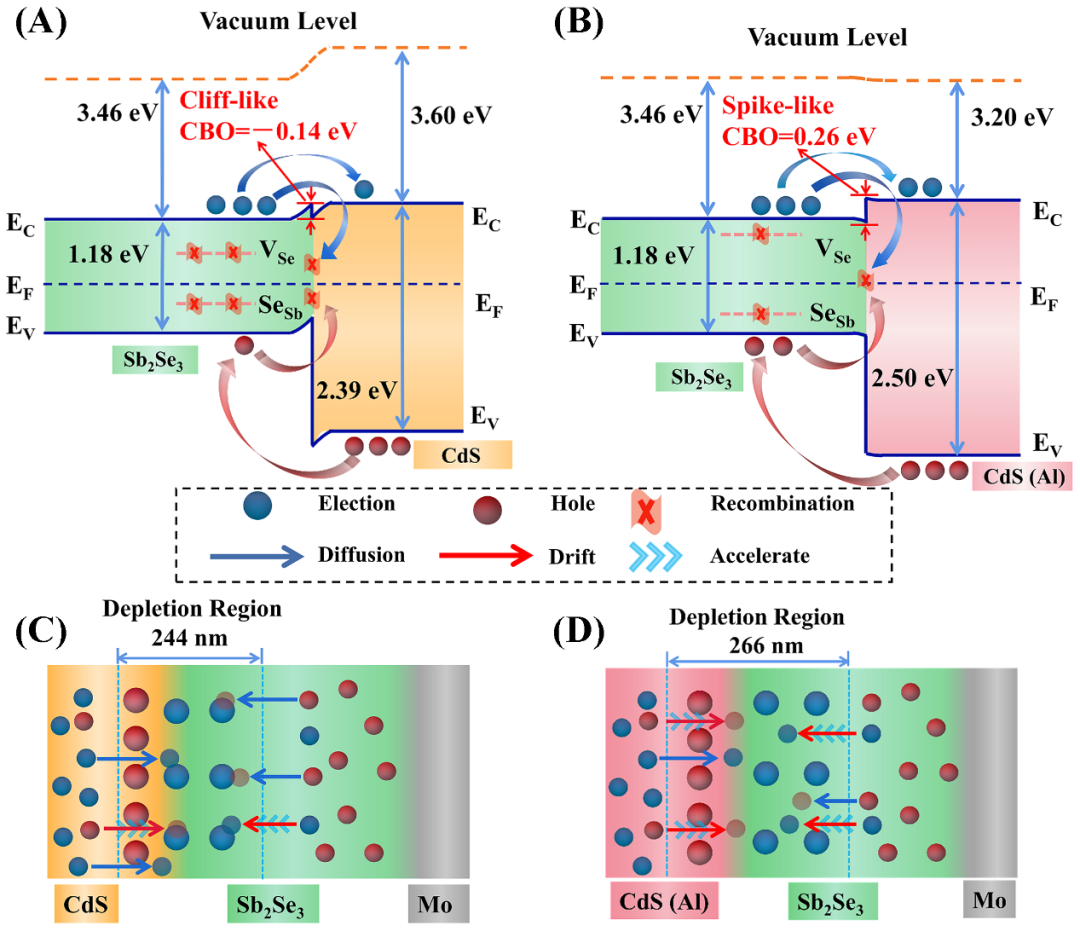

最后,从载流子动力学角度分析了界面缺陷及体缺陷抑制、能带匹配优化对器件性能的影响(图6)。Al离子掺杂可调整CdS缓冲层的费米能级、导带和价带位置,从而优化了Sb2Se3/CdS异质结的能带匹配,从Cliff-like构型转变为理想的Spike-like构型,抑制界面载流子复合,强化载流子分离和输运。

此外,耗尽层宽度的增加可加强载流子的漂移运动,减小自由运动程及非耗尽区的扩散时间,进一步降低载流子复合的概率。最终,载流子复合抑制及传输增强共同促进Sb2Se3薄膜光电探测器性能的提升。

图6 (A-B) Sb2Se3/CdS和Sb2Se3/CdS (Al)异质结的界面缺陷、能带排列示意图,体现载流子传输和复合机制。(C-D) S2A0和S2A3器件中载流子扩散和漂移动力学示意图。

结论:

本文成功构建了Sb2Se3/CdS平面异质结薄膜光电探测器。通过光吸收层工程和界面工程的协同调控可以显著抑制缺陷辅助的载流子复合,增强载流子输运,对应器件性能超过目前文献报道的Sb2Se3基自驱动薄膜光电探测器性能,同时也可以与目前研究较为先进的石墨烯、钙钛矿等光电探测器性能相媲美。该研究对新型高性能自驱动薄膜光电探测器的发展具有一定的促进作用。

审核编辑:刘清

-

光电探测器的主要噪声源及其成因2023-09-01 1346

-

InGaAs/InP光电探测器2023-06-19 947

-

Au/TiO₂复合纳米结构增强热电子光电探测器宽谱响应性能2023-05-19 2381

-

混合硅基光电探测器的各项性能研究2023-04-23 3155

-

综述:铟砷锑(InAsSb)红外探测器的研究进展2022-12-02 5359

-

如何设计一个高增益的光电探测器电路?2021-04-14 3719

-

光电探测器是什么_光电探测器有哪几类2019-12-06 37354

-

新型光电探测器,有出色的传感和成像能力2018-07-05 4264

-

合肥研究院研发出有序Au阵列/PbS薄膜复合光电探测器2018-03-12 5249

-

光电探测器有哪些!如何选型2017-11-28 28827

-

光电探测器工作原理及分类2017-11-27 75113

-

热探测器和光电发射探测器等光辐射探测技术的解析2017-11-18 1297

-

四象限光电探测器的设计方案2010-07-14 2616

-

低压光电探测器电路2009-02-09 4812

全部0条评论

快来发表一下你的评论吧 !