Efinity在Debug时会出现UUID mismatch错误案例分享

描述

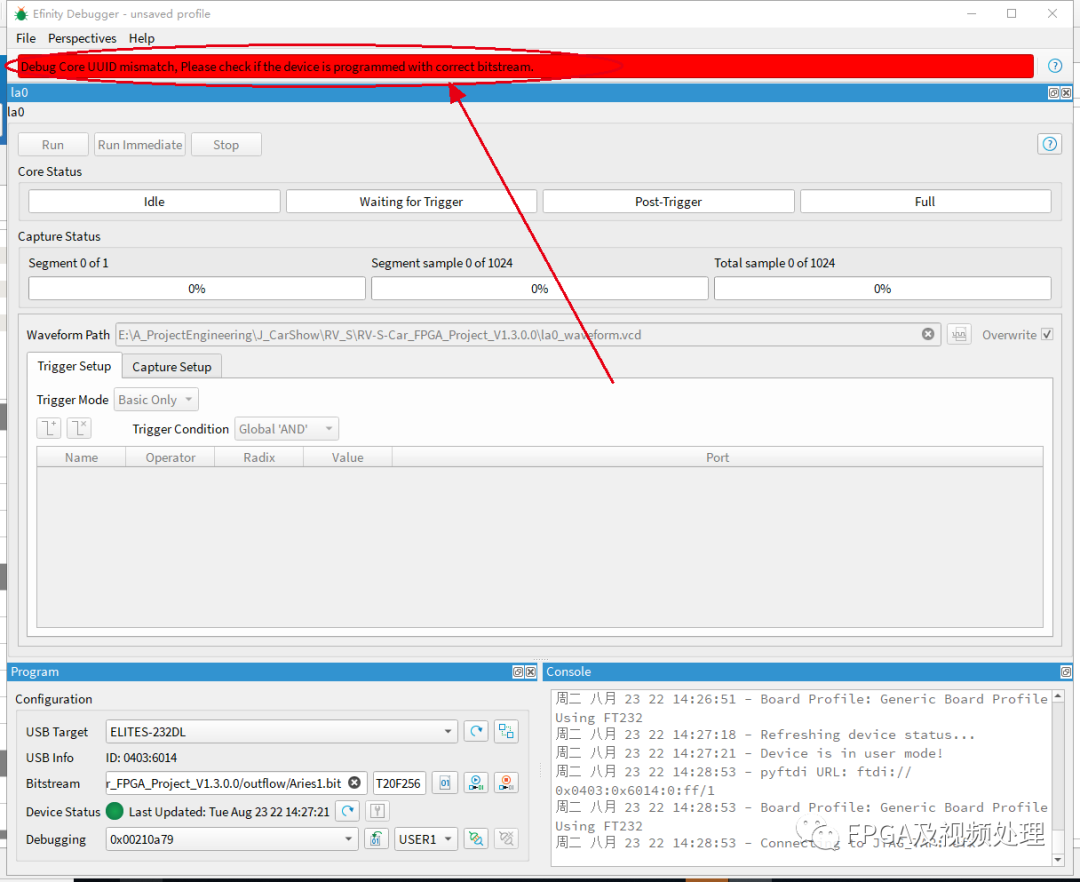

Efinity在Debug时会出现UUID mismatch错误。很多刚开始使用的人经常遇到。下面我们做一个总结。欢迎遇到案例时共同分享。

一般有以下几种原因

(1)程序没运行起来。这种情况CDONE信号没有拉高,说明程序没有加载到FPGA,也可以说程序没有运行起来。

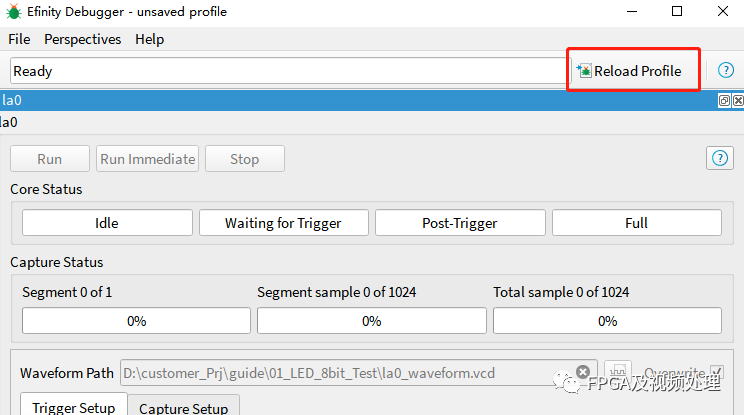

(2)配置文件与debugger文件——即json文件不对应。需要手动从Perspectives -> Profile Editor中重新import Profile,即找到json文件,目前已经添加了upload功能功能解决该问题,在界面的右上角,会提示upload。

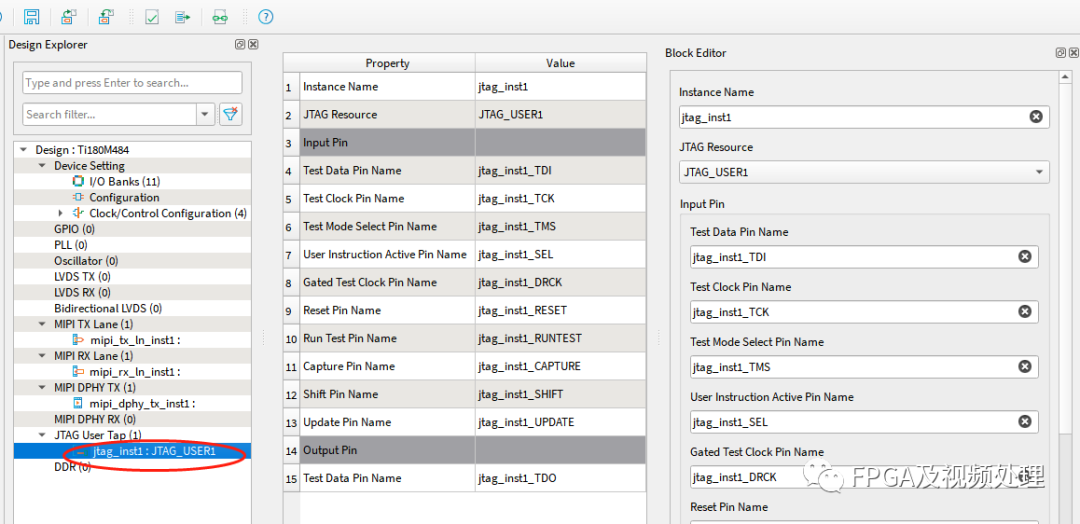

(3)通过Open Debugger添加vio或者la,但是实际上没有在Interface Designer中添加JTAG_USER_TAP。

(4)没有添加Debug;

(5)JTAG_USER_TAP接口与debug_top例化部分连接出错,比如名字不对。

(6)TI60会存在A版本与A1版本有区别不连接不上,2022.8月份之后不存在该问题。

(7)添加了vio和la但是没有添加debug_top.v到工程中,依然编译过去,连接时也会提示UUID mismatch.

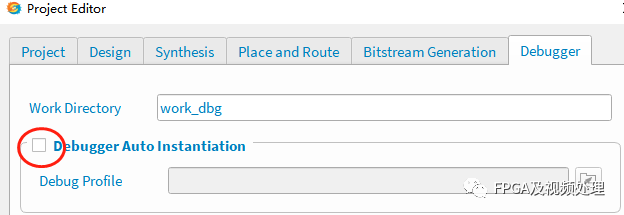

(8)Debugger Auto Instantiation没有打开。

(9)有客户第一次的设计调试信号线 TCK TDO TMS(10K上拉) TDI(10K上拉)是直连的使用正常。第二次在TCK,TDO,TMS和TDI串联了100欧的电阻,并且TCK进行了4.7K下拉,就出现了UUID mismatch。

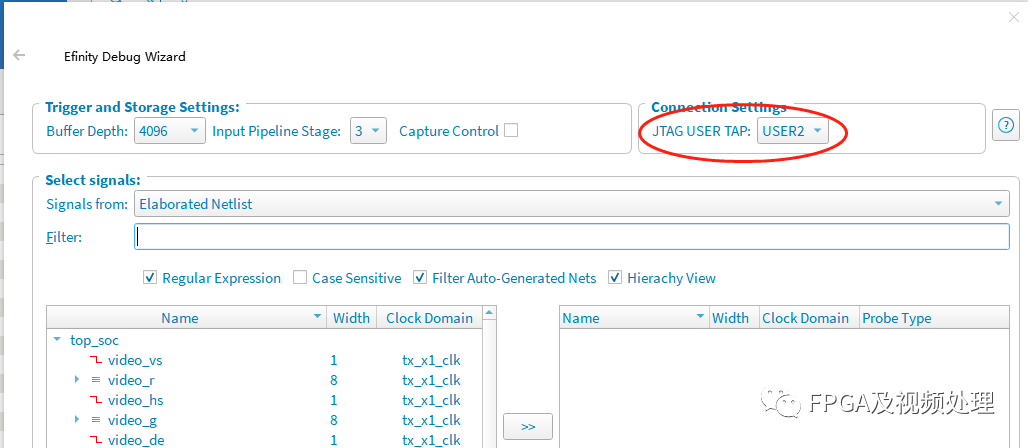

(10)JTAG USER TAP不对应。比如下图选择了USER2,但是连接时选择的是USER1.

(11)T20以下器件在通过JTAG配置时必须要连接CRESET,T8F81还需要连接SSN信号。如果没有连接的话,可能存在看似JTAG配置成功,但是实际上配置的程序并没有运行,依然只运行了上电第一次配置的程序。此时UUID肯定也不匹配,因为新程序没有运行。

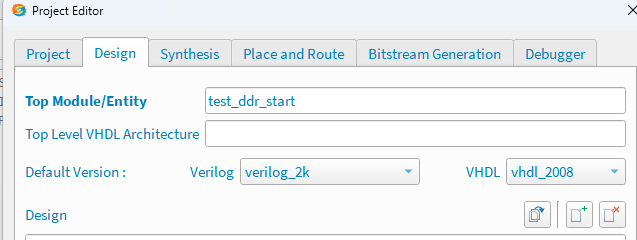

(12)没正确指定top文件。如果没有指定top文件,软件会自动选择top文件,很多时候就是用户自己定义的top文件。

(13) JTAG下载器连接有问题。

说明:upate1 添加了(12)(13)两项。

审核编辑:刘清

-

Efinity debuger常见问题总结-v22024-07-11 3427

-

Efinity debuger常见问题总结-v32025-01-16 2437

-

MDK调试时出现MEMORY MISMATCH错误的原因及解决方法2008-08-02 5997

-

添加库文件时会出现错误2013-02-03 4261

-

为什么我在设置ODBC时,点击测试时会出现下面的错误2015-05-10 3315

-

CC2640 编译和debug出现错误2016-03-28 2879

-

FLASH和upp例程合一起后,发现flash读写数据时会出现DMA传输错误2019-09-11 1136

-

为什么Eclipse调试运行Debug时会出现以下错误?2019-10-31 2013

-

为什么单板串口在发送数据时会出现不可预知的错误呢2021-11-10 1129

-

对stm32进行编译时会出现哪些问题呢2021-11-18 857

-

为什么在websocket中将数据从手机发送到esp32服务器时会出现错误?2023-03-02 569

-

Debug Core UUID mismatch案例总结2023-02-06 3213

-

PDF输出时出现错误提醒的解决方案2024-01-12 3883

-

Efinity debugeri常见问题总结-v12024-05-20 1931

-

Efinity debuger常见问题总结-v42025-06-10 1485

全部0条评论

快来发表一下你的评论吧 !