Xilinx IP GTY调试心得

描述

本文为调试心得

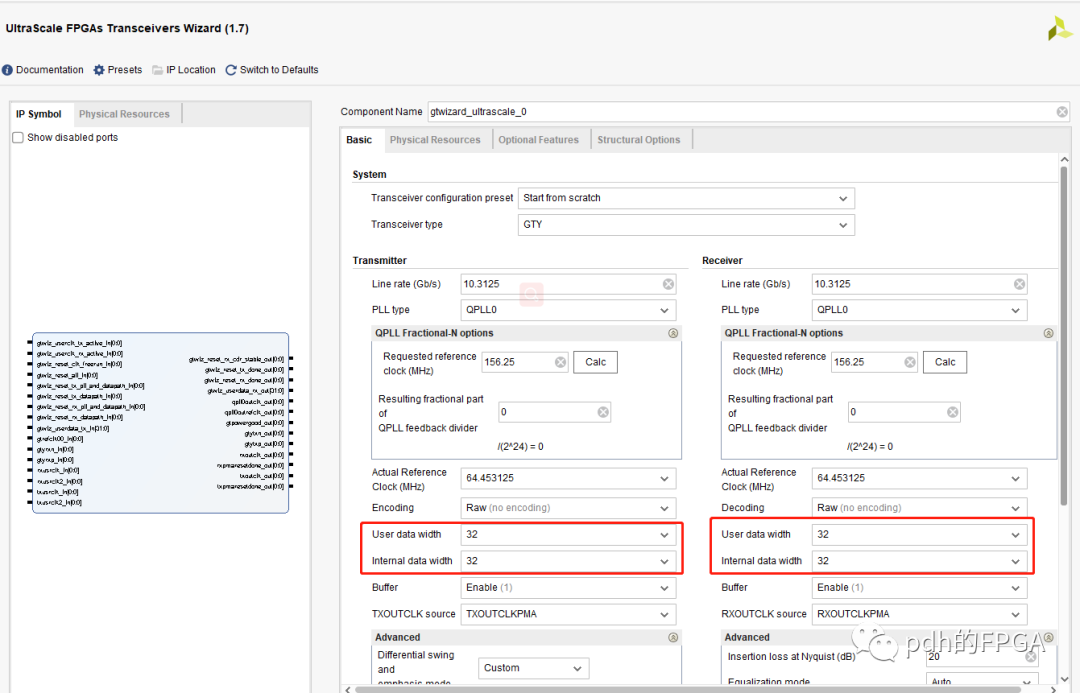

1.TXUSRCLK为用户接口时钟,接的PCS层,TXUSRCLK2接的PMA层,TXUSRCLK对应的GUI界面为user data width,而 TXUSRCLK2 对应的 GUI界面为internal data width。

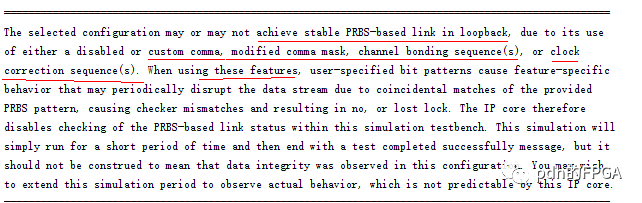

2.两者的位宽可以相同,也可以不同,相同时,TXUSRCLK = TXUSRCLK 2,当在使用时,如果IP设置 8B/10B编码,在控制用户接口时,没有什么要特别注意的。而如果IP设置64B/66B编码,那么在TX用户接口,控制tx sequence时时序会不同,需要特别注意,并且根据user data width 的不同,tx sequence 的掩码位置也不同,更具体的信息需要去阅读手册ug578,pg182。

3.8B/10B编码是不需要你进行 bit移位来还原数据的,但64B /66B 编码是需要的。

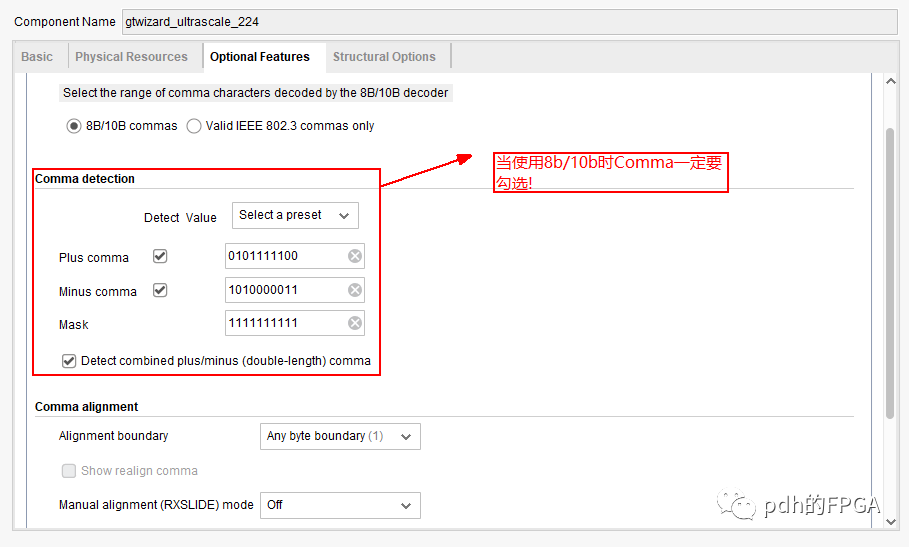

4.使用8b/10b编码时

否则

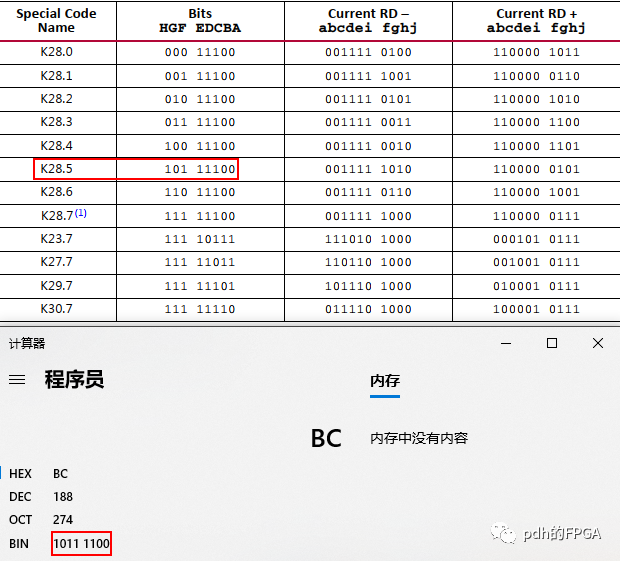

5.使用的K码一般使用k28.5,即BC

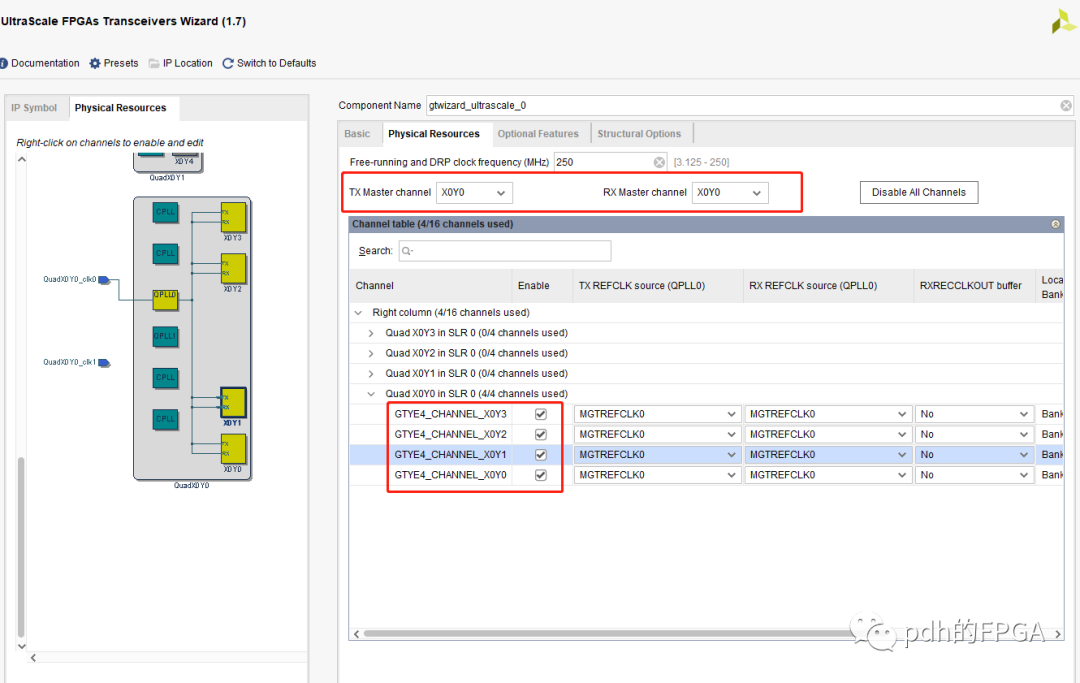

6.接下来是最重要的使用问题,通常,我们使用GT IP大多会选 4个lane

在IP核GUI界面中,选了x0y0-x3y3 共4个通道,然后GUI界面有tx master channel和 rx maxter channel 这个选项,当使用gt例化一个quad的时要注意master所在的lane在外部硬件上一定要确保连接不可悬空,否则导致其它lane连接不稳定。上板实测发现设置主为x0y0,如果你的x0y0的硬件没接,那么你的x1y1-x3y3会工作不正常,硬件上一定要接x0y0,其他lane才会正常工作。

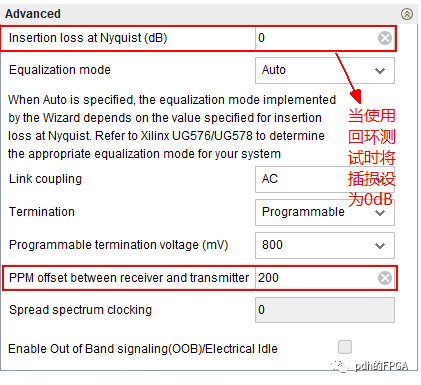

7.PMA层设置

审核编辑:刘清

-

如何申请xilinx IP核的license2024-10-25 2731

-

HK32MCU应用笔记(六)| HK32MCU芯片调试心得2023-09-18 1782

-

Versal GTY仿真:初始化,复位和速率变更2022-11-23 2209

-

如何使用Xilinx AXI进行验证和调试2018-11-20 4858

-

是否有关于为GTY收发器发布IBERT的讨论?2018-09-28 3314

-

基于QEMU系统模拟器Xilinx/QEMU的运行与调试2018-07-04 10377

-

图解JLINK在ADS下调试心得2018-04-09 5023

-

Xilinx CORE生成器IP列表名称及说明详解2017-11-18 5630

-

Xilinx DDR2存储器接口调试代码2016-06-07 927

-

下载Xilinx IP Core2013-06-20 4196

-

DDS 调试心得2011-05-25 682

全部0条评论

快来发表一下你的评论吧 !