终于搞懂模拟电路中的ADC!1

模拟技术

描述

一、基本介绍

ADC(Analog to digital converter)、DAC(Digital toanalog converter)为数据转换芯片,本质上是信号链芯片(模拟芯片按照功能可以分为信号链芯片和电源管理芯片两类)中的一种。ADC是将模拟信号转换为数字信号,DAC 相反。其中ADC 在两者的总需求中占比接近80%。ADC 和DAC 属于模拟芯片中难度最高的一部分,被称为模拟电路皇冠上的掌上明珠。

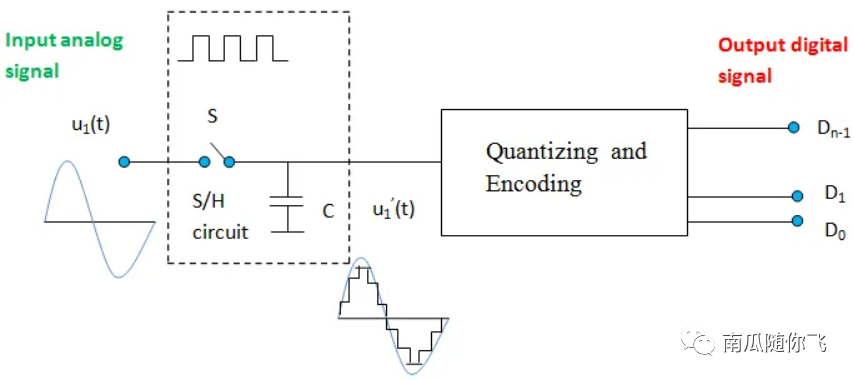

ADC的原理:通过采样-保持-量化以及编码电路,将输入的连续波形的模拟信号变换成间断的数字型号。

图片来源:百度

通常情况下A/D转换需要经过采样-保持(S/H:Sampling & Holding)、量化、以及编码4个过程。

1.采样

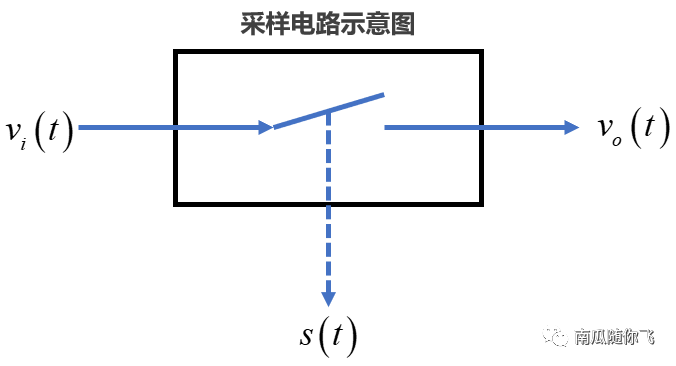

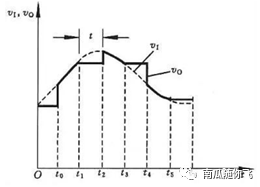

采样是将连续变化的模拟波形通过与采样脉冲串(或者周期方波信号)做卷积运算,将连续变化的量变成时间离散的模拟量,如下图所示。

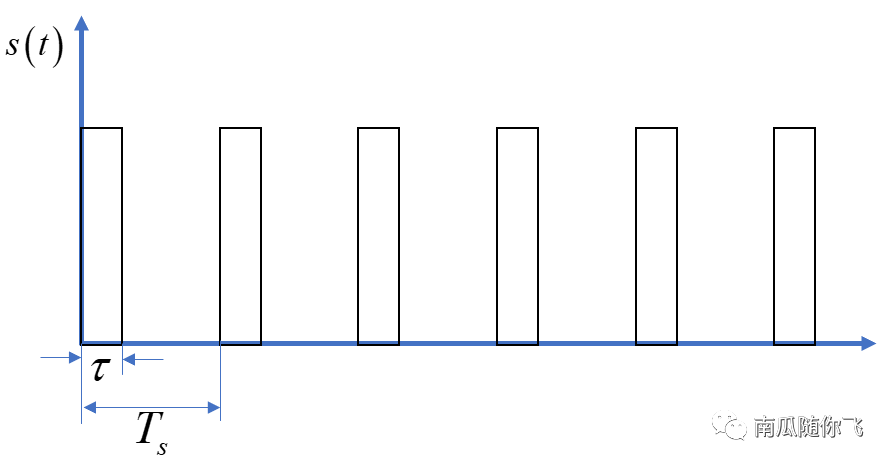

S(t)是采样传输控制信号,脉宽为τ,脉冲周期为Ts。在脉宽时间τ内控制信号导通,采样输出端口有输出信号Vo(t);在Ts-τ的时间内,控制信号关闭,采样输出端口无信号输出。各个周期脉冲对应采样输出后的结构如下图所示。

图片来源:百度

当S(t)的脉冲频率越高,采样时间间隔越小,信号保留越多,得到的信号波形越接近原始波形。根据奈奎斯特定理,S(t)对应的采样频率fs与输入信号的最高频率分量fmax之间必须满足fs≥2fmax,才能将原始信号的信息保留下来。工程上为了能够满足实际使用,一般都采用fs≥(3-5)fmax。

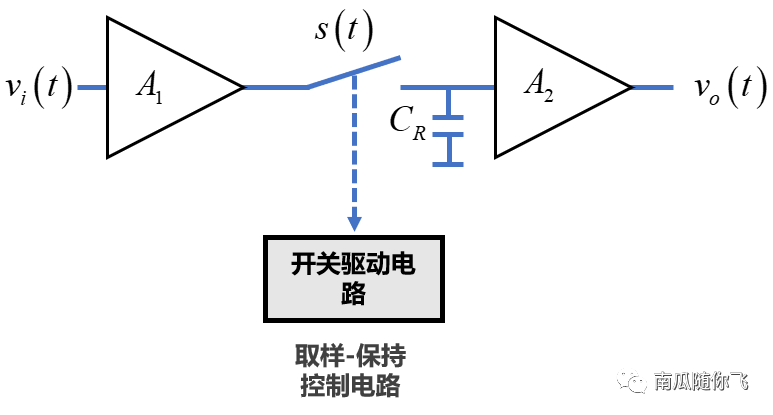

2.保持

上面提到的采样是通过脉冲串实现的,得到的输出结果在时间上是隔离的,实际过程中采样电路每次取得的模拟信号转换为数字信号都需经过一定的时间,这是为了为后面的量化编码体提供一个稳定值。所以每次取得的模拟信号都必须要通过一个保持电路,保持一段时间。实际上采样和保持的过程是通过采样-保持电路同时完成的。

在t=t0,控制电路闭合,电容充电,此时v0=vi。在t0-t1时间内采样,t=t1断开,电容放电,采样输出保持平稳,最后得到的波形如上图所示。这个过程就是保持阶段。

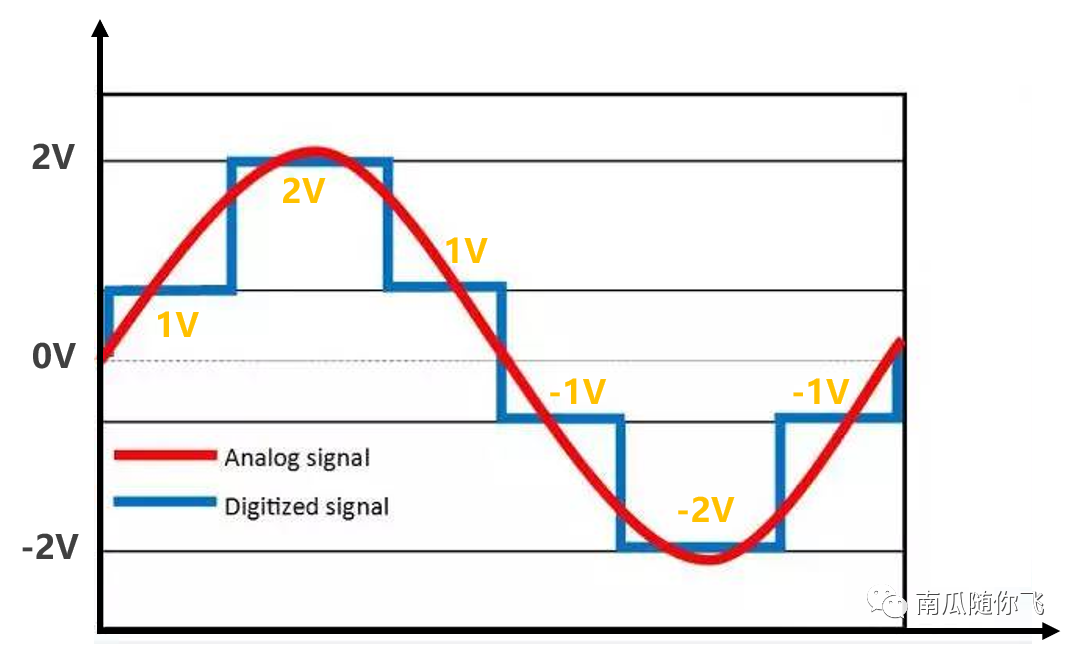

3.量化

通过采样得到的数字信号在幅度上面是不连续的,量化就是将抽样得到的瞬时值将其幅度离散,用一组规定的电平把瞬时抽样值用最接近的电平值表示。简单来说就是把输入信号幅度连续变化的范围分为有限个不重叠的子区间,每个子区间用对应的一个确定数值表示,其内的输入信号就以该数值输出,从而将连续输入信号变为有限个离散值电平的近似信号。

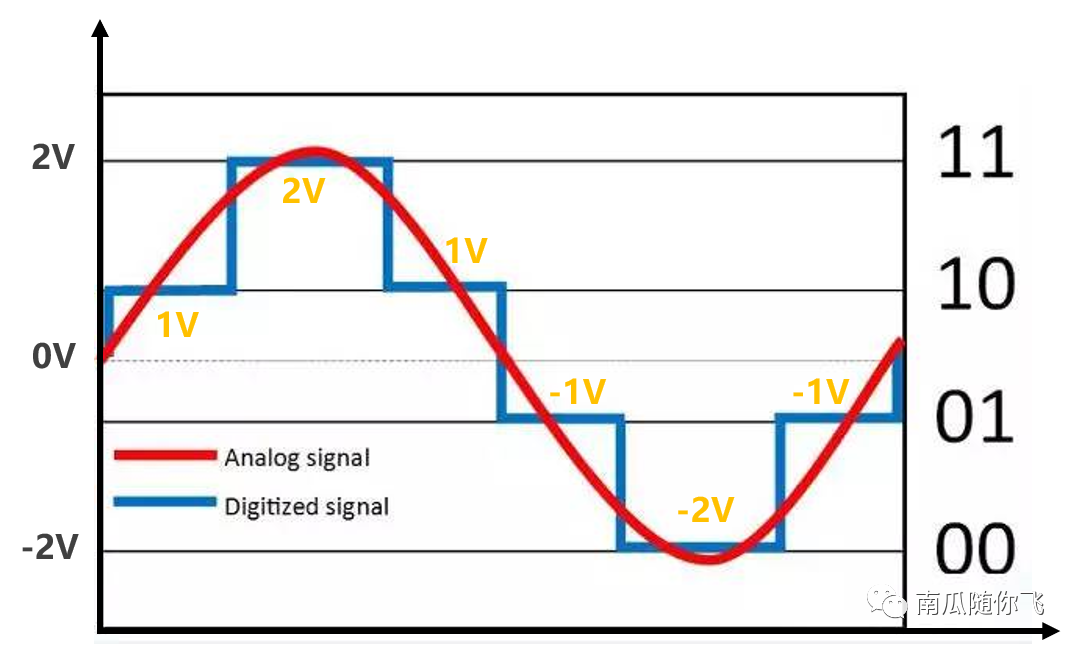

4. 编码

编码就是将量化过后的电压幅值用对应的二进制码对应进行表示。

5.名词解释

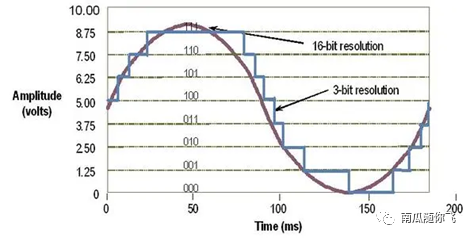

- 分辨率;

分辨率,简单来说就是对应了ADC中的位数。表征了能够将一个信号进行最小量化的尺度,位数越多表示这个ADC的分辨率越高,对于信号的描述就越准确。如下图所示一个16bit和3bit对信号进行量化表征的细节程度相差很大。位数越高,对信号的量化越准确,转换的精度越高。

图片来源:百度

2)采样率;

采样率,Sample PerSecond,SPS,每秒取得的样本数量。代表了ADC的采样速度,当采样率越高,就代表ADC的速率越高。

3)射频采样;

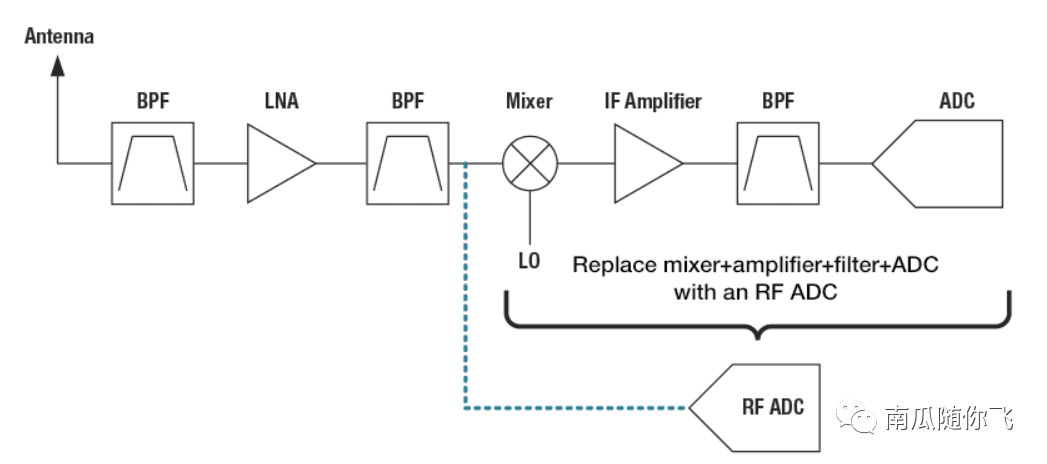

射频采样就是将ADC直接用在射频信号中。传统的采样是需要将输入信号通过一个下变频器件,将信号频率降低到一个较低的中频频率之后再做AD变换。射频采样是不需要将信号经过下变频,而直接对输入的射频信号进行AD变化,其在信号链路中的位置如下所示。

图片来源:ADI官网

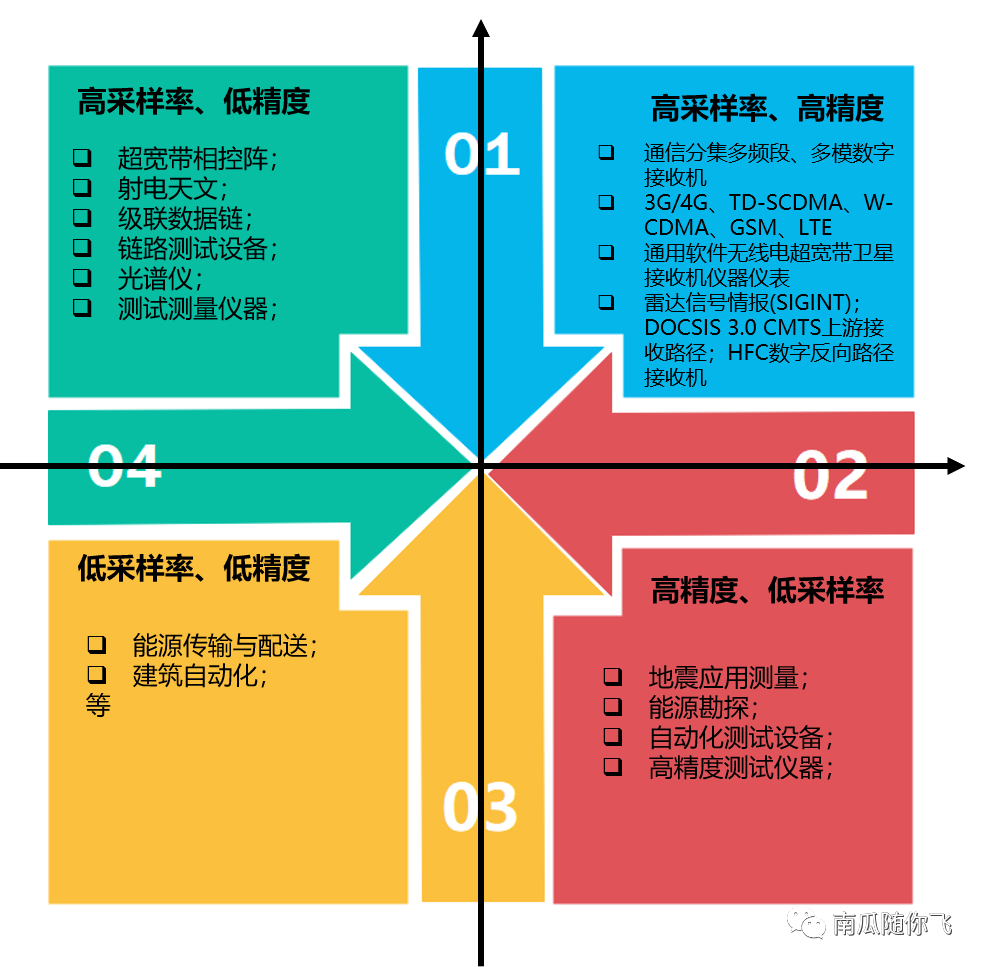

采样率和分辨率是两个相互矛盾的指标,当位数越高,需要采集、比较的数越多,相应的ADC芯片的架构越复杂,比较器越多,运行的时间越长,速度越慢。

二、ADC分类

ADC按照工作原理可以大致分为两大类:

- 直接转换型ADC:将输入电压信号直接转换为数字代码,不需要经过中间任何变量;

- 间接转换型ADC:将输入电压信号转变成某种中间变量(时间、频率、脉冲宽度等),然后再将这个中间变量转换成数字代码输出;

按照采样定理的原理可以分为两种:

- 奈奎斯特采样ADC:采样率=2信号最高频率;

- 过采样ADC:采样率>2信号最高频率;

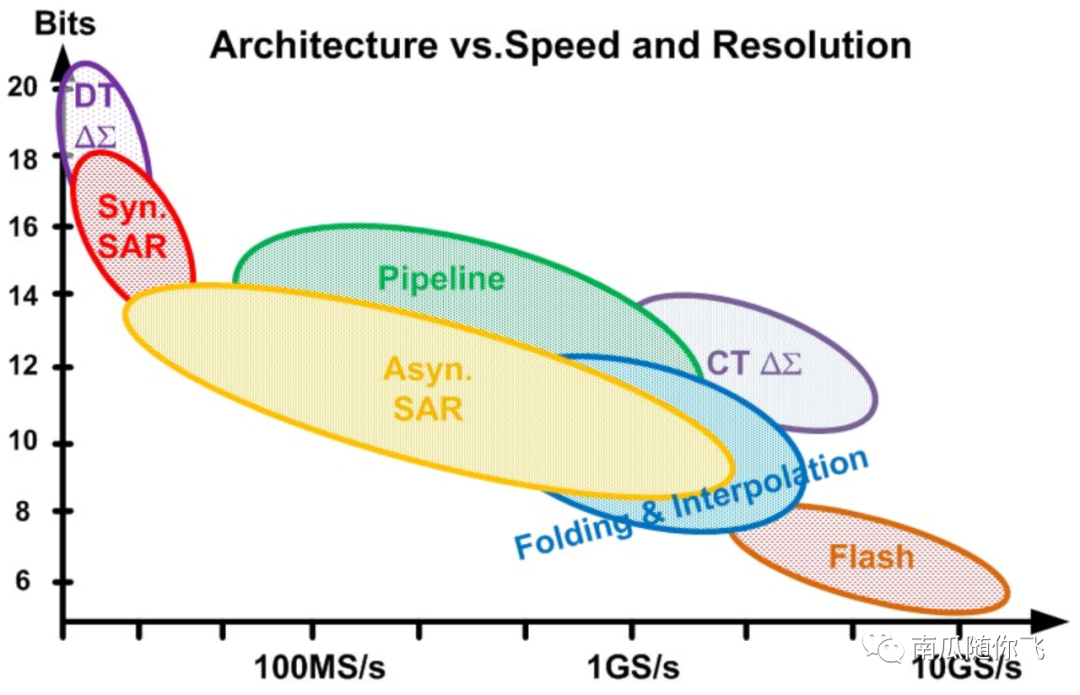

按照不同的精度和采样速率可以分为Δ-Σ 、SAR、Flash、Folding & Interpolation、Pipeline等不同种类。这几种不同的ADC之间精度和速率的关系如下图所示:

图片来源:髙速低功耗逐次逼近式ADC研究与实现

1.Flash

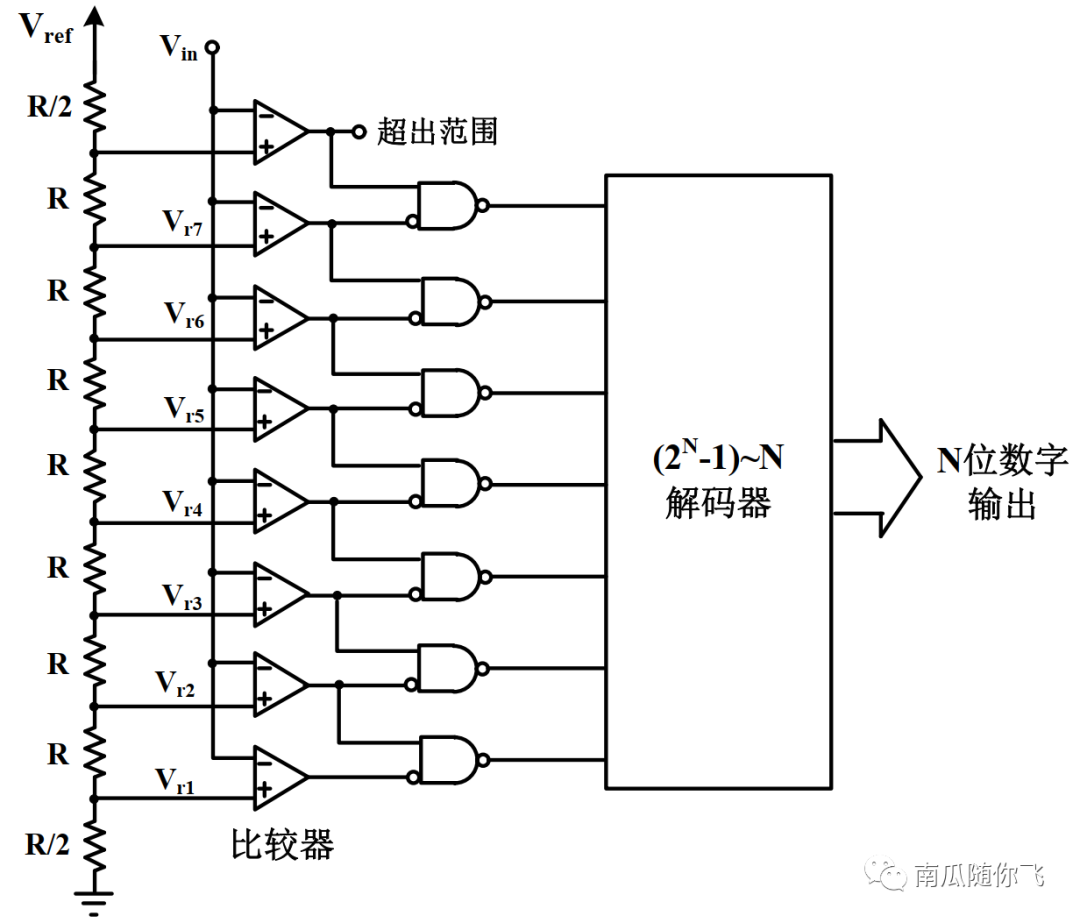

Flash是一种高速的ADC架构,是目前成熟的采样速率最高的ADC架构。其架构如下图所示。

图片来源:高精度Σ-Δ ADC设计

从它的结构中可以得到,输入电压Vin与参考电压Vref是分别同时接入到不同的输入端口进行对比,也就是输入信号是被多个端口并行处理,执行一次运算只需要一个时钟周期。

也正是因为其并行运算的架构使得其无法做到很高的分辨率(既高位数)。上图显示的是一个3位,用到了7个比较器。一个N位的ADC采用Flash架构,需要2的N次方-1个比较器,因此增加一位,就需要增加2的N次方个比较器。这也是导致Flash无法做到太高精度的主要原因,精度越高、架构越复杂、芯片面积越大。

另外,比较器对于输入电压都是并联的,呈现十分大的输入电容,需要用很大的功率来驱动这一类ADC,对于功率、功耗等方面也受限制。

目前Flash最高可用位数为8bit,高于8bit之后就需要采用其他架构。8bit的Flash ADC速率可以达到1GS/s,6bit的ADC可以达到12GS/s。

Flash ADC除了可以作为单片使用,还经常在Pipeline ADC、Δ-Σ ADC、SAR ADC中作为子ADC使用。

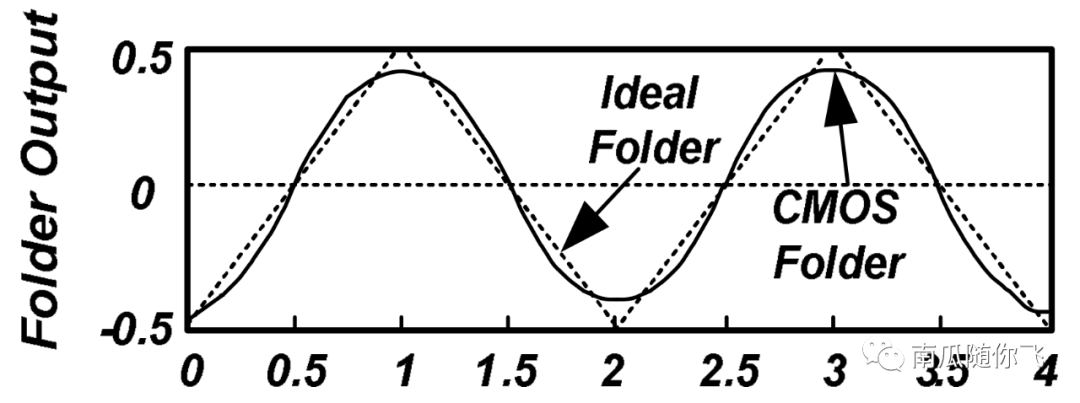

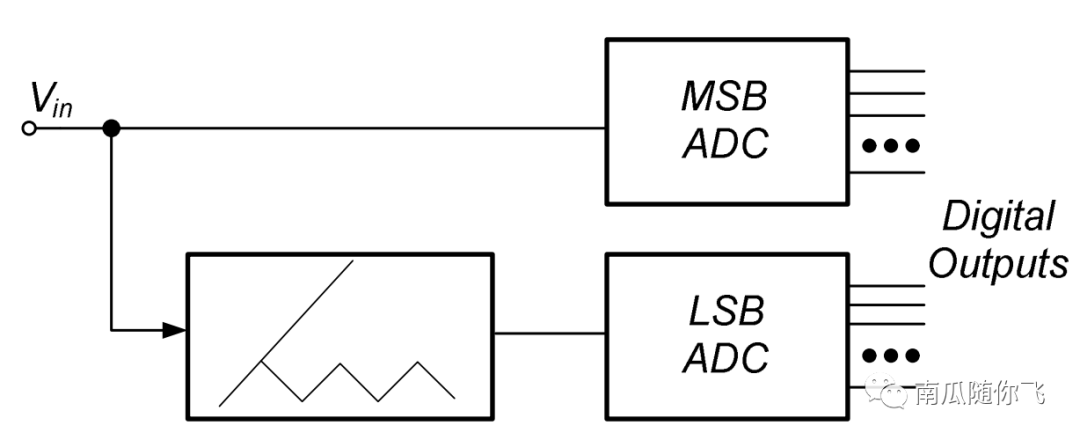

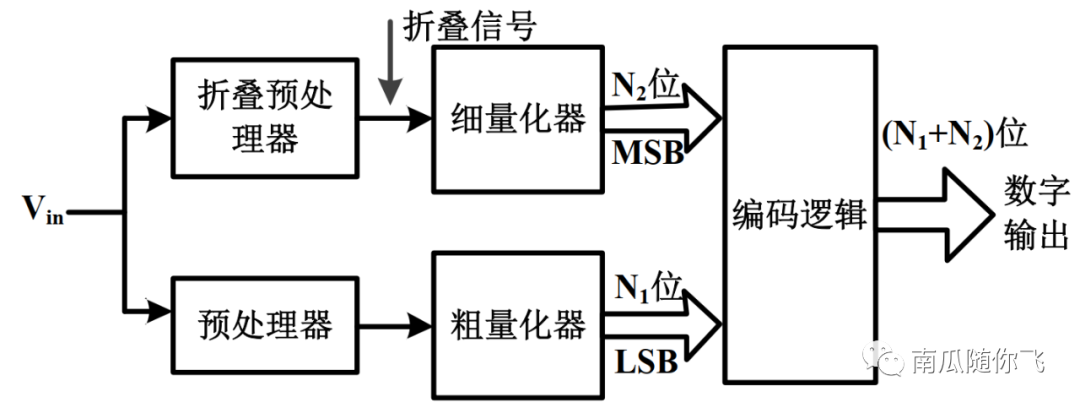

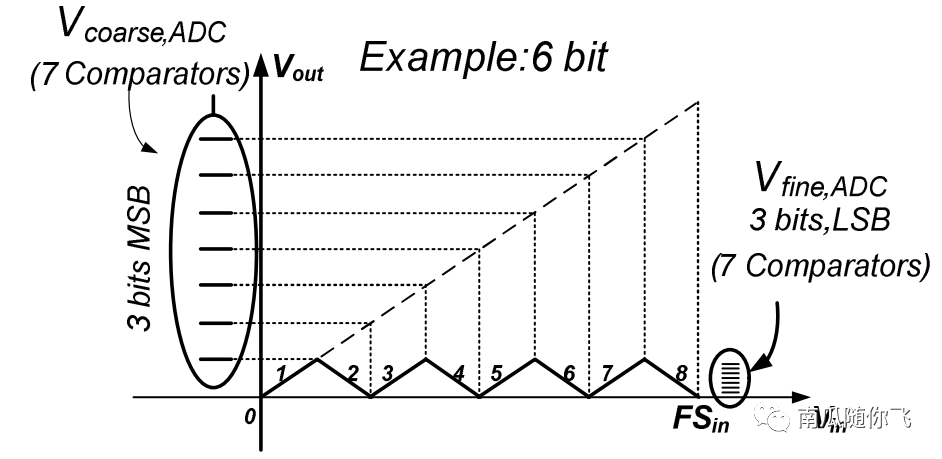

2. Folding & Interpolation

Folding & Interpolation,折叠内插式ADC,其核心思想是划区、分段再组合。

划区:将输入型号进行折叠划区,如下图所示,输入信号被划分为四个区域,然后分别对不同区段进行量化。

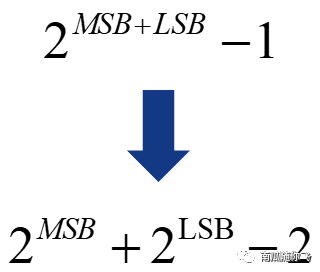

分段:将输入电压分成两路信号,一路直接通过低精度Flash ADC,进行粗量化,得到高位的MSB;另外一路通过折叠放大器分成小的量化区间再进行细量化。

组合:将两路信号对应的MSB+LSB位数组合成一个完整的精度表示。

采用Folding& Interpolation架构,会相比与采用Full Flash架构用到的比较器少很多。系统架构简化。同时其处理的精度得到提高、采样的速率相对较高。

Folding & Interpolation ADC的特点如下:

- 由于没有反馈环路,可以保持较高的采样频率,仅次于Flash ADC;

- 能够实现高采样率以及12bit的精度,但是需要复杂的校准电路;

- 需要用到很多高速放大器,功耗大、电路规模大,适用于对功耗和面积不敏感的高速应用;

-

jf_45852653

2024-06-03

0 回复 举报赞 收起回复

jf_45852653

2024-06-03

0 回复 举报赞 收起回复

-

adc是什么意思 adc在电子电路中的应用2024-10-31 14734

-

远场应用中的模拟麦克风和ADC系统2024-08-28 364

-

模拟电路中的失真是什么意思?模拟电路中都有哪些失真?2023-10-18 7897

-

ADC模拟电路皇冠上的明珠(1)2023-07-03 5923

-

终于搞懂模拟电路中的ADC!22023-02-20 7294

-

#电路知识#电路分析 ADC中的电源设计—如何设计最佳ADC电源(1)电子技术那些事儿 2022-08-20

-

实用模拟电路设计技术Section4高速采样ADC2022-08-01 571

-

ADC数字地和模拟地的接地原理2022-05-10 5114

-

如何使用LTspice模拟 SAR ADC 模拟输入?2022-04-12 52372

-

模拟ADC的前端2018-09-07 2584

-

ADC外围电路设计方法2012-03-15 10071

-

ADC电路2011-07-15 3972

-

ADC外围电路的设计2011-02-11 5336

全部0条评论

快来发表一下你的评论吧 !