终于搞懂模拟电路中的ADC!2

电子说

描述

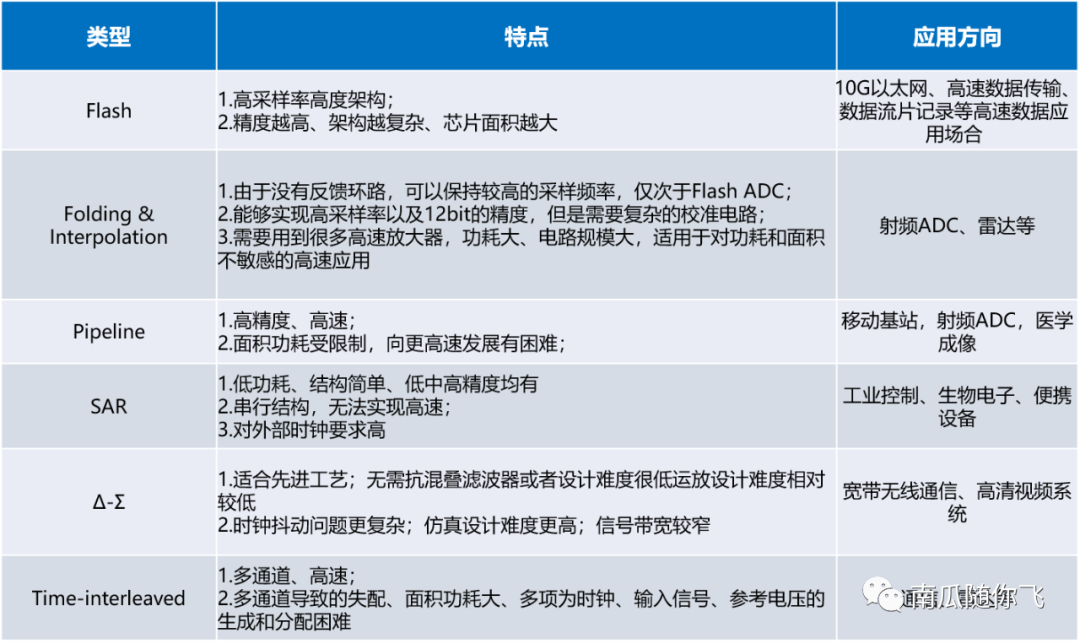

3.Pipeline

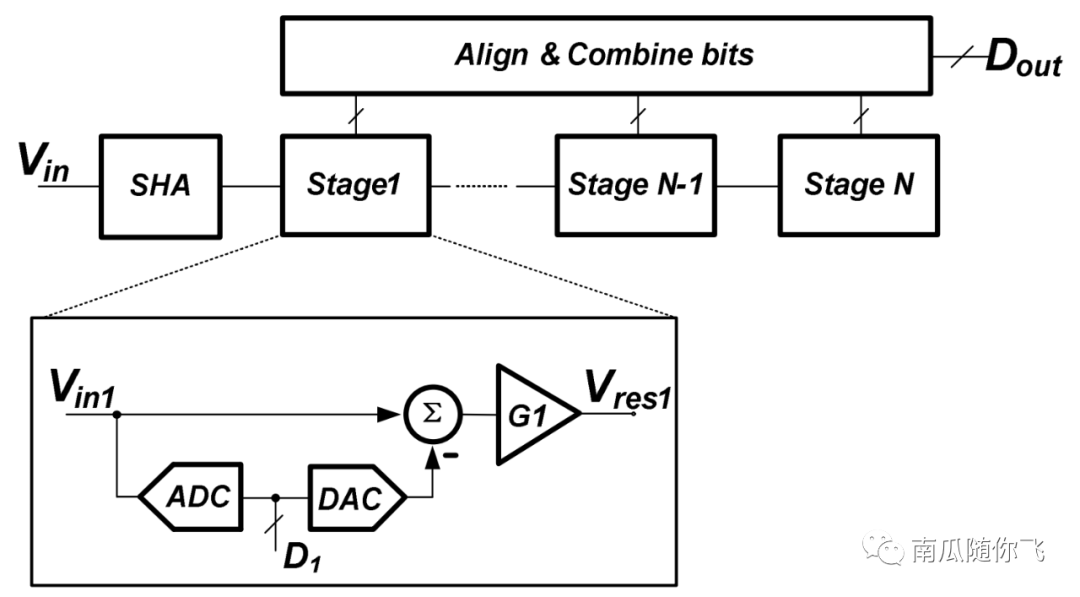

Pipeline ADC,流水线式ADC架构。正如其名字一样,采用了类似于加工产线上的流水线生产流程和原理,将输入信号进行分段处理,然后逐个传输到每个ADC完成对应的采样+量化的工作,最后拼接输出。与Folding & Interpolation结构不同,Pipeline将输入信号在时间和空间上都进行分段了,前者仅在空间上分段,然后并行处理两路信号。

上图所示为Pipeline ADC的基本结构,可以看到输入信号需要经过不同的流水线节点Stage。每一个Stage中包含了一个子ADC、一个子DAC以及一个残差放大器(Residue Amplifier)。每一个Stage在前半个时钟内接收信号完成一次采样,然后在后半个时钟内由子ADC完成量化,输出量化结果D。

Pipeline ADC需要保证分段的量化在半个周期内完成,同时其不想Flash或者Folding & Interpolation同时完成所有位数的量化,因此其在高精度的基础上还可以保留一定的速度优势,但是相对于Flash和Folding & Interpolation高速来说稍显不足。

主要的优点:

- 高精度:其每级的残差放大可以抑制后级的误差,类似于射频链路中的级联噪声作用,提高了整体的精度;分段结构能够更灵活的对每一位进行校准,能够达到10-16bit;

- 高速:目前可实现单通道250MS/s+16bit,1.5GS/s+12bit的性能,适用于基站、通信、雷达等应用;

- 量化校准方便,能够通过灵活的校准算法提高精度、降低功耗;

主要的缺点:

- 随着工艺制程不断降低,晶体管的沟道效应增强,本征增益下降,放大器难以保持高增益,因此限制了残差放大器的精度;

- 高速、高精度需要更高的功耗和更大的面积,系统的架构也越发复杂,进一步导致功耗和面积的增大;

- 流水线式的固有数据延迟特点使得其无法实时输出当前量化结构,使其无法朝向更高速的应用场景发展;

高速Pipeline ADC发展趋势:

- 低功耗:功耗是限制传统Pipeline ADC发展的瓶颈问题,降低功耗也是研制高速、高精度Pipeline ADC的重要方向;

- 混合结构:为实现兼容高速、高精度、低功耗的特点,往往采用了混合结构实现,例如Pipeline+SAR可以实现低功耗和中高精度;Pipeline+ Δ-Σ ,可以实现高精度;

4.SAR

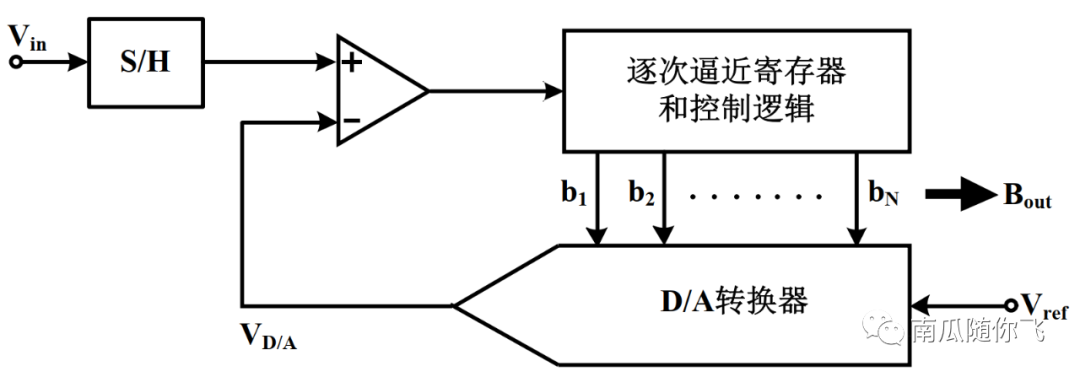

Successive-approximation Register,SAR,逐次逼近式ADC。传统架构的SAR式时间同步取样,主要优势低功耗、结构简单、低中高精度均有,能够应用在工业控制、生物电子、便携设备中。

由采样+保持电路、逐次逼近寄存器、控制逻辑、DAC构成。举个列子来说明其工作流程和原理。

由采样+保持电路、逐次逼近寄存器、控制逻辑、DAC构成。举个列子来说明其工作流程和原理。

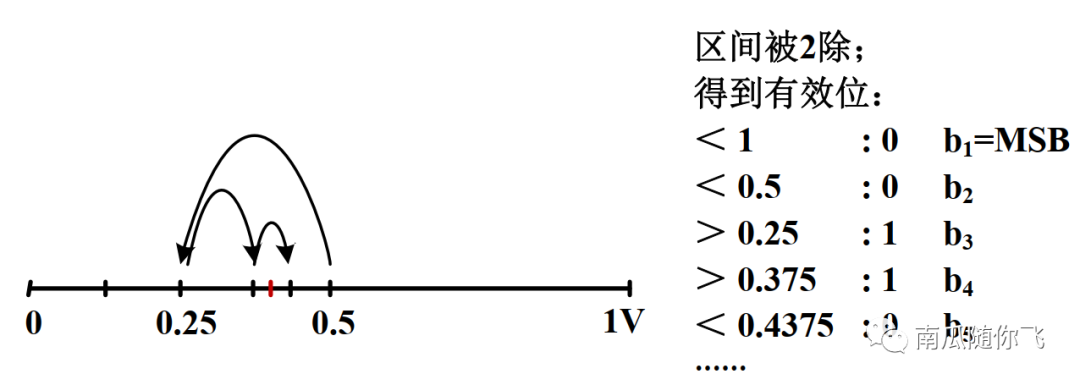

假设输入电压是0.4V(参考电压为1V)。

1)第一次比较,0.4V <1V,最高有效位为0;

2)二分区间,输入电压与<0.5V 相比较,再次产生一个0;

3)二分区间,输入电压>0.25V 相比较,有效位为1;

4)1作为控制信号,将比较值从0.25V 选为0.375V,而不是0.125V;

5)比较程序继续N 次,得到N 位输出。

主要缺点:

- 逐次逼近是串行结构,使得其无法实现高速采样;

- 同步时钟电路控制,模块之间传递信号存在较多等待;

- 基于分频的时钟控制,外部时钟频率要高于内部采样时钟N+1倍或以上;

采用异步时钟的结构能够有效解决其关键问题:外部时钟无需N+1倍于内部采样时钟,降低了对外部时钟速度和精度的要求,简化了电路设计;异步时钟下电路模块在传递信号的时候没有等待问题,时间延迟小。因此异步时钟的SAR ADC是目前SAR ADC的主流解决方案。

5.Δ-Σ

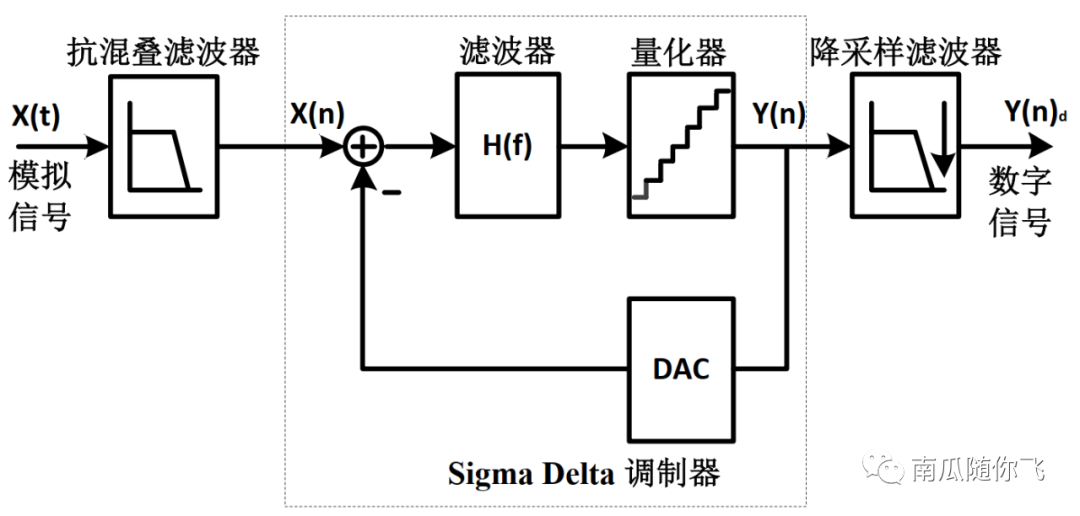

Δ-Σ ,增量累加ADC。与其他几种ADC不同,这一类ADC成为过采样ADC,其采样率远大于2倍信号最高频率,根据应用场合的不同范围从20-1000。其他结构如下图所示。

信号的采样率越高,噪声对信号信息的影响就越小,SNR也随着过采样率的提高而提高,因此ADC的分辨率也会提高。Δ-Σ 就是通过速度来换取高分辨的一种架构。其采样进度能够达到24bit。

6. Time-interleaved

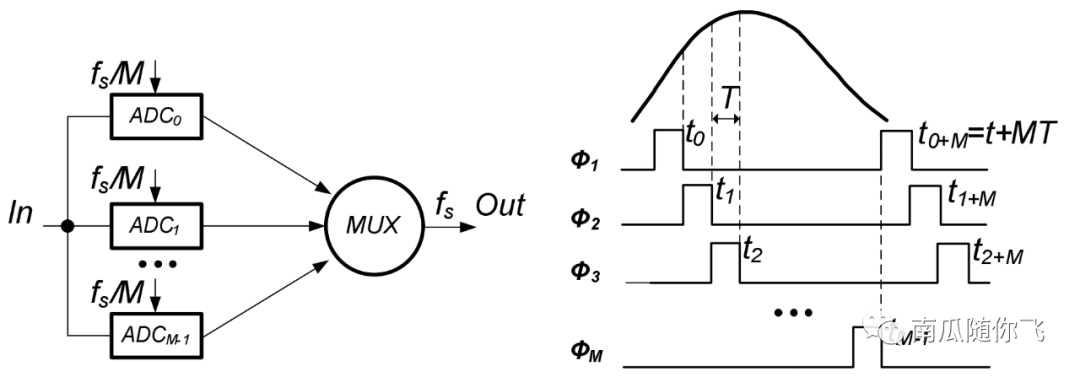

Time-interleaved,时间交织ADC。时间交织的核心思想是两点:多路处理+时钟交织。其结构如下图所示。M个采样率为fs/M的ADC阶梯式并行采样。在第一个采样时钟信号到达的时候把第一个采样值传递个ADC0,第二个时钟周期来到的时候把第二个采样值传递给ADC1,这样类推。

Time-interleaved ADC是目前实现多通道ADC采样的方案,是实现高速ADC的重要方案。但是面临由多通道导致的失配、面积功耗大、多项为时钟、输入信号、参考电压的生成和分配困难等问题。

-

设计带ADC电路时,如何用模拟地与数字地进行分割来减少数字地对模拟地的影响?2024-12-03 547

-

adc是什么意思 adc在电子电路中的应用2024-10-31 14642

-

远场应用中的模拟麦克风和ADC系统2024-08-28 355

-

模拟电路中的失真是什么意思?模拟电路中都有哪些失真?2023-10-18 7853

-

ADC模拟电路皇冠上的明珠(1)2023-07-03 5866

-

终于搞懂模拟电路中的ADC!12023-02-20 21022

-

如何在MSP430G2中使用ADC使用Energia IDE读取模拟电压2022-11-16 3758

-

实用模拟电路设计技术Section4高速采样ADC2022-08-01 562

-

ADC数字地和模拟地的接地原理2022-05-10 5084

-

如何使用LTspice模拟 SAR ADC 模拟输入?2022-04-12 52364

-

模拟量模块K2-04ADC和K2-02DAC技术资料2017-09-22 1405

-

ADC外围电路设计方法2012-03-15 10063

-

ADC外围电路的设计2011-02-11 5330

全部0条评论

快来发表一下你的评论吧 !