探讨一些关于ADC技术层面的问题(上)

模拟技术

描述

上一篇文章中对ADC的概况进行了简单的介绍,这篇内容主要针对ADC的一些技术方面的问题做探讨。

一、28nm工艺下的ADC

随着无线通信向高速、宽带方向发展,对于无线信号接收机提出了越来越高的要求。特别是在电子战领域、信号情报侦察应用方向对于高带宽、小型化、轻型化以及低功率(Size, Weight and Power: SWaP)ADC的需求更加迫切。

65nm制程的ADC在向更高速的、高带宽的数据变换器扩展的时候遇到了一些固有的障碍:工艺制程、带宽限制等方面。28nm的先进工艺制程正在打破这个界限,从而使得原本一些无法考虑实现的接收机的架构或者性能得到很大的促进。接下来我们就从几个角度来看看28nm的ADC具有哪些应用的优势。

在宽带的雷达电子战领域中,系统的研发人员在设计高性能、低SWaP的接收机的时候会面临很多挑战。在接收机中ADC扮演了一个非常重要的角色,以至于有时候会因为ADC的性能而采用不同的接收机架构。

ADC的性能参数包括了采样率、带宽、分辨率,都会影响射频RF链路以及后端的DSP。高采样率和带宽能够一次性捕捉分析宽带的RF信号,同时降低扫描时间、保持更高分辨率,能够提高分析的性能,降低虚警概率。

28nm的晶体管能够降低寄生的栅极电容,实现更快的开关速度,同时仅需要很低的功率来驱动即可。28nm的工艺不仅能够提高单个晶体管的性能,同时能够在单位面积上集成更多的晶体管以获得更优异的信号处理能力。28nm工艺下实现的高采样率ADC在电子战方向中的信号情报侦察、电子战防御(Electronic Protect:EP)、电子战支援(ElectronicSupport:ES)应用需求十分迫切。

采用28nm的工艺,同时也带给了半导体厂商更多的设计思路。能够在ADC中集成更多的混合信号处理单元以保证在同等的SWaP条件下提高ADC的性能。

例如NCO(Numerically Controlled Oscillators:数控振荡器,其作用类似于本振源,提供一个混频信号)和DDC(Digital Downconverters:数字下变频器,其作用是将高频信号在数字域进行下变频,降低频率以便于后续处理)。

在提高了采样率和带宽之后面临着有大量的数据吞吐(GSPS),在研发过程中就需要找到能够与之相匹配的数据接口传输数据。目前市场上很多28nm的ADC数据输出速率已经超过了10Gbps,采用的接口通常为JESD204B,但是引入由串行和解串路由Gbps带来的JESD相关电路布局、信号完整性分析方面的问题,进一步提升设计研发的难度。

可以通过集成NCO、DDC实现降采样,变换到基带,结合数字滤波能够保持很高速的数据输出速率。所以集成NCO、DDC以实现降采样是保持高速数据的有效方法。

另外一方面,如果JESD204B输出的数据没有经过降采样,一直维持在非常高速的传输下,所需要的功率、产生的功耗将会非常大。因此,采用抽取滤波的方式能够降低功耗。

总的来说,在电子战领域对于集成了NCO、DDC的高速的、高带宽、高分辨率的ADC的应用能够极大的提升接收机的性能,先进工艺制程的ADC能够有效的解决低SWaP与高速数据之间的矛盾关系,为实现高性能的接收机提供了有效的解决方案。

二、ADC芯片的工艺方案

在ADC方向上,CMOS工艺已经成为一种主流的工艺实现方式。CMOS工艺具有较低的寄生电容、电感以及电阻效应,是Δ-Σ、SAR以及Pipeline架构(基于开关电容型的电路)的ADC的主要实现工艺。

BiCMOS的工艺成本较高,在一些性能要求较高的模拟前端需要使用。例如混频器、采样保持电路、输入放大器以及高精度参考电压都利用双极型实现的,其他的功能电路利用CMOS实现。

GaAs在ADC方面的应用主要在6-8bit,采样率大于1G的flash架构中使用。这一类的ADC通常成本、功率都比较高,但是市场较为小。

三、ADC对接收机系统架构的影响

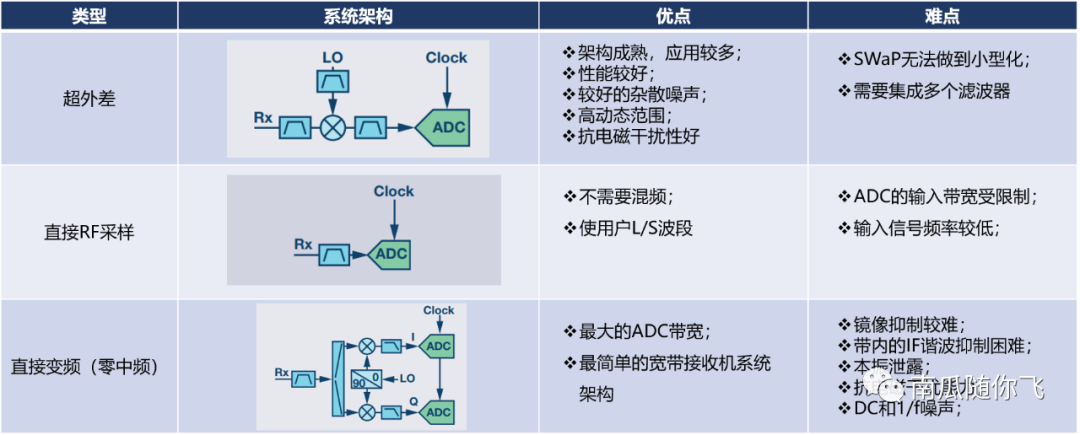

接收机按照不同的RF信号变频处理方式可以分为三种:超外差式、直接RF采样、直接下变频(零中频)。

1.超外差接收机

RF信号通过与本振信号混频后变到中频IF,在进行后入处理。超外差式接收机应用的时间早、架构较为成熟、性能表现稳定。通常会采用较高的IF频率结合滤波器来抑制镜像频率干扰,或者通过多级下变频器逐级变频实现镜频抑制。

同架构图中可以看出来,超外差接收机的架构较为复杂。通常需要很大的驱动功率以及电路布局才能够获得较合适的工作带宽,与现在系统对低SWaP的需求相违背。

2. 超外差接收机

直接RF采样是市场和研发人员一直在追求的接收机架构。目前主要的障碍在直接射频采样的速度、大输入带宽与ADC的速率之间不匹配的问题。这也是限制这类架构向更高频段发展的重要原因。

目前主要应用还是集中在较高的奈奎斯特频段(采样率与信号频率之间的关系)的L/S波段的接收机中。下一步随着ADC的发展,将会逐步向C-band,X-band扩展。

3. 零中频

零中频是对数据变换带宽利用效率最高的架构。ADC通常工作在第一奈奎斯特采样区间。信号通过与正交的本振信号混频过后形成两路I/Q正交信号,然后分别进行ADC。

主要的难点在于保持较好的I/Q信号的平衡,以获得较好的镜像抑制、本振泄露以及直流偏移等。目前通过集成整个零中频信号链路并结合数字校准技术已经解决了这些问题,进一步打开了该类型接收机的应用市场,在多种应用场合已经逐步采用这种类型的接收机。

以超外差结构为例,介绍ADC对其架构的影响。通常在低速的ADC时代,因为工作带宽与输入频率的比例很大,使得通过单级下变频直接做低频滤波较为困难,很多微波接收机通常都是采用多级变频的模式。

图片来源:ADI官网

随着ADC的采样率、输入带宽的提高,使得单级变频架构逐步进入应用。典型的框架如下图所示:

图片来源:ADI官网

接收链路最开始是一个低噪放,但是在有些特定的应用领域,例如面对大功率电子对抗设备会在前端加载一个限幅器降低输入功率的幅度。随后经过带通滤波、放大、低通滤波、下变频、低通滤波、放大,在进入ADC之前需要做一个抗混叠滤波,滤除掉一些干扰、杂散以及谐波信号。信号进入ADC进行数据变换,后续的电路都是围绕着ADC进行设计的。

有没有必要在每一种接收机或者设备中都采用高速、高精度的ADC?这是需要结合具体的应用场景来讨论的。当面对的是宽带、高速的信号,典型的就是电子电子对抗、大数据量通信、频谱测试测量等,高速的ADC就显得必不可少。

从系统架构方面来看,能够有效降低系统复杂程度;从性能方面来说,能够提高高吞吐量的数据采集变换。同时结合不同的接收机架构,在面对射频直采和零中频的应用,高性能的ADC的需求更加迫切,大带宽、高采样率等特点有助于研发人员采用紧凑的系统架构;

超外差结构中,高性能的ADC也能够在一定程度上降低系统的复杂程度,但是如果需要考虑到性价比、成本方面的问题,如果能够采用成本较低的多级变频的方案+性能适合的ADC来实现也是一种方案。

综上,考虑到架构性价比、成本、性能优势以及复杂程度,虽然不是每一种接收机架构都需要用到高速、高分辨率的ADC,但是高速的ADC能够极大的降低接收机的架构复杂度、提高性能,这也正式复合了系统朝着低SWaP方向发展的技术和应用趋势。

-

一些技术报告2016-01-25 2814

-

时钟软件层面和硬件层面的问题解释2021-11-29 1116

-

嵌入式一些日常小技巧分享2021-12-21 1573

-

硬件层面的堆和栈基本介绍2022-03-01 1323

-

关于电池的一些疑问解答2009-11-13 817

-

关于PCB 生产过程中铜面防氧化的一些探讨2009-11-17 4351

-

关于红外通信的一些问题知识点2016-05-05 1070

-

LTE的其它一些关键技术介绍2016-06-27 460

-

关于PID一些常用知识2016-08-29 934

-

关于信息治理与云的一些事实2016-12-28 586

-

usb通信的一些基础知识2019-05-18 4987

-

分享一些比较全面的手机原理资料2021-11-05 928

-

SiC技术优点、缺点及应用层面的一些瓶颈2022-05-09 1153

-

探讨一些关于ADC技术层面的问题(下)2023-02-20 2631

-

关于数码管的一些知识笔记2023-06-28 6545

全部0条评论

快来发表一下你的评论吧 !