探讨一些关于ADC技术层面的问题(下)

模拟技术

描述

四、ADC中的NCO和DDC如何工作的

首先我们先来回答几个问题。

- 为什么要做降采样?

降采样,顾名思义,降低采样率。为什么要做降采样,那是因为之前用了采样率过高的ADC。那为啥不直接用低采样率的ADC就可以了吗?

用高速的ADC,个人觉得主要原因如下:

第一、因为接收和采集的信号是宽带、高速的信号,需要采集的信号往往是一些宽带的信号,必要时候还需要在一个很宽的频段内进行扫频。所以为了实现匹配,采用高速的ADC是必备的。

第二、可以降低对射频前端模拟滤波器的要求。滤波器的设计难点在于尽量需要一个很好的矩形系数,又希望只采用几阶就能够实现,这之间就存在trade-off的设计。

模拟滤波器通带越窄、带外衰减越陡峭、衰减越大,需要的滤波器阶数就越多,滤波器的设计成本就越高,有时甚至无法研制出来。所以采用宽带的滤波器结合逐级滤波,进来的信号量也就很大,就需要用到高速的ADC了。

为什么又需要再后面降低采样率呢?主要是因为ADC过后,需要将数据传输到后续的DSP、FPGA等基带数字信号处理电路进行分析处理,这中间存在一个速率匹配的问题。

高速的ADC不经过降采样出来的信号速率通常很高,DSP的时钟速率是无法跟上的,所以需要经过降采样处理。第二,ADC的数据输出接口如果一直保持在很高的数据传输速率下,其需要驱动的功率就很高,功耗也提高,芯片的功耗、散热是一个非常大的问题。

- 为什么是先滤波、再降采样而不是先降采样再滤波?

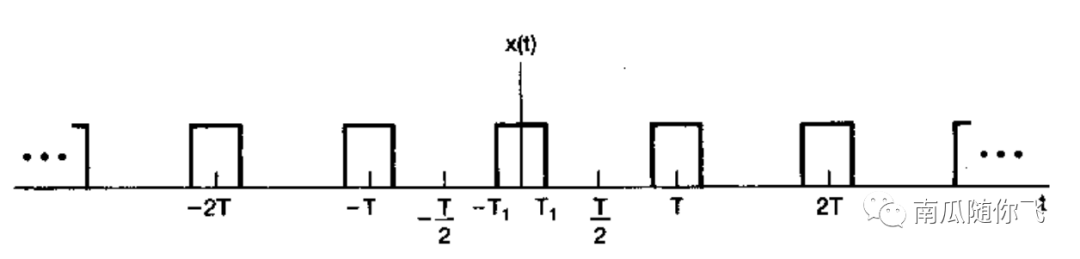

在信号与系统中表述过,时域离散对应频域周期、时域连续对应频域离散。(信号与系统第三章和第四章)。直观的就是时域上的周期方波通过傅里叶变换成为了频域上的Sinc函数,如下图。

图片来源:《信号与系统》

假设,输入信号如下左边是时域,右边是频域:

图片来源:《信号与系统》

经过ADC采样之后,时域和频域分别变成如下,时域离散对应频域周期。

图片来源:《信号与系统》

降采样过程实际上是在对AD采样之后的数据进行抽取滤波,即是间隔一定的数量进行抽过去采样,如下图所示左所示。这个过程可以看作是对已经在频域上周期了的信号又做了一次周期,结果如下图右边所示。此时的信号在频域上面已经发生了混叠。

所以,需要在采样之后滤波,然后再进行降采样,就可以得到没有混叠的信号。

回到NCO和DDC。NCO:Numerical ControlOscillator,数控振荡器,集成在DDC中,用于为输入信号分成I/Q信号提供本振混频。

DDC:Digital Downconverters,数字下变频器,进行降采样工作。

图片来源:ADI官网

信号经过采样之后进入DDC,首先通过NCO,与NCO提供的两路相位相差90°的信号进行混频,从一个较高频率变换到较低频率;然后通过滤波器进行抽过去滤波;接着选择性的是否进行一个放大;最后输出两路I/Q信号。

图片来源:ADI官网

DDC中的滤波器一般来说采用级联方式首先的,分为三级,按照顺序分别是梳状滤波器(CIC),第二级半带滤波器(HBF),第三级有限冲激响应滤波器(FIR)。

CIC是一种不需要进行乘除法运算的滤波器,只需要加减法和移位运算就可以。乘法运算是一种非常耗费资源的运算,因为实际上在数字计算中本质上是没有乘法运算的,还是通过加减法结合移位运算进行的。

乘法运算实质上是一堆加减法+移位运算的集合。在提出CIC之前都是直接用乘法运算进行一级滤波的,成本很高,同时运算速率有限。采用了CIC能够很好的将高频速率降低,同时修复带内平坦度,为后面两级滤波设计降低了难度。

HBF作为第二级滤波器,运算量是FIR的一半。

FIR低通滤波器,它的作用是对经过抽取滤波后的波形进行整形,因为经过抽取滤波之后,仍然会有一部分波形处于有效频带之外,故需要低通滤波器将这部分带外波形除去,剩下带内的信号提供给后端的 DSP 处理。

参考文献:

- 信号处理机中的数字下变频技术研究;

- 数字下变频芯片的前端设计;

- 数字下变频技术及其FPGA实现;

- 《Data Conversion Handbook》;

- 《信号与系统》;

-

自己收集的一些关于手机摄像头方面的资料,分享下!2013-10-03 13741

-

一些技术报告2016-01-25 2766

-

时钟软件层面和硬件层面的问题解释2021-11-29 1047

-

嵌入式一些日常小技巧分享2021-12-21 1500

-

关于电池的一些疑问解答2009-11-13 749

-

关于PCB 生产过程中铜面防氧化的一些探讨2009-11-17 4295

-

关于红外通信的一些问题知识点2016-05-05 1015

-

LTE的其它一些关键技术介绍2016-06-27 431

-

关于PID一些常用知识2016-08-29 891

-

关于信息治理与云的一些事实2016-12-28 555

-

usb通信的一些基础知识2019-05-18 4822

-

分享一些比较全面的手机原理资料2021-11-05 812

-

SiC技术优点、缺点及应用层面的一些瓶颈2022-05-09 1078

-

探讨一些关于ADC技术层面的问题(上)2023-02-20 2282

-

关于数码管的一些知识笔记2023-06-28 5504

全部0条评论

快来发表一下你的评论吧 !