分析一个电路因WPE效应挂掉的案例

模拟技术

描述

今天分享一个后仿真发现电路fail掉的一个案例。

首先简单介绍一下什么是WPE效应。

工艺中,有一些物理效应,这些物理效应在以前的老工艺中,比如180nm之前,影响基本可以忽略不计,因此老工艺设计中不会去关心这些效应。但是随着工艺的先进,这些物理效应造成的器件性能的影响占比越来越大,不可忽略,以至于导致芯片fail。foundry会在PDK中将这些物理效应建模进去,但是designer和layouter在设计电路的时候,也要考虑这些效应,以保证电路可靠性。

这些物理效应包括:

WPE: Well Proximity Effect阱临近效应

LOD: Length of Diffusion扩散区长度效应

OSE: OD Space Effect扩散区/有源区间距效应

PSE: Poly Space Effect栅间距效应

其中,WPE效应就是阱临近效应,指器件靠近阱(Well)引起的参数发生偏离,从而影响器件的性能。在普通的单阱工艺中,只有PMOS有此效应;在双阱工艺中,PMOS和NMOS都有此效应。

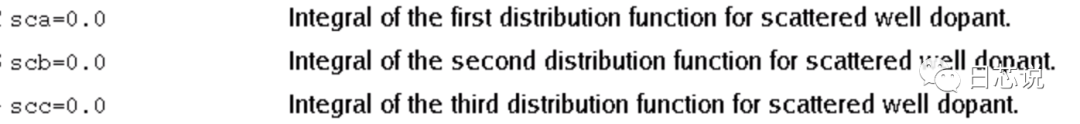

WPE参数主要有三个:SCA、SCB、SCC。这三个参数在BSIM4模型中的定义如下:

看似很难懂,其实也不用过多care这些参数的具体含义,简单说,就是WPE的这三个参数很重要,在前仿真和后仿真不应该差别过大,否则会引起MOS的电流、Vth等参数产生很大影响,继而影响电路整体功能。

该案例主要说明版图中TG layer对WPE参数的影响(TG是tripple Gate,主要标识高压device,栅氧化层更厚)。

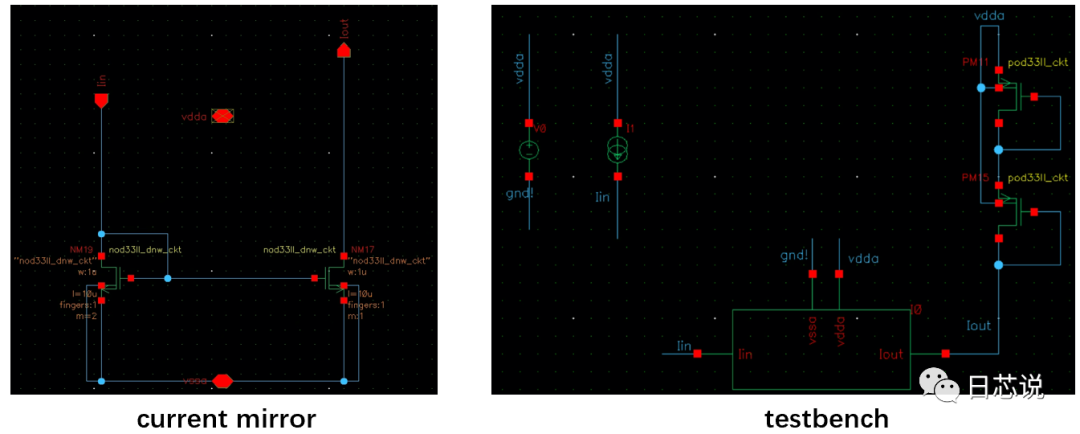

以一个简单的电流镜为例,说明layout改变WPE参数对输出电流Iout的影响。testbench中输入电流Iin给定20nA,电流镜是2:1的copy rate。两个MOS的W/L=1u/10u.理论上Iout为10nA。

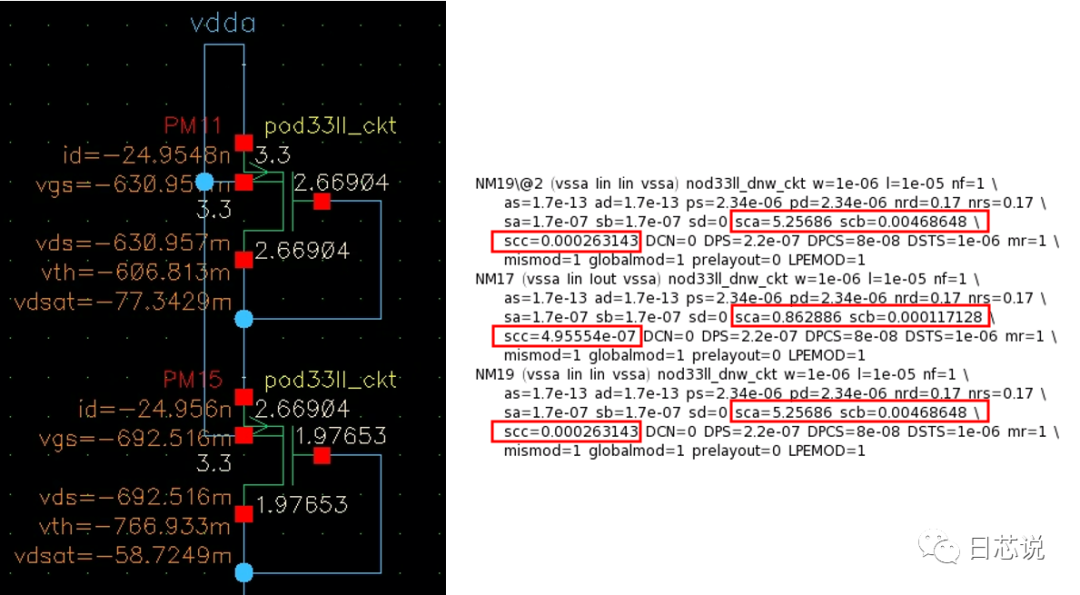

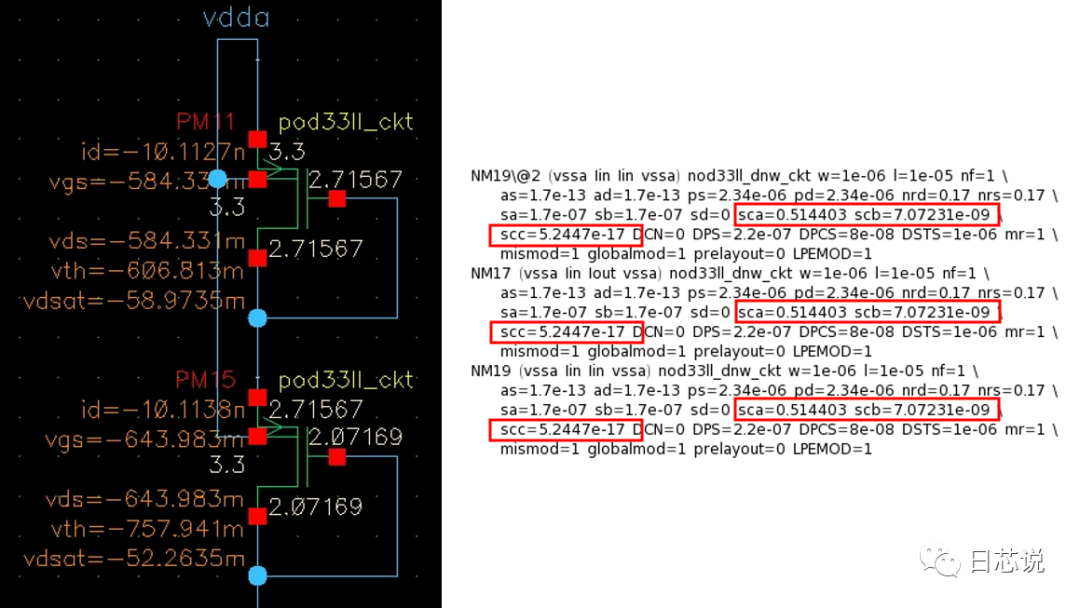

电路图中两个MOS的WPE参数,网表显示均如下图右图所示,前仿真结果如左图,输出电流Iout大小为10nA,无问题。

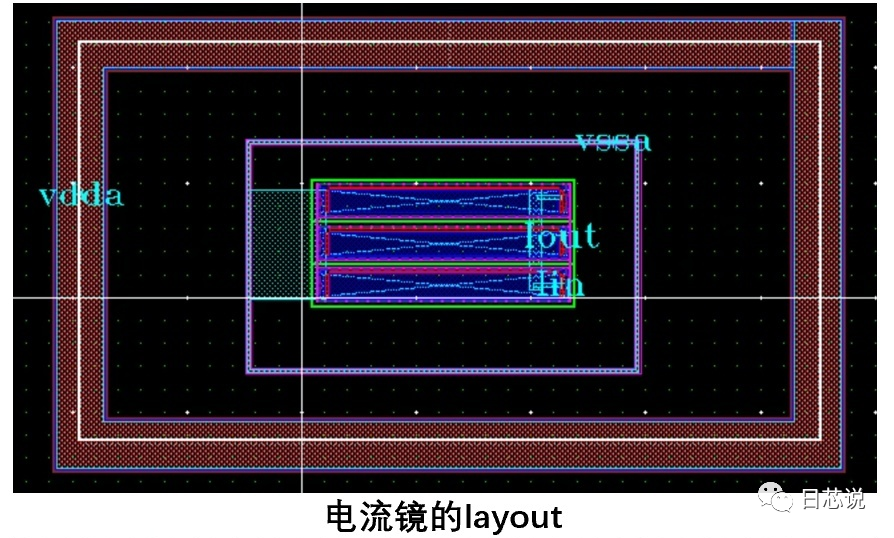

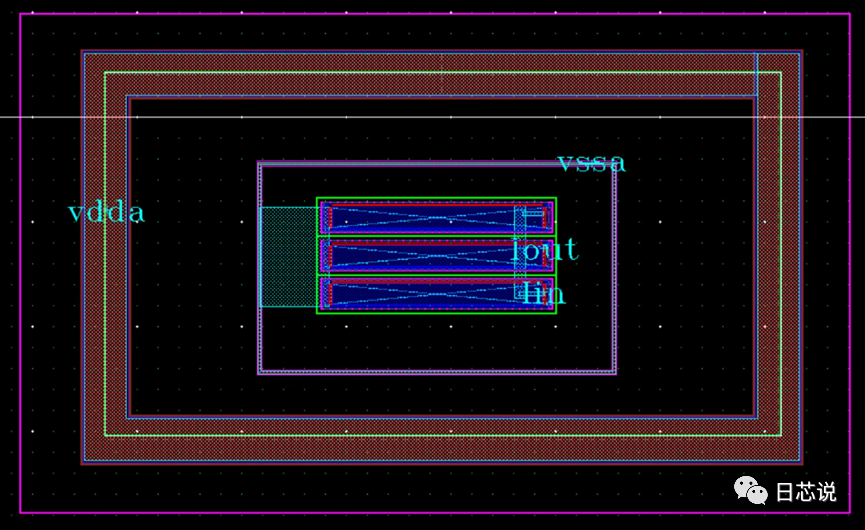

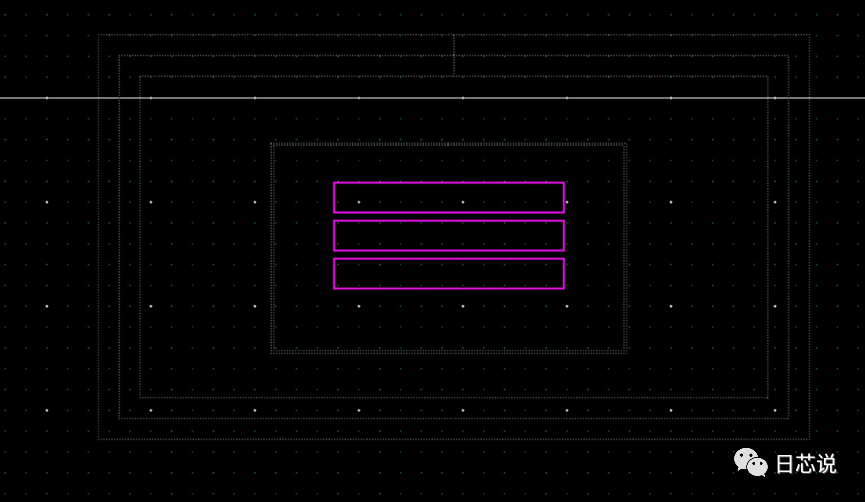

其layout如下所示:

(注意DNW device的画法,此版图不专业,只是为了说明问题,同时也不会引入问题,未加dummy,已验证dummy对此电流镜的WPE参数无影响)。

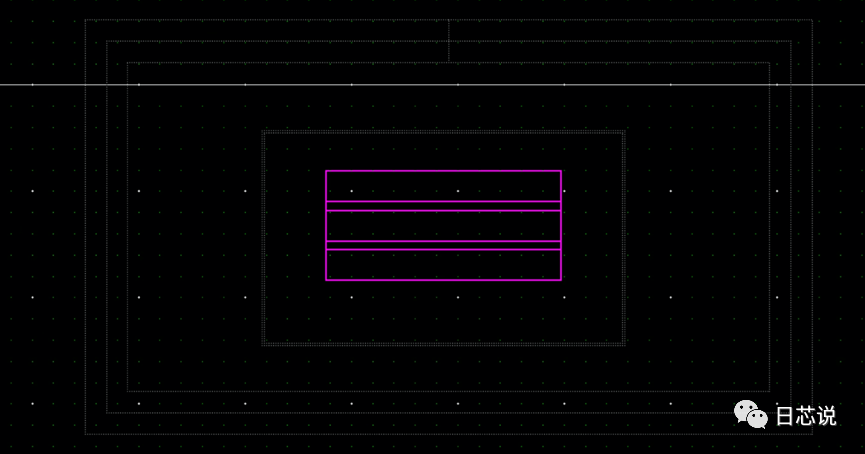

只显示TG layer的情况:

现在将相同电压域的管子用一篇TG铺满,但都是贴着原有TG层的边去铺,如上图所示,不会留出裕度,如果是用的180nm,这样铺也没啥问题,如果是40nm,这样就出现问题了。

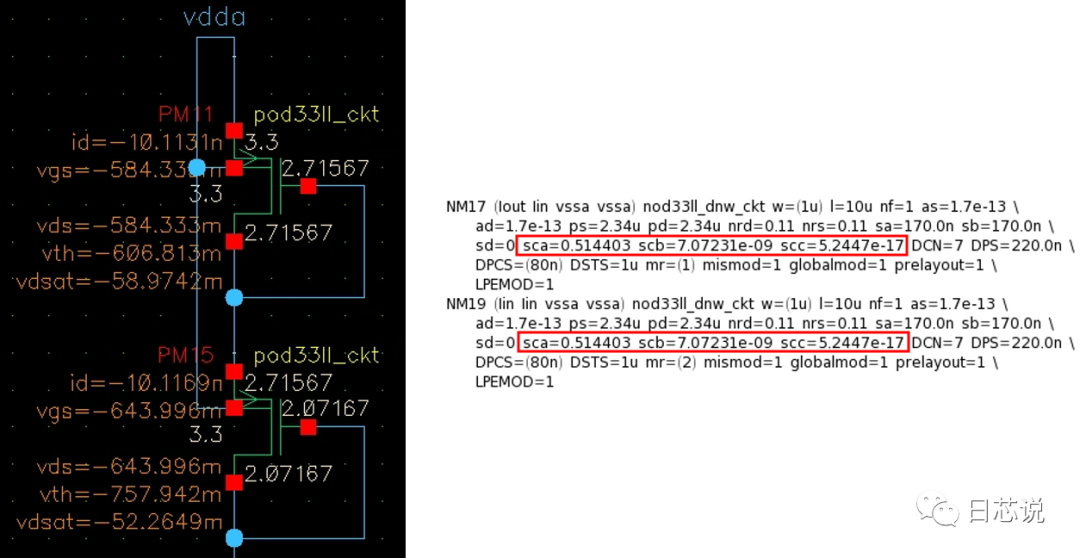

对此layout进行寄生参数提取,在calibre进行norc的提取就可以发现此画法的问题了。用此layout生成的calibreview进行仿真,结果如下。输出电流Iout不再是10nA,而是24.9nA,显然不正常。再看网表,发现WPE参数中sca、scb、scc参数和前仿真的差异很大,导致Iout不正常了。电流本来是10nA,现在接近25nA,变大到原来的2.5倍,如果此电流流过电阻,且后续电路是小摆幅设计,那么电流的变大会时后续电路无法正常工作。

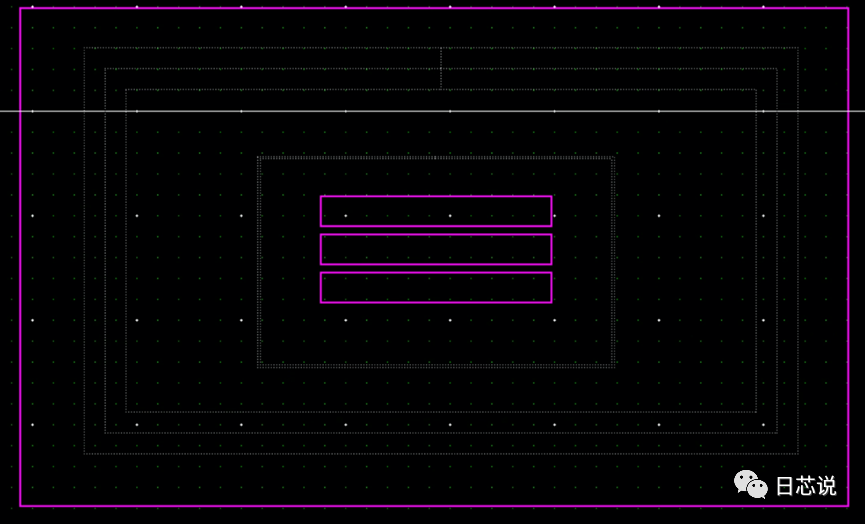

现做改动,将TG层铺满的面积变大,如下图:

再对此layout进行norc后仿真,提取出的calibreview进行仿真,结果如下。网表中,WPE参数和前仿真一样,输出电流变为正常,为10nA。

再次做改动,将自己铺设的TG层删除,只保留库里的器件原本的TG层,可看出三个MOS之间TG有间距。

对此layout进行norc提取,提取出的calibreview进行仿真,结果如下,可发现,网表中的WPE参数变得更大了,与前仿真的WPE参数差别很大,但是输出电流是正常的,是10nA,这个现象就奇怪了,WPE参数偏离前仿真这么多,输出结果竟是正确的。

以上几种layout画法都不会报DRC错误,总结经验就是,TG layer应该流出几um的裕度包围MOSFET的有源区,这样更保险。(有经验的layouter应该深懂这一点,designer也应该提醒和你对接的layouter这些注意的地方)。

至于TG是如何影响WPE参数的(应该是TG影响了阱的掺杂浓度),WPE参数又是如何影响MOS的电流的(现在看来不是正比关系)研究透彻了再分享一下,有知道的同学也可以留言呀。

-

白日梦想ll

01-27

0 回复 举报请问这个问题博主后续有研究吗,我目前也发现了这个情况,在umc40nm工艺下,TG_25层对WPE参数的影响很大,我单独调整阱的大小却没有看到明显的参数变化,目前还想不清楚TG这层怎么影响阱的浓度的 收起回复

白日梦想ll

01-27

0 回复 举报请问这个问题博主后续有研究吗,我目前也发现了这个情况,在umc40nm工艺下,TG_25层对WPE参数的影响很大,我单独调整阱的大小却没有看到明显的参数变化,目前还想不清楚TG这层怎么影响阱的浓度的 收起回复

-

WPE效应的概念 如何让减小WPE效应呢?2023-11-03 9936

-

电路耦合效应分析 耦合性高好还是低好2023-09-22 6790

-

一个由RC电路和P沟道场效应管组成的延时关机电路分析2023-08-14 2927

-

一个超简单的单片机供电电路分析2023-04-26 2475

-

mwifi无router,一旦root挂掉,系统瘫痪怎么解决?2023-03-10 513

-

请教tmos任务挂掉的原因有哪些?从哪方面查?2022-07-29 788

-

示波器探头的负载效应的检测和分析2021-10-19 2072

-

怎么设置mos管的WPE Proximity Effect?2021-06-24 2537

-

石墨烯电路芯片的热效应研究分析2021-06-10 1405

-

一款带有DDR1的电路板,系统挂掉了,怎么回事资料下载2021-04-11 1079

-

寄生电路的效应:Latch-Up(锁定)2018-08-23 6087

-

场效应管驱动电路分析2016-01-09 5875

-

场效应晶体管放大电路的动态分析2010-09-25 988

-

高速电路传输线效应分析与处理2009-11-17 1056

全部0条评论

快来发表一下你的评论吧 !